Por Matías Guala (@matias_guala)

Hubo un tiempo en el que la tecnología no llegaba en cajas minimalistas ni se actualizaba sola durante la noche.

Llegaba envuelta en papel de regalo.

A veces mal envuelta.

A veces con el moño torcido.

Pero llegaba.

Hubo un tiempo en el que la tecnología no llegaba en cajas minimalistas ni se actualizaba sola durante la noche.

Llegaba envuelta en papel de regalo.

A veces mal envuelta.

A veces con el moño torcido.

Pero llegaba.

Cuando el fracaso es el camino al éxito

Cincuenta máquinas por el balcón. El día que Burroughs perdió la paciencia

¡Leé la primera parte por ACÁ!

Imaginemos la escena: San Luis, Missouri, 1885. William Seward Burroughs, un emprendedor nato, observa con frustración creciente las cincuenta máquinas sumadoras que había construido con tanto esfuerzo. Las había diseñado, supervisado su manufactura, probado una y otra vez con gran éxito, y funcionaban a la perfección.

Pero había un problema: solo funcionaban correctamente cuando él las manejaba (debido a que la velocidad de tipeo influía en el resultado).

Por Roberto Trillo (Facebook: Sumando A Manija)

Hubo un tiempo en el que FIFA no era solo fútbol. Era una historia.

No una historia de marketing ni de estadísticas.

Era una historia de personas, de vínculos rotos, de decisiones incómodas y de segundas oportunidades.

Una historia imperfecta, limitada, pero profundamente humana.

Esa historia se llamó The Journey.

Por Matías Guala (@matias_guala)

Continuar leyendo “De FIFA a FC: cuando el camino importaba más que el resultado”Hay juegos que uno espera.

Hay juegos que uno persigue.

Y después está GTA IV, ese que aparece cuando tu vida ya no es la misma que cuando jugabas de madrugada con unos auriculares rotos… pero todavía necesitás que un juego te diga algo.

Porque GTA IV no te abraza:

te confronta.

Te exige.

Te hace mirar cosas que las versiones más jóvenes de nosotros apenas entendían.

Y ahí, cuando Liberty City se abre entre la neblina, te agarra algo en el pecho.

Ese recuerdo de cuando los videojuegos no eran servicios, temporadas, cosméticos ni “pay to win”.

Eran historias.

Eran sensaciones.

Eran refugios.

Por Matías Guala (@matias_guala)

Continuar leyendo “GTA IV: la oveja negra de Rockstar”Hay juegos que uno busca. Y hay juegos que te encuentran. ARC Raiders me encontró así: un viernes a la tarde, con ganas de desconectar. Le escribo a un amigo y me dice:

—Mati, ¿lo tenés? Está buenísimo para jugar en equipo.

Yo, gamer +40, ya sé cómo funciona esto: te tentás, te ilusionás, sacás la tarjeta… y después te arrepentís cuando llega el resumen. Pero igual lo hice, porque hay impulsos que a cierta edad ya aprendimos a no resistir.

Y así entré a un género que jamás había tocado: un extraction shooter. Sin armas. Sin experiencia. Sin reflejos competitivos. Sin saber ni cómo abrir el inventario.

Ahí empezó algo que —te juro— no esperaba sentir en 2025:

un juego online que habla bien de la gente.

Por Matías Guala (@matias_guala)

Continuar leyendo “ARC Raiders: un faro para gamers que todavía creen en lo colectivo”Hay preguntas que parecen simples, pero esconden bastante más de lo que dicen. Y una de ellas es esta: ¿por qué jugamos retro?

¿Por qué, teniendo miles de títulos nuevos, mundos inmensos, gráficos que parecen cine y consolas que hacen magia, seguimos volviendo —una y otra vez— a juegos de hace 20, 30 o 40 años?

La respuesta fácil sería: nostalgia.

Pero la nostalgia no explica todo.

Por Matías Guala (@matias_guala)

Hubo un tiempo —no tan lejano, apenas una década atrás— en que las revistas de moda eran el villano más fácil de señalar.

Por Matías Guala (@matias_guala)

El dedo acusador apuntaba a esas portadas donde las modelos parecían de otro planeta: pieles sin poros, cinturas imposibles, sonrisas congeladas.

La palabra Photoshop se volvió sinónimo de trampa, de mentira visual.

“Todo retocado”, decíamos, con una mezcla de burla y alivio.

Nos reíamos de las celebridades que necesitaban un diseñador para parecer bellas. Nosotros, los mortales, aún conservábamos el consuelo de la autenticidad. Pero el tiempo, como siempre, tuvo otros planes. Acompañame en este viaje.

Por cierto, por acá podés escuchar la versión podcast de la nota:

Allá por 1991/1992 aproximadamente, y yo siendo bastante chico, llegó a mis manos gracias a mi padre un Froggy Junior, que para otros con acceso a las novedades del exterior era una reliquia de los 70s/80s, pero para mi un antes y un después en mi relación con los videojuegos.

La Froggy Junior era conocida como una consola de videojuegos clon de Atari 2600 Jr importada por -BTE Electronics S.A.- desde Taiwán para el mercado argentino. (Consolas como esta misma las pueden ver en el Museo de Informática Espacio TEC)

Continuar leyendo “Arqueología una Froggy Junior (clon de Atari 2600) de Argentina de los 90s”Hay sagas que se vuelven parte de uno. Que dejan de ser simplemente videojuegos para transformarse en capítulos de una historia personal, en compañía silenciosa durante madrugadas largas o en esas tardes donde la nostalgia se mezcla con el olor del mate.

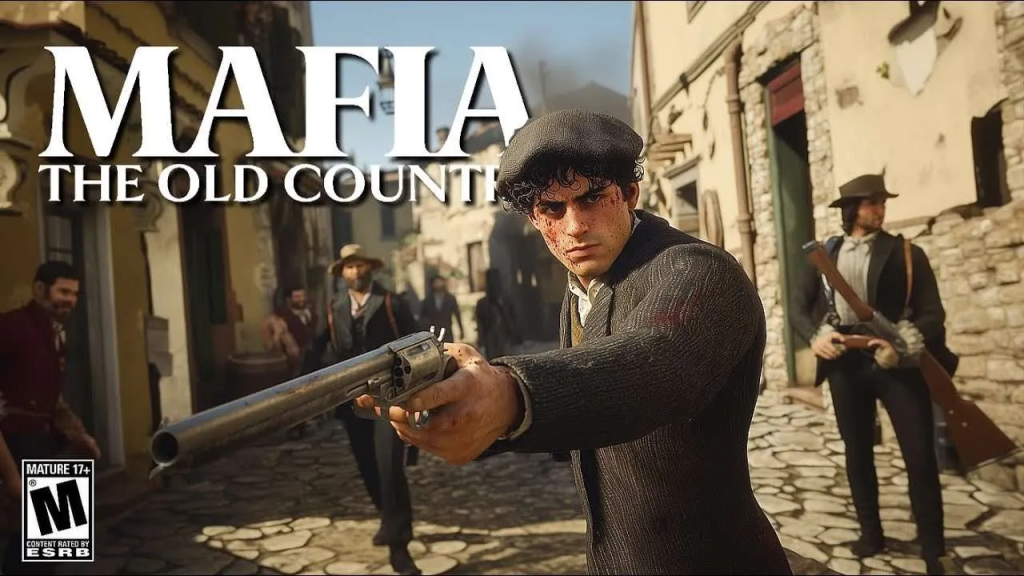

Mafia siempre fue una de esas sagas. Y con Mafia: Old Country, 2K Games acaba de recordarnos que los buenos relatos —los verdaderos— no mueren: se reinventan.

Por Matías Guala (@matias_guala)

“Yo aprendí prompt engineering jugando Monkey Island”

Por Francisco Morell (jupiter_tonante)

A veces pienso que todo empezó cuando tenía doce años, frente a una pantalla fosforescente que parpadeaba más que razonaba. No había conexión a Internet, pero sí una más profunda: la que se establece entre el jugador y un mundo hecho de comandos, verbos y objetos imposibles. “Usar pollo de goma con polea en cable”.

Esa línea, escrita con la solemnidad de quien invoca un hechizo, me abrió la puerta a una lógica que hoy reconozco como mi primer prompt engineering practice.