A continuación les dejo los links a los artículos anteriores de la serie

Categoría: C64

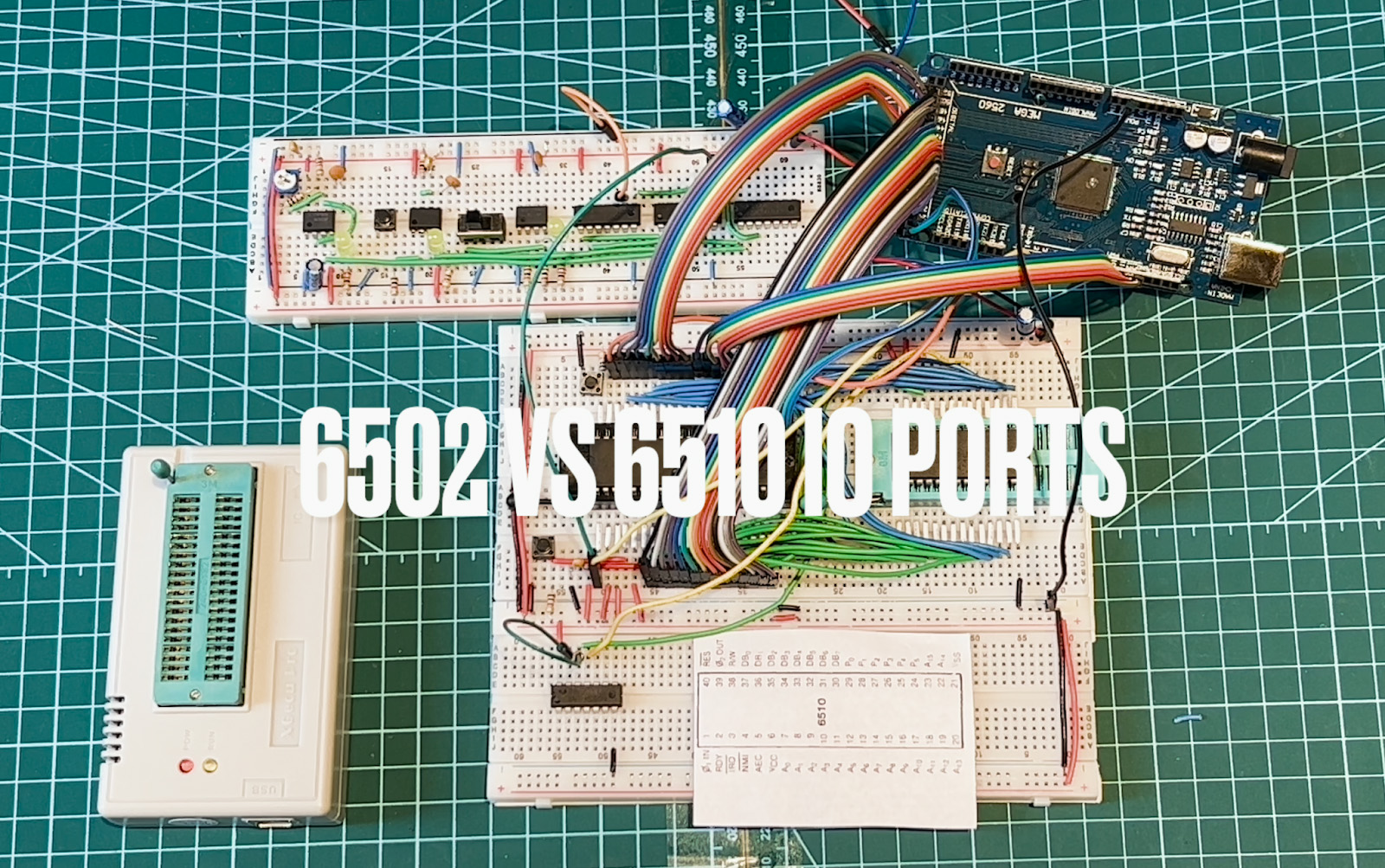

6502 vs 6510 Episodio 10 – Conectando una Memoria Static RAM

Continuamos este estudio comparativo del 6502 vs el 6510 esta vez conectando una memoria Static RAM del modelo 62256 que posee 32kb.

Vamos a estudiar cómo conectar esta memoria tanto a un 6510 con CIA 6526 como a un 6502 con VIA 6522, incluiremos todas las rutinas de assembler para poder probar la memoria, sus conexiones físicas y timing de la memoria con el procesador, punto central de su funcionamiento.

La Memoria HM62256B

Esta memoria es una static ram, esto implica que los datos que esta posee no necesitan ser refrescados cada cierta cantidad de ciclos de reloj sino que los mismos se conservan mientras esta no pierda electricidad.

Su denominación de 256 refiere a sus 256Kbits disponibles, estos están organizados en 32768 entradas de 8bits cada una lo que conocemos normalmente como 32Kbytes.

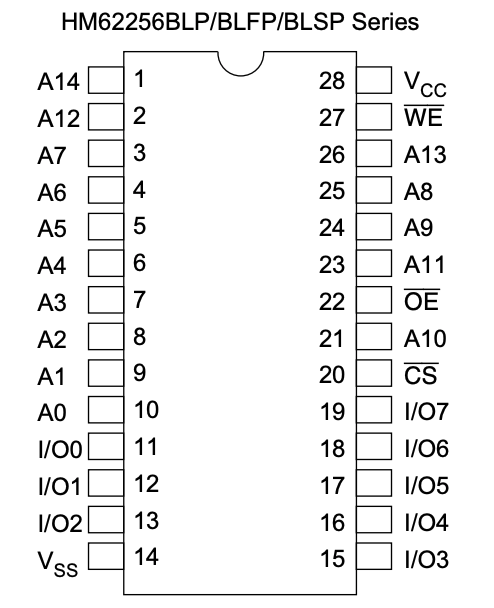

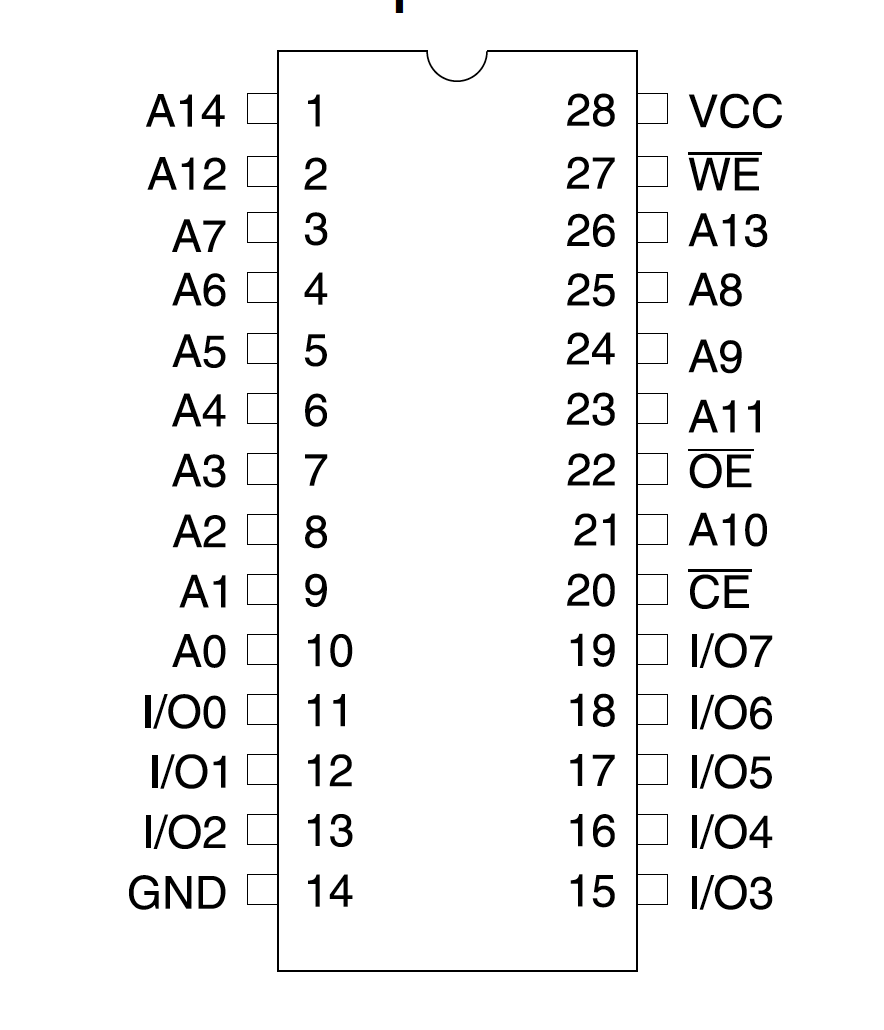

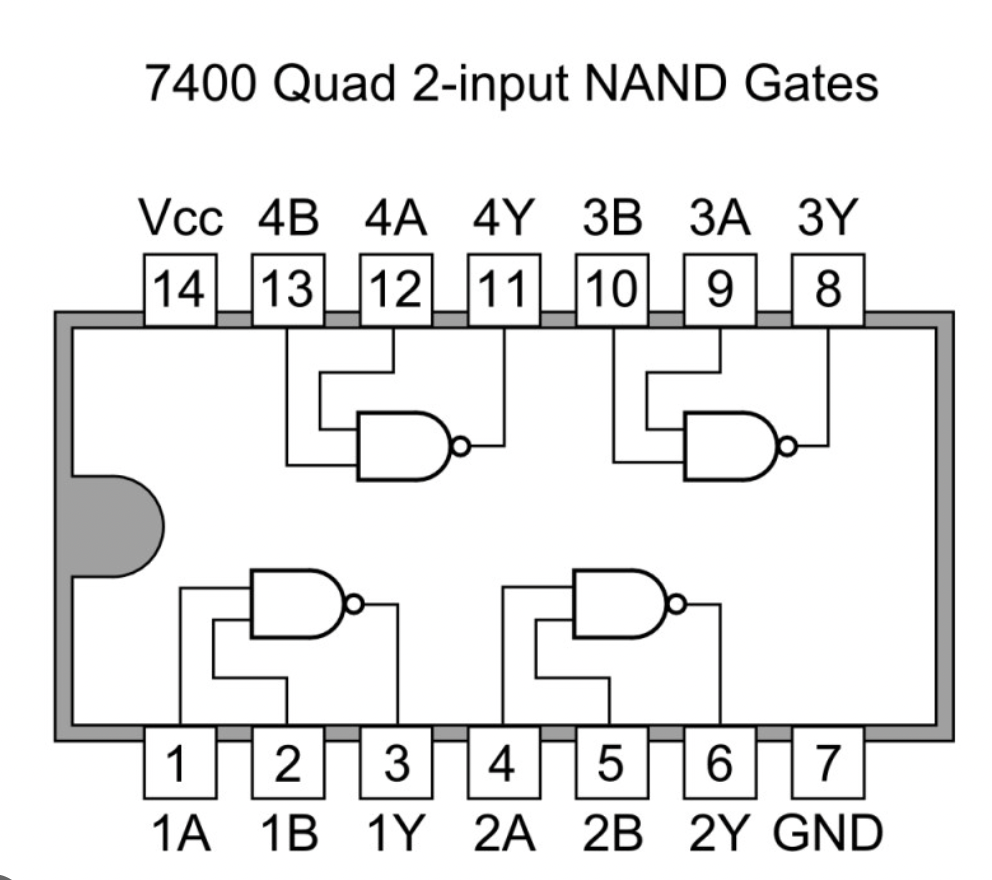

PinOut

Este chip viene en formato DIP (Dual Inline Pins) de 28 pines y es muy parecido en su layout a la eeprom AT28C256 que vimos en un artículo anterior.

A14 – A0: Estos pines nos permiten seleccionar qué registro de ocho bits queremos acceder dentro de nuestra memoria, al ser 15 pines podemos direccionar 2ˆ15 = 32768 registros de 8 bits. Estos pines se conectan al bus de direccionamiento.

I/O 0 a I/O 7: Los pines de I/O es donde vamos a ver el contenido de cada registro previamente seleccionado para leer la memoria, o donde vamos a enviar los datos que tenemos para escribir la memoria. Estos pines se conectan al bus de datos.

VCC: En este pin es donde el chip espera una alimentación de +5Volts

GND: Este es el pin de referencia a tierra del chip

/WE: El pin de write enable al recibir una señal de low o 0 Volts permite grabar en los registros de la memoria. Como la estamos utilizando como una ROM conectamos este pin directamente a +5 Volts para que sea de sólo lectura. La barra / significa que este pin es active low con lo cual espera 0 Volts para activarse

/OE: El pin de output enable conecta o desconecta los pines de I/O del bus de datos. Si el pin está en +5 Volts la memoria se desconecta del bus de datos poniendo sus pines de datos en un estado de alta impedancia. La barra / significa que este pin es active low con lo cual espera 0 Volts para activarse

/CE: El pin de chip enable conecta o desconecta los pines del chip para una lectura o escritura trabajando en conjunto con /OE y /WE. Es active low con lo cual espera 0 Volts para activarse

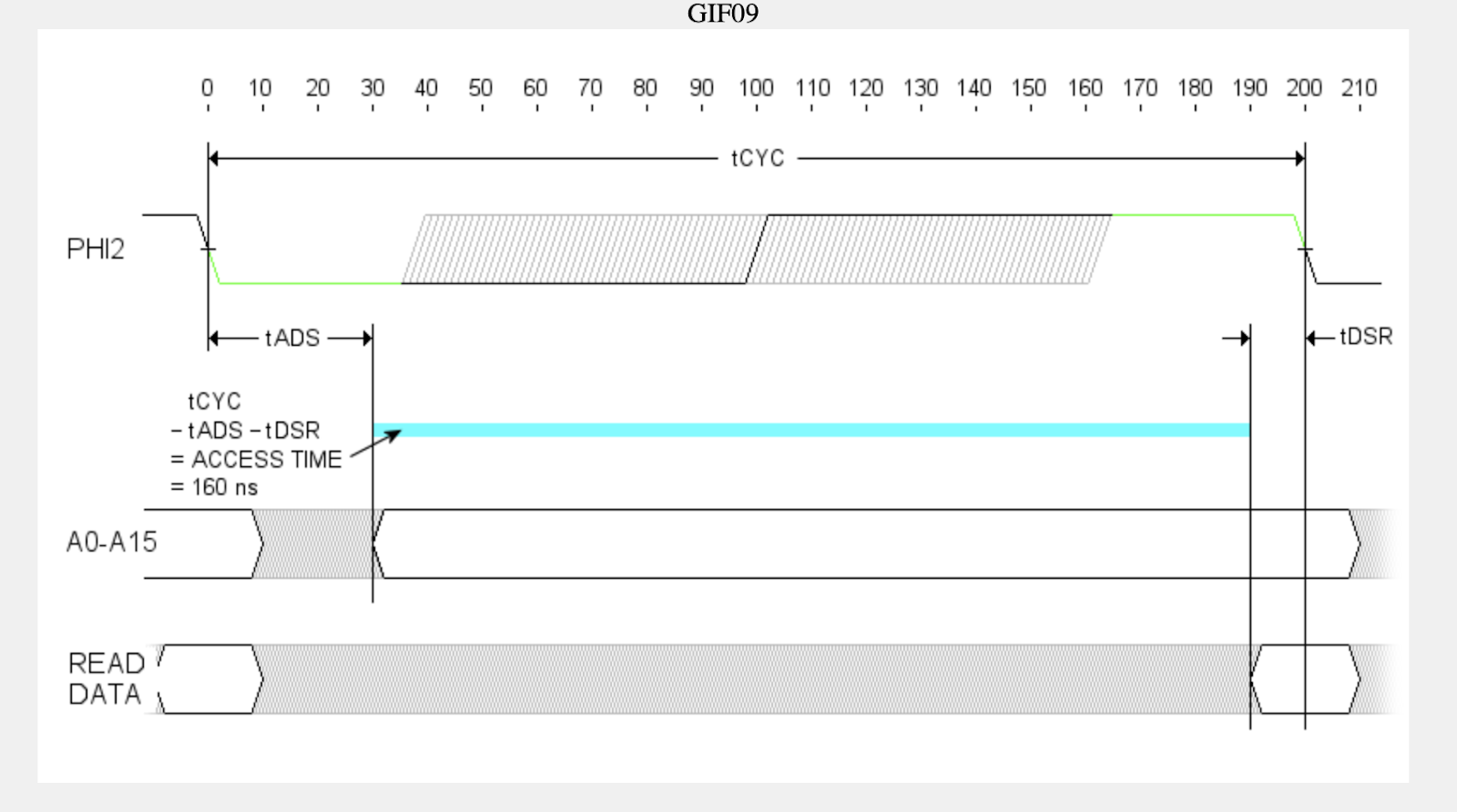

Timing para una lectura

Cuando un procesador y una memoria necesitan comunicarse ya sea para lectura o escritura hay dos tiempos generales que tienen que ser compatibles: el tiempo en que la memoria responde y el tiempo que el procesador puede esperar. Para poder leer o escribir tenemos que realizar una combinación de 3 pines /WE /OE /CE. En el caso de una lectura WE debe estar en High y OE y CE en low, para una escritura los 3 pines deben estar en LOW.

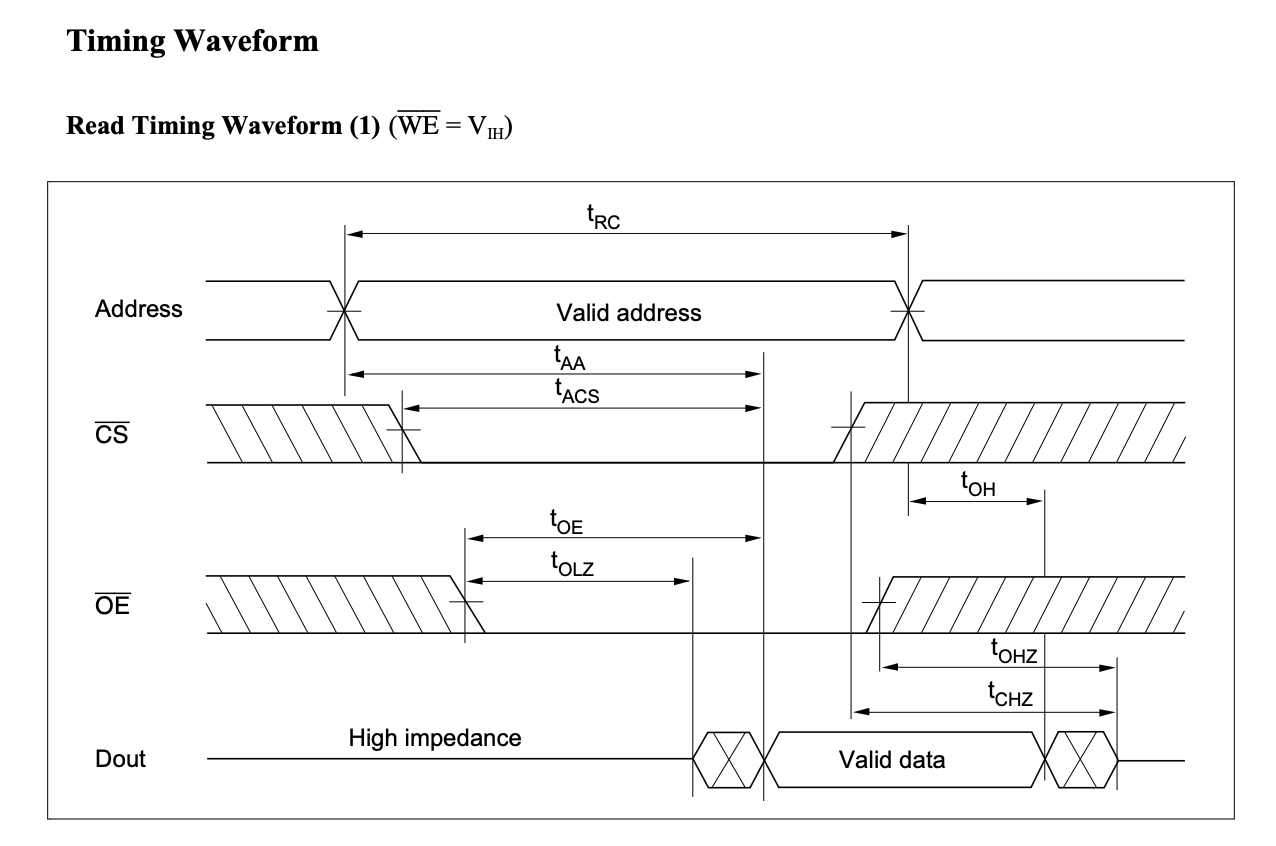

Timing de la Memoria en una lectura

Para poder hacer una lectura de la memoria, primero el procesador debe poner en el address line o bus de direccionamiento la dirección donde está el dato que quiere leer, esta dirección consiste en los unos y ceros o los highs y lows de los pines A15 a A0.

La memoria no tiene inmediatamente disponibles los datos elegidos sino que tarda en buscar el dato y en poner el mismo en el bus de datos con sus 8 bits representados por los pines D7 a D0 y tarda en que estos estén estables, que sean válidos y que reflejen el valor interno en la memoria por lo que el procesador tiene que esperar un tiempo hasta que estos datos sean válidos y recién ahí leerlos, en el caso del datasheet del ejemplo 70ns como mínimo debe ser el tiempo de espera del procesador.

Hagamos el análisis paso por paso utilizando el siguiente diagrama.

Primero el procesador tiene que colocar los 16 bits del address line en forma correcta pero estos puede que no sean seteados al mismo tiempo o en algún orden específicos con lo que el bit 1 puede setearse luego el 15, luego el 12, etc. Tenemos que esperar hasta el punto donde comienza TRC o Read Cycle Time que es el momento donde el address bus tiene los 16 bits en forma correcta.

El procesador deberá esperar un tiempo tAA o Address Access Time, que es el tiempo para que los datos en el bus de datos sean válidos y con valores correctos. Cuando el tiempo tAA termina recién ahí los datos o bits o highs y lows que están en el bus son válidos y representan la dirección deseada.

Este tiempo posee dos subcomponentes tACS o chip Select to access time que es el tiempo que tarda el chip en activarse cuando recibe una señal low en el pin de Chip Select y también tOE o Output Enable to Output Valid, qué es el tiempo que tarda en activarse los pines de output luego de recibir un low en el pin de Output enable y que estos pines reflejen el valor correcto del contenido de la memoria en el bus de datos..

¿Cómo sabemos cuánto puede tardar como máximo el chip en darnos datos válidos una vez que tenemos un address válido en el bus de direccionamiento? Con una tablita de tiempos de acceso disponible en el datasheet de cada chip.

Si vemos para el chip de la familia HB62256B si termina el mismo en -7 el tiempo máximo de address access time o tAA es de 70 nanosegundos, podemos deducir que es tiempo máximo de tACS el chip select to access time o lo que tarda en activarse el chip ya que este timer tarda 70 ns y el de tOE de Output enable to output valid solo tarda 40ns como máximo.

tAA = 70 ns

tACS = 70ns

tOE = 40ns

Otro tiempo importante que vamos a utilizar en el futuro es el tOH o el Output hold time from address change, este tiempo es cuánto los datos vamos a mantenerse como válidos desde que cambió el address en el bus de direccionamiento, este es de 5ns

tOH = 5ns

Ahora cómo sabemos si el procesador que utilizamos puede esperar 70 nanosegundos? Estudiando el diagrama de timing del mismo,

Timing del Procesador 6502 en una lectura

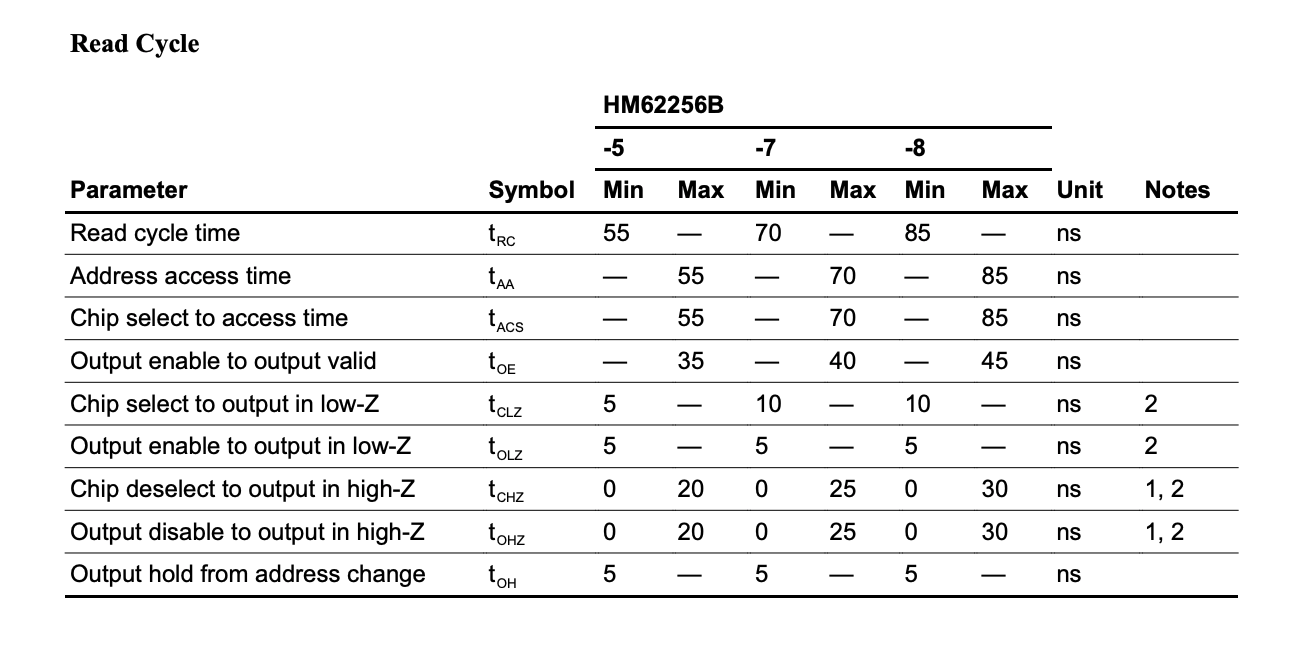

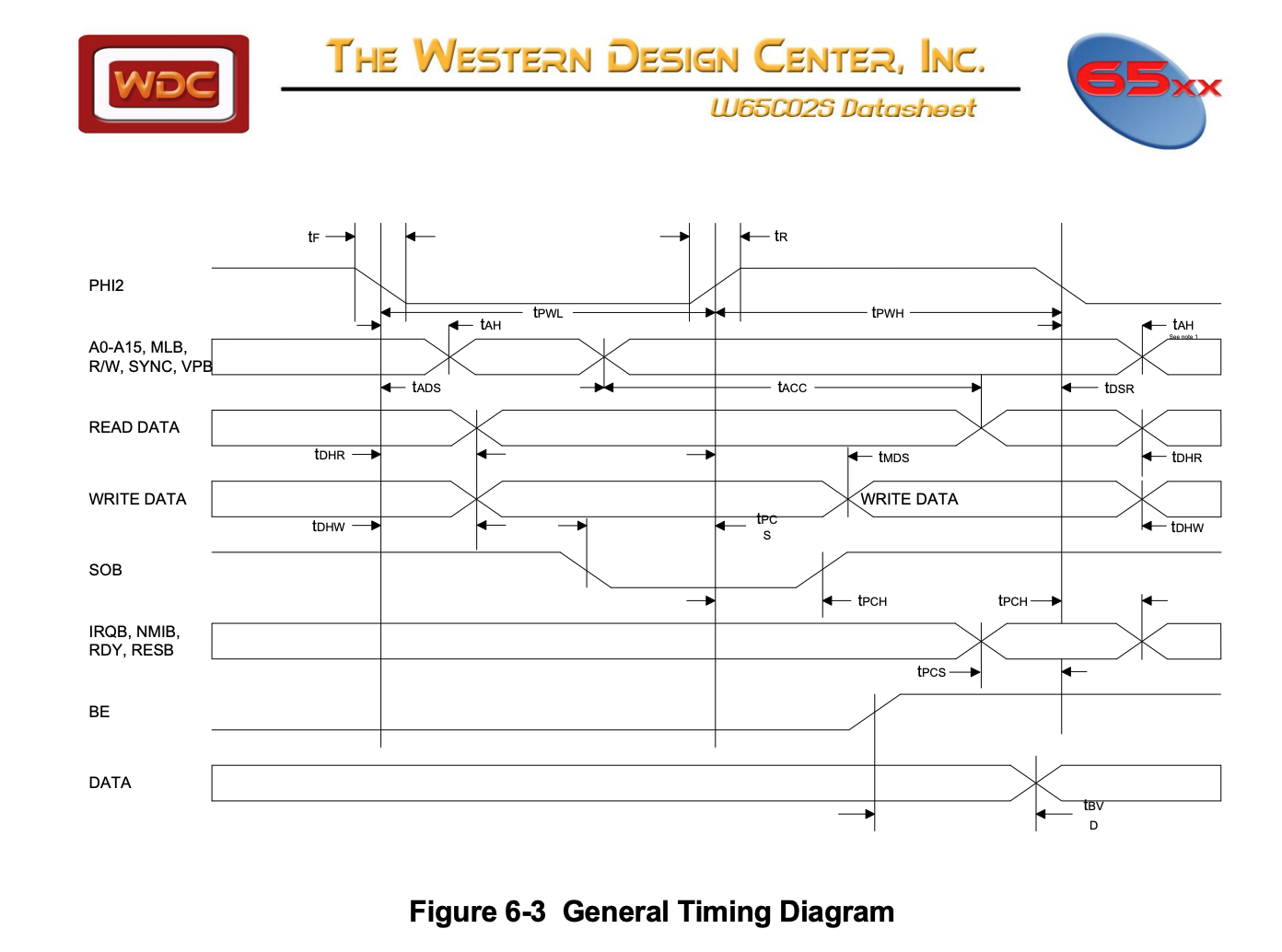

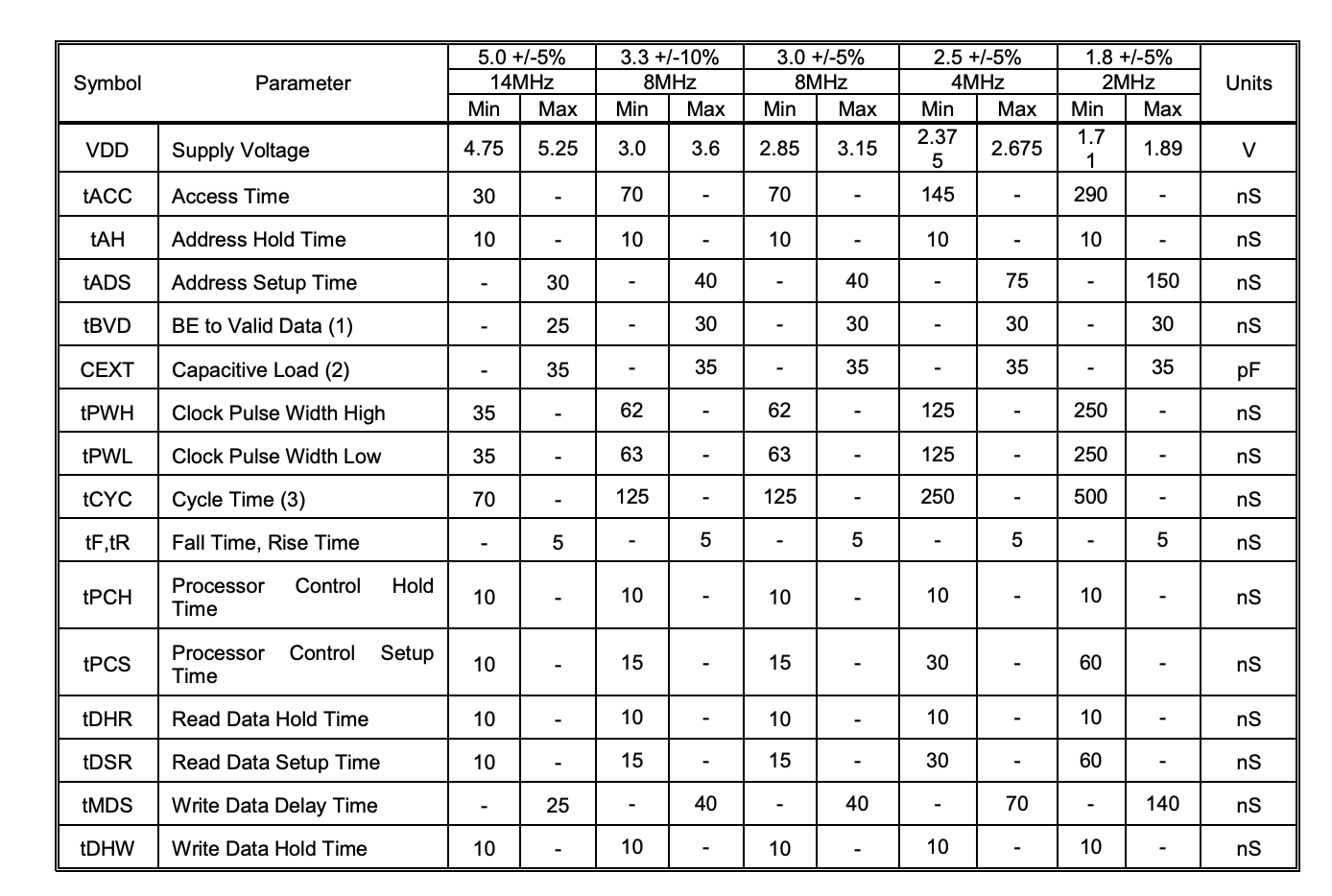

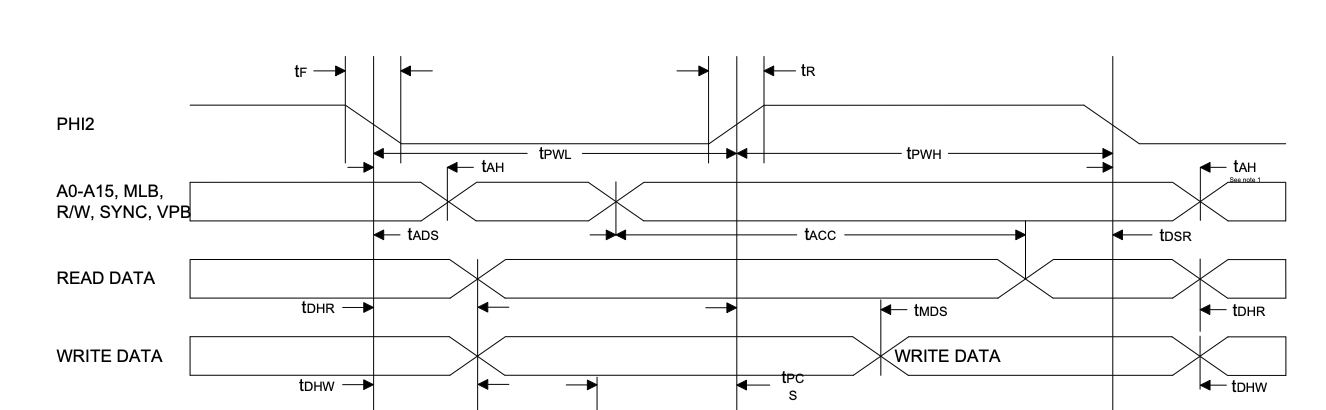

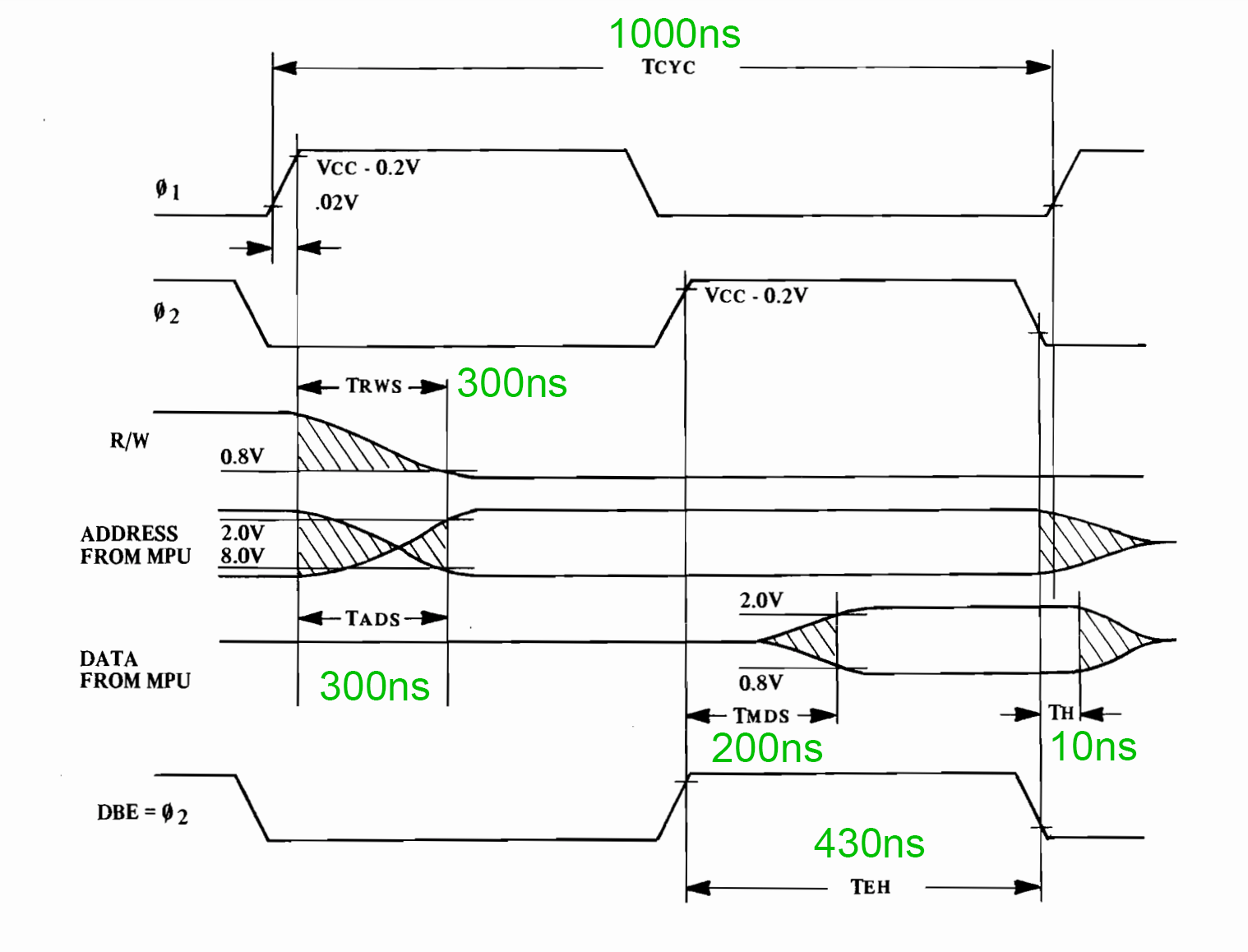

El siguiente es el diagrama de tiempos del procesador 6502 hecho por Western Design Center. El problema con este diagrama es que mezcla los tiempos de escritura y de lecturas al mismo gráfico por lo que construí un diagrama simplificado para poder entenderlos mejor.

Por otro lado la velocidad de cada uno de estos intervalos va a depender de a que voltaje nosotros manejemos el cpu, como estamos usando +5 Volts esa es la columna que utilizaremos. Estos voltajes nos van a dar un máximo de 14Mhz para correr nuestro CPU pero lo vamos a estar corriendo a 1Mhz.

El ciclo del Reloj

El primer tiempo que nos interesa saber es el de un ciclo completo de reloj, este está representado en el diagrama como PHI2 y se divide en tPWL y tPWH (Clock Pulse Width Low y High respectivamente). Al usar un reloj de 1Mhz vamos a tener disponibles 1000 nanosegundos para todo el ciclo completo de reloj.

(1)

tPWL va de 0ns a 500ns

tPWH va de 500ns a 1000ns

El mínimo de tiempos de estos intervalos podría ser de 35ns cada uno o sea 70ns de ciclo de reloj si lo corriéramos a 14Mhz pero sabemos que por lo menos necesitamos 70ns para que nuestra memoria nos de los datos con lo cual esta velocidad no es adecuada.

Las preguntas que debemos responder primero para ver si podemos esperar esos 70ns que tarda en acceder a los datos la memoria que estamos utilizando es cuando el procesador configura el address en sus pines y cuando r ealiza la lectura.

Estableciendo el Address en el Bus de Direccionamiento

El segundo tiempo que vamos a tener que estudiar es el tADS o Address Setup Time , es el tiempo que le toma al cpu estabilizar los highs y lows en los pines del bus de direcciones. Y el tercer tiempo es el tAH o Address Hold Time, por cuánto tiempo esos highs y lows son válidos en el bus de direcciones.

(2) tADS = 30ns

(3) tAHT = 10ns

El tADS comienza en el falling edge del comienzo del ciclo del reloj.

El tAHT se mantiene desde el falling edge (transición de High a Low) del final ciclo del reloj.

Leyendo los datos

El cuarto tiempo a estudiar es el tDSR o Data Setup Time, que es cuánto tiempo tardan en estabilizarse los highs y lows en el bus de datos y el quinto tiempo es el tDHR o data Hold read time o cuánto tiempo esos datos són válidos.

(4) tDSR = 10ns

(5) tDHR = 10ns

El tDSR termina desde el falling edge (transición de High a Low) del ciclo del reloj en ese falling edge es cuando ocurre la lectura.

El tDHR son por lo menos 10ns desde el momento de la lectura.

Tenemos que asegurarnos que la RAM esté dando datos válidos durante tDSR + tDHR. Tenemos que asegurarnos que la RAM esté dando datos válidos durante tDSR + tDHR.

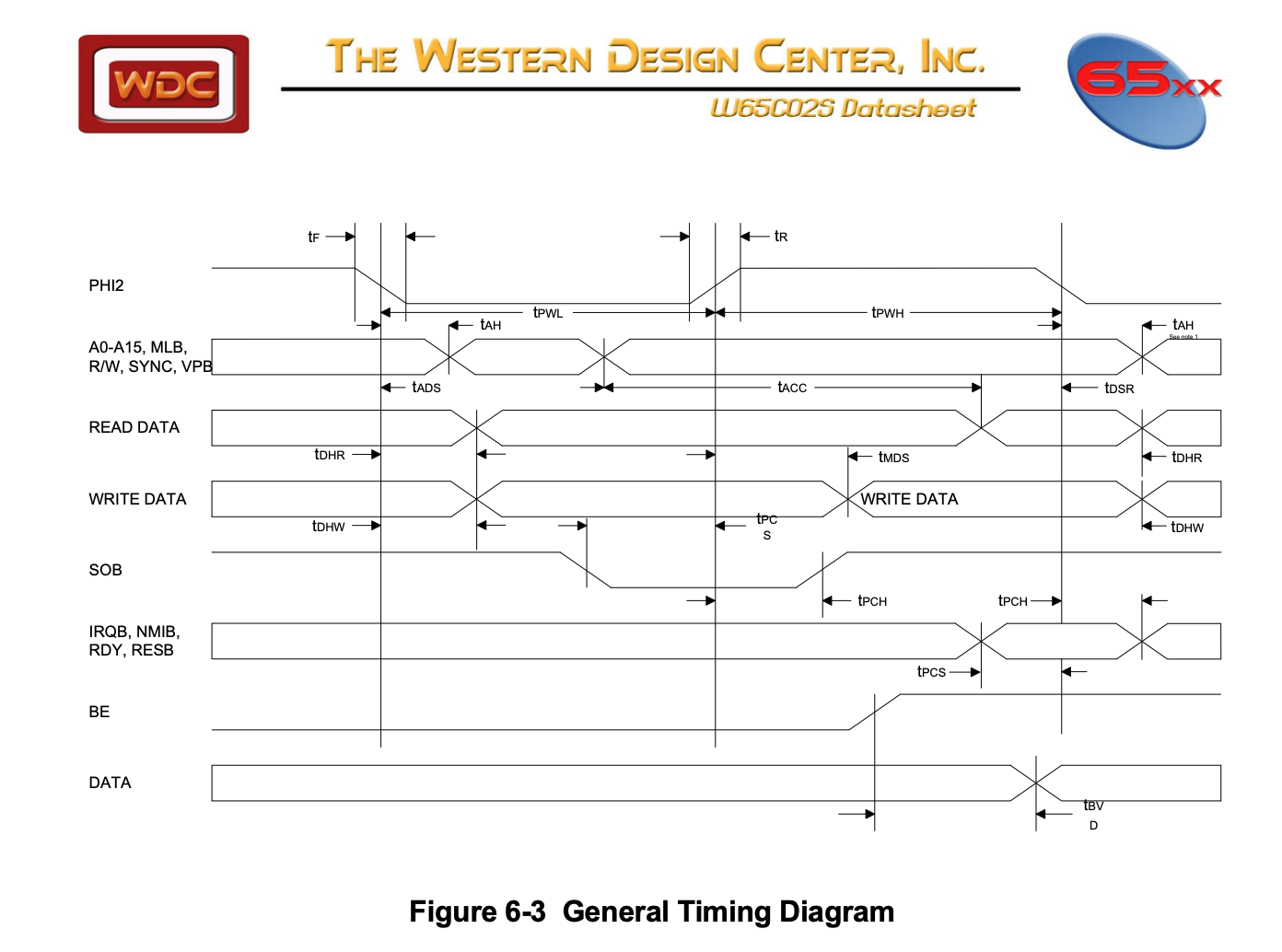

Si hacemos un esquema podemos ver:

0ns a 30ns necesitamos que el address sea estabilizado tADS

30ns a 1010 ns el address el válido tAHT

990ns a 1010ns los datos tiene que ser válidos tDSR + tDHR

Con lo cual la ram tiene 990 – 30 = 960ns para poder dar los datos en el bus, pero como vimos la RAM sólo tarda 70ns como máximo para darnos los datos por lo que tenemos mucho tiempo disponible.

Pero por cuánto tiempo la RAM mantiene los datos válidos en el bus? Para esto está el timer tOH de la RAM que es de 5ns a partir de que cambia la dirección de la ram, pero la dirección cambia recién en el ns 1010 que es cuando expira el timer de address hold time del procesador lo que nos da unos 5ns extras para la lectura.

990 ns a 1015ns la RAM da valores de highs y lows válidos en el bus de datos

Por esto podemos hacer la lectura por que el procesador requiere de 10ns después del momento de la lectura y la RAM mantiene los datos válidos por 15ns

De forma similar a como hicimos este análisis podemos realizar lo mismo para la escritura de la memoria variando solo algunos valores de los parámetros.

Un gran lugar para poder ver alternativamente como funcionan los diagramas de tiempo del 6502 es este sitio donde se ve muy bien visualmente Visual Guide to 65xx CPU Timing

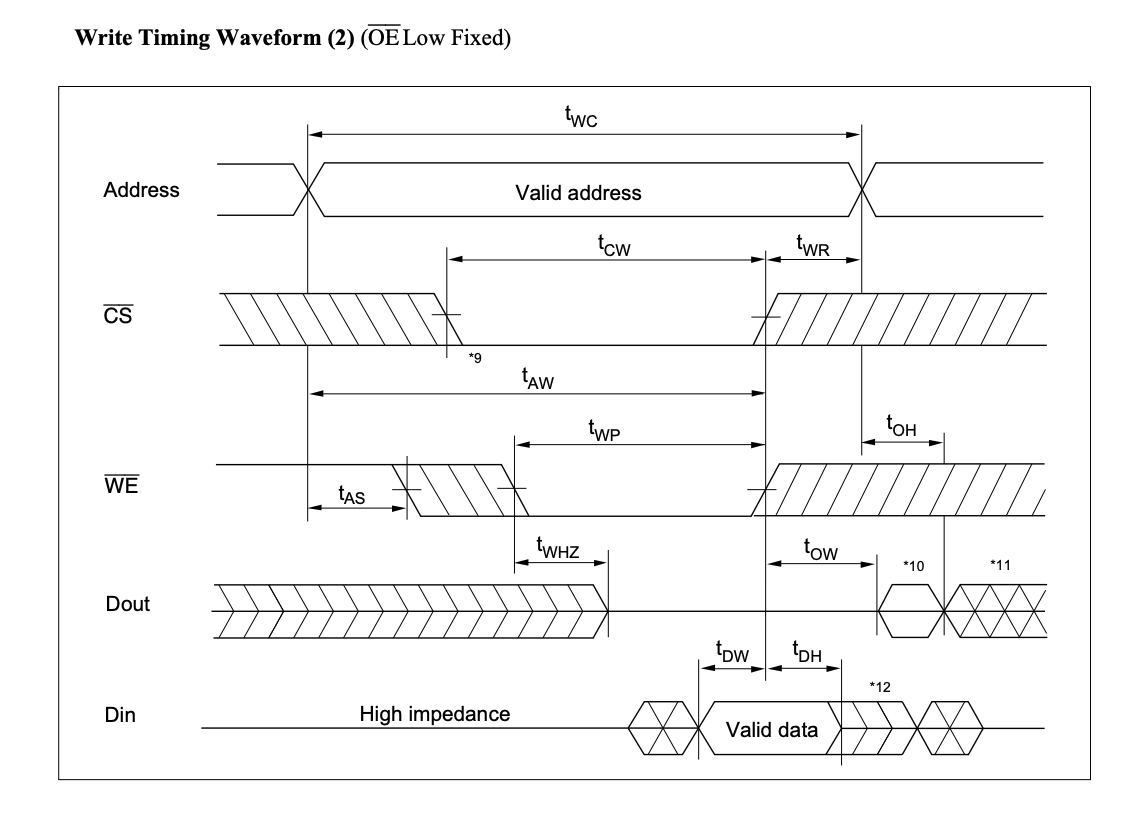

Timing para una escritura

Con la información que ya tenemos de interpretar cómo se hace una lectura encaremos la escritura de datos en la memoria.

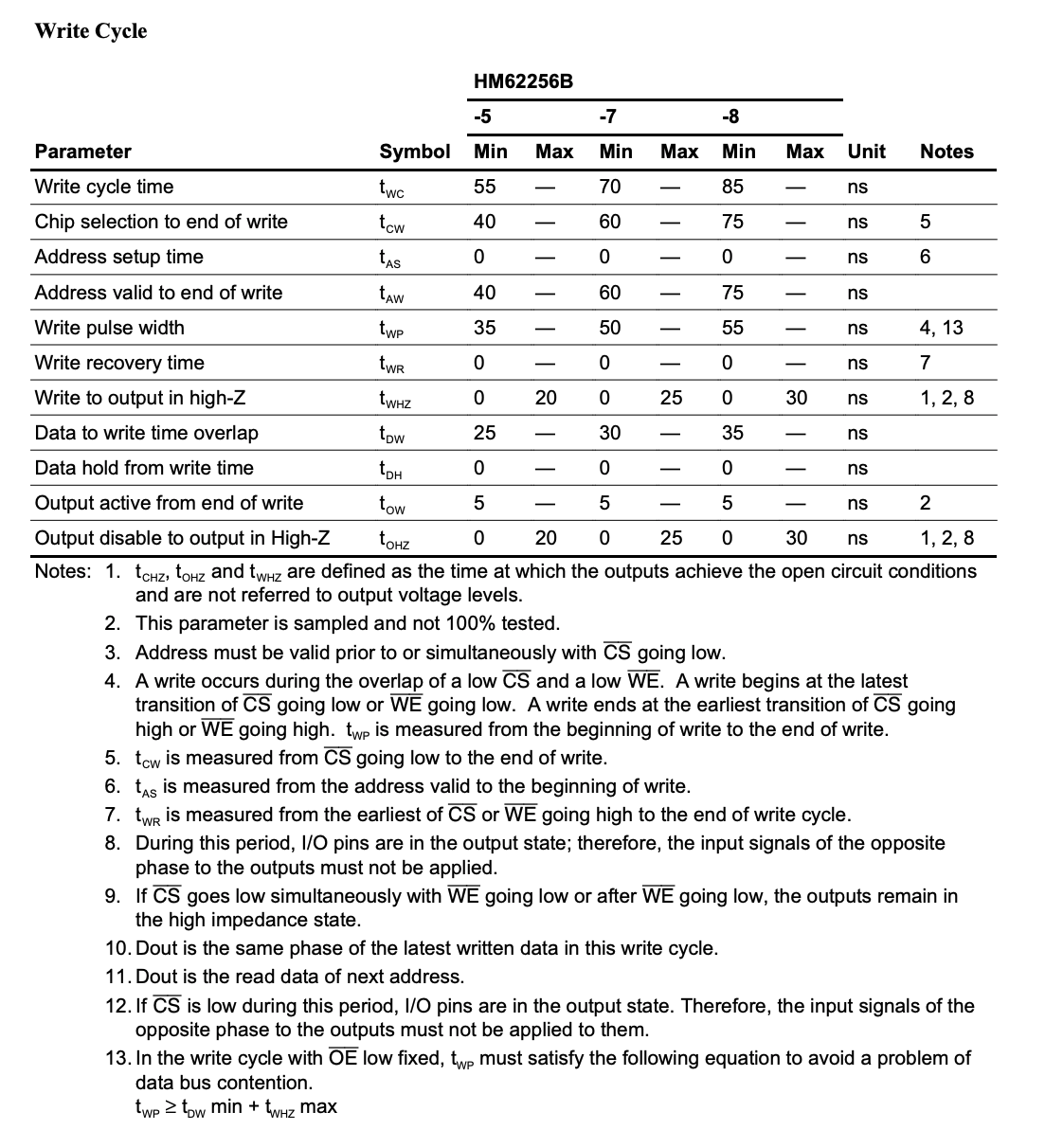

Timing de la Memoria en una escritura

Veamos este nuevo diagrama de tiempos para la escritura.

Y también los nuevos valores mínimos y máximos para estos parámetros

Este diagrama asume que el pin de OE output enable está fijo en Low y según la nota 4 la escritura se va a realizar cuando CS y WE ambos estén el Low.

Comienza el tiempo tWP o Write Pulse Width cuando el último pin entre WE y CS entren en low y dura hasta que el primero de ellos pase a High.

tWP = minimo de 50ns

Los datos deben ser válidos en el bus por lo menos desde tDW o Data Write time overlap y mantenerse válidos por un período tDH o Data Hold form write time

tDW = 30ns

tDh = 0ns

Con lo cual por lo menos 30ns antes de que WE o CS pasen a ser High los datos deben mantenerse como válidos.

Si analizamos lo que puede pasar, el bus de datos puede tener cualquier información errónea sin problemas y esos datos se escriben en la ram, pero por lo menos 30ns antes de que se termine la escritura los datos deben ser válidos ya que estos quedarán en la RAM, estos datos válidos pueden ser mantenidos por 0ns enel bus si queremos ya que ya han sido escritos ya que el mínimo de tDH es cero.

Timing del Procesador 6502 en una escritura

Veamos este nuevo diagrama de tiempos para la escritura.

Sabemos que los siguiente tiempos se cumplen debido a nuestro análisis anterior:

0ns a 30ns necesitamos que el address sea estabilizado tADS

30ns a 1010ns el address el válido tAH

1000 ns a 1010ns tDHR

Los datos se vuelven inválidos al final de tDHR que coincide con tAH y con un nuevo timer tDHW o Write Data Hold Time

tDHW = 10ns desde el falling edge fin del clock cycle

1000 ns a 1010ns tDHW

El write ocurre en el falling edge del final de clock cycle. Pero para que la escritura sea correcta los pines de CS o WE tienen que ser high antes de que el address, los datos o el write hold time sean inválidos.

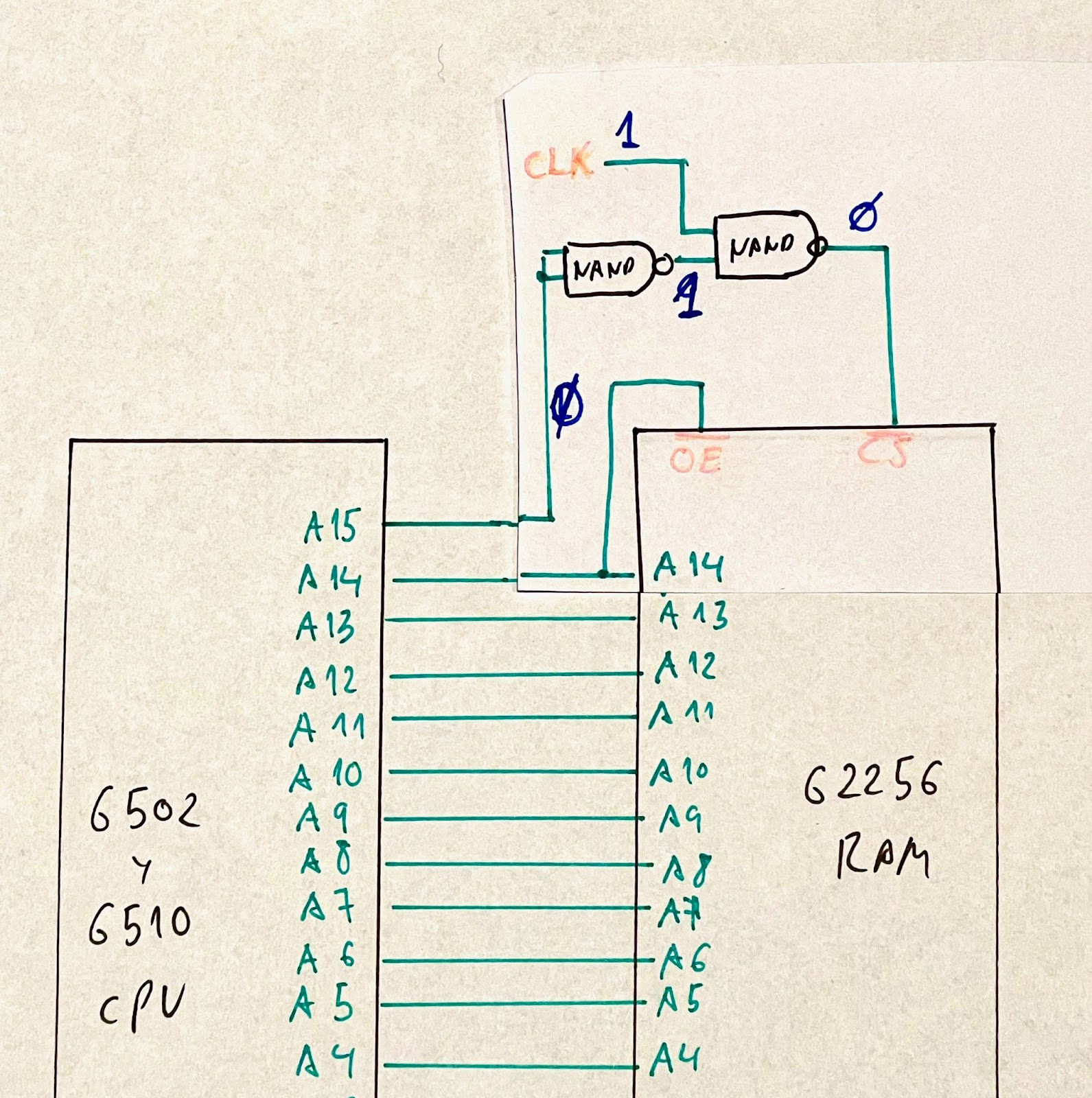

Si conectamos el pin de chip select CS a cualquier de las address lines estaríamos en problemas ya que debemos asegurar que el pin CS sea high mientras todavía todos los pines de address son válidos y todos los pines de datos son válidos, pero no tenemos forma de poder apagar un pin antes que los otros asegurándonos que sea siempre así.

Lo mismo nos sucede con el pin de R/W del procesador no hay forma de garantizar que vaya a cambiar antes que los pines de address.

Con lo que nada nos asegura que CS o WR pasen a ser High (terminando la escritura) antes de que el address y los datos seán inválidos.

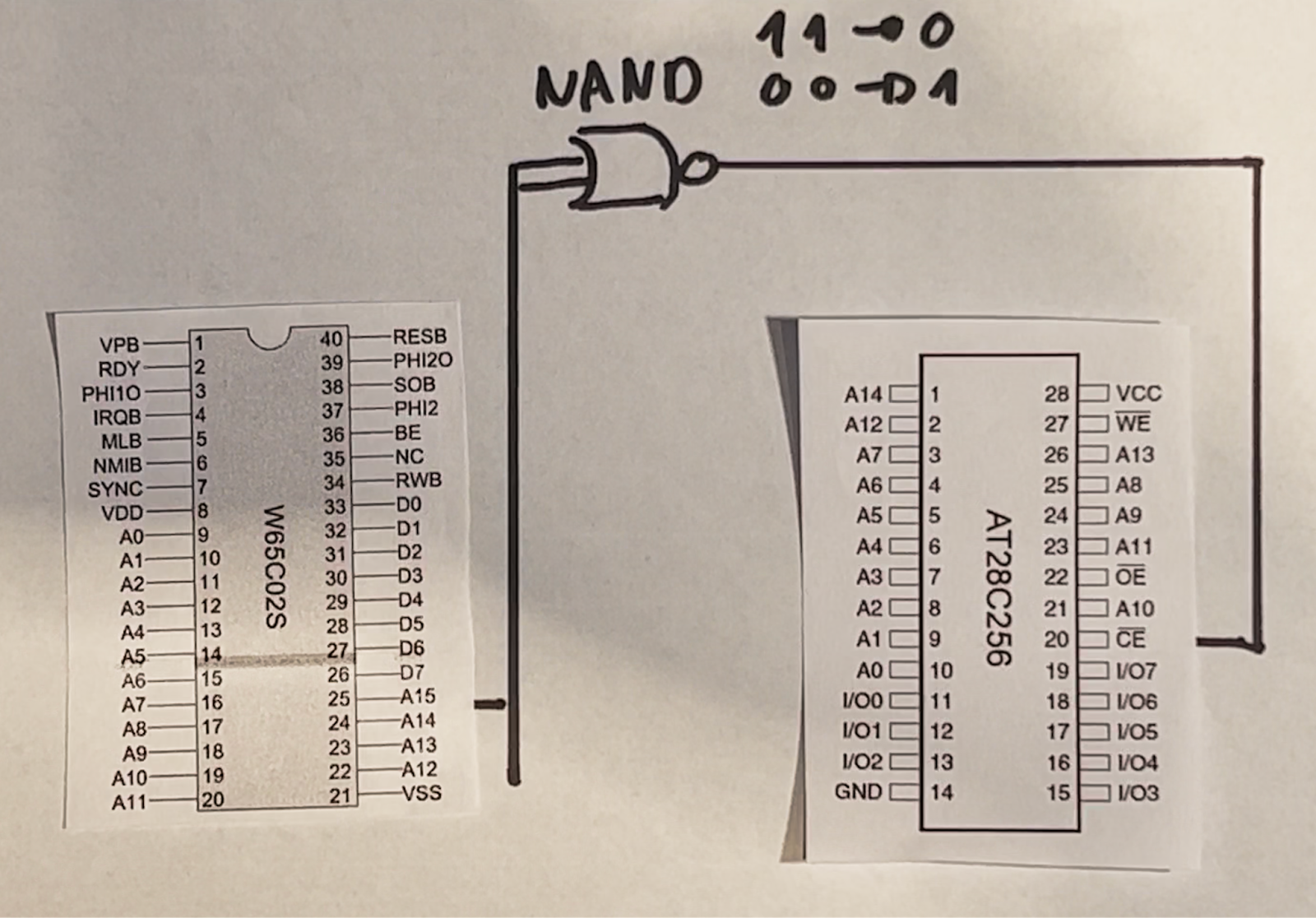

Para solucionar esto podemos hacer que el CS chip select pin sólo sea LOW durante el ciclo de pulso alto del reloj o tPWH de 500 a 1000 ns, de esta forma nos aseguraremos que el address bus tenga direcciones válidas y que unos nanosegundos tDW antes de apagarse el CS tenemos todavía datos válidos, ya que los hold timers de tAH y tDW nos mantendrían valores válidos en address y data bus respectivamente aún después de poner el High el pin de CS. En nuestro ejemplo serían 10ns extras.

Para lograr esto podemos conectar el pin a15 si lo usáramos para seleccionar nuestro pin de chip select conectado a través de dos compuertas nand de forma tal que solo en el pulso high del reloj y cuando el pin a15 sea cero el pin de la memoria de chip select reciba un cero o low.

Al agregar dos compuertas nand debemos sumar un tiempo más que el que tarda la compuerta en evaluar sus inputs y darnos un output, este tiempo se llama maximum propagation delay (tPHL).

En el caso de las compuertas que utilizamos este es de 25ns al usar 2 vamos a tener como máximo 50ns de delay, lo que implica que la señal de chip select va a ir a low 50 ns después de que si no usáramos las compuertas, en este setup ese tiempo no influye ya que tenemos 960ns disponibles con el address valid antes de que los datos estén válidos (llendo de los 30ns a los 990ns) esto nos llevaría sólo al intervalo 80ns a 990ns no implica problema alguno.

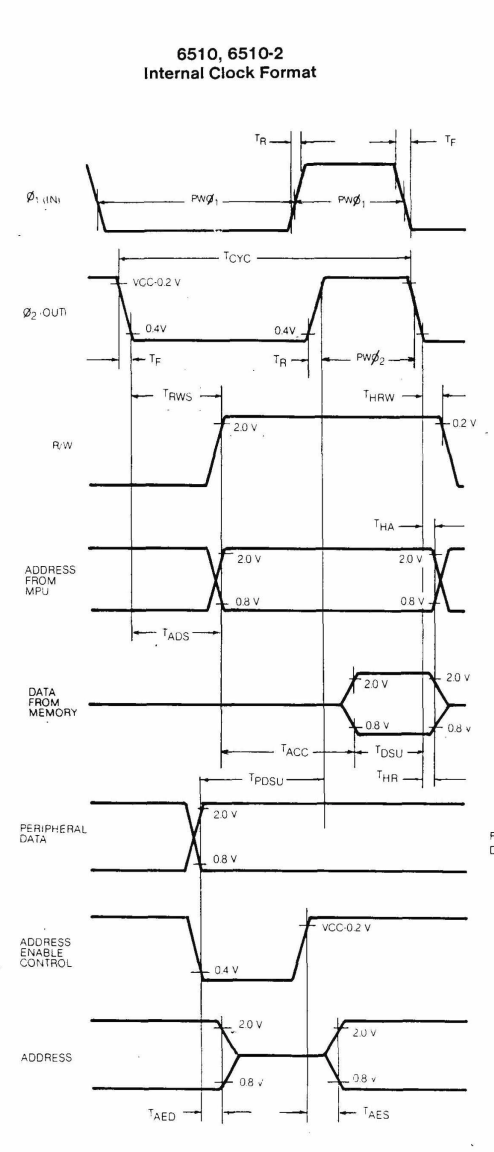

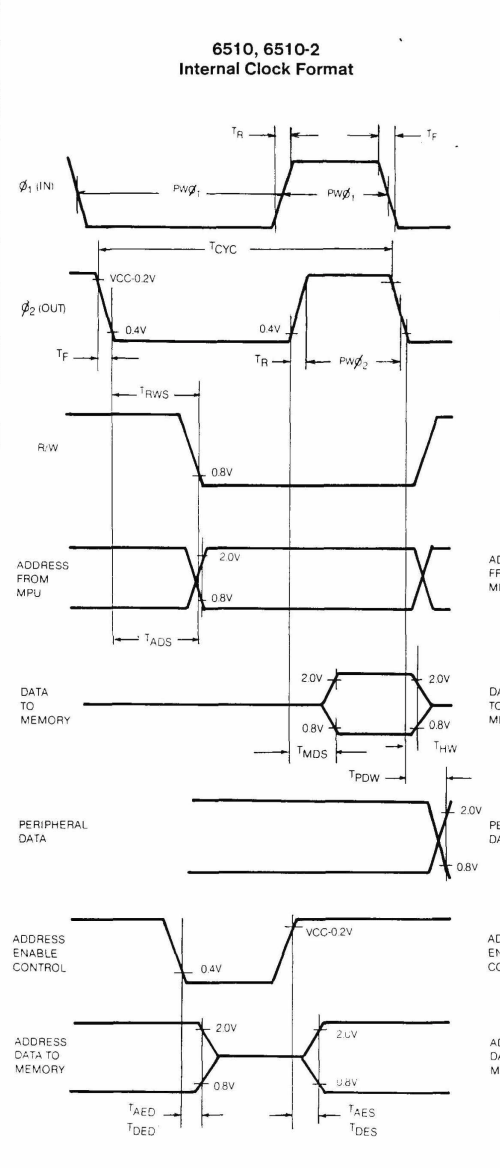

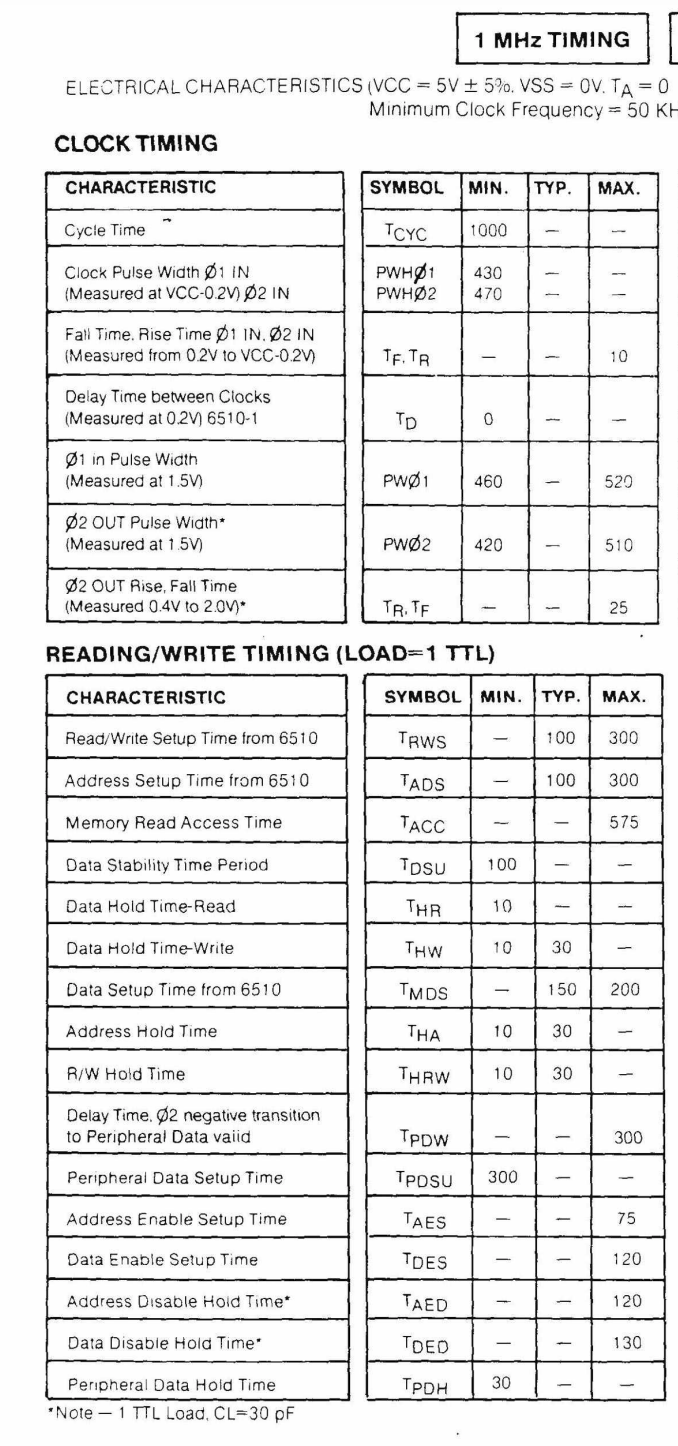

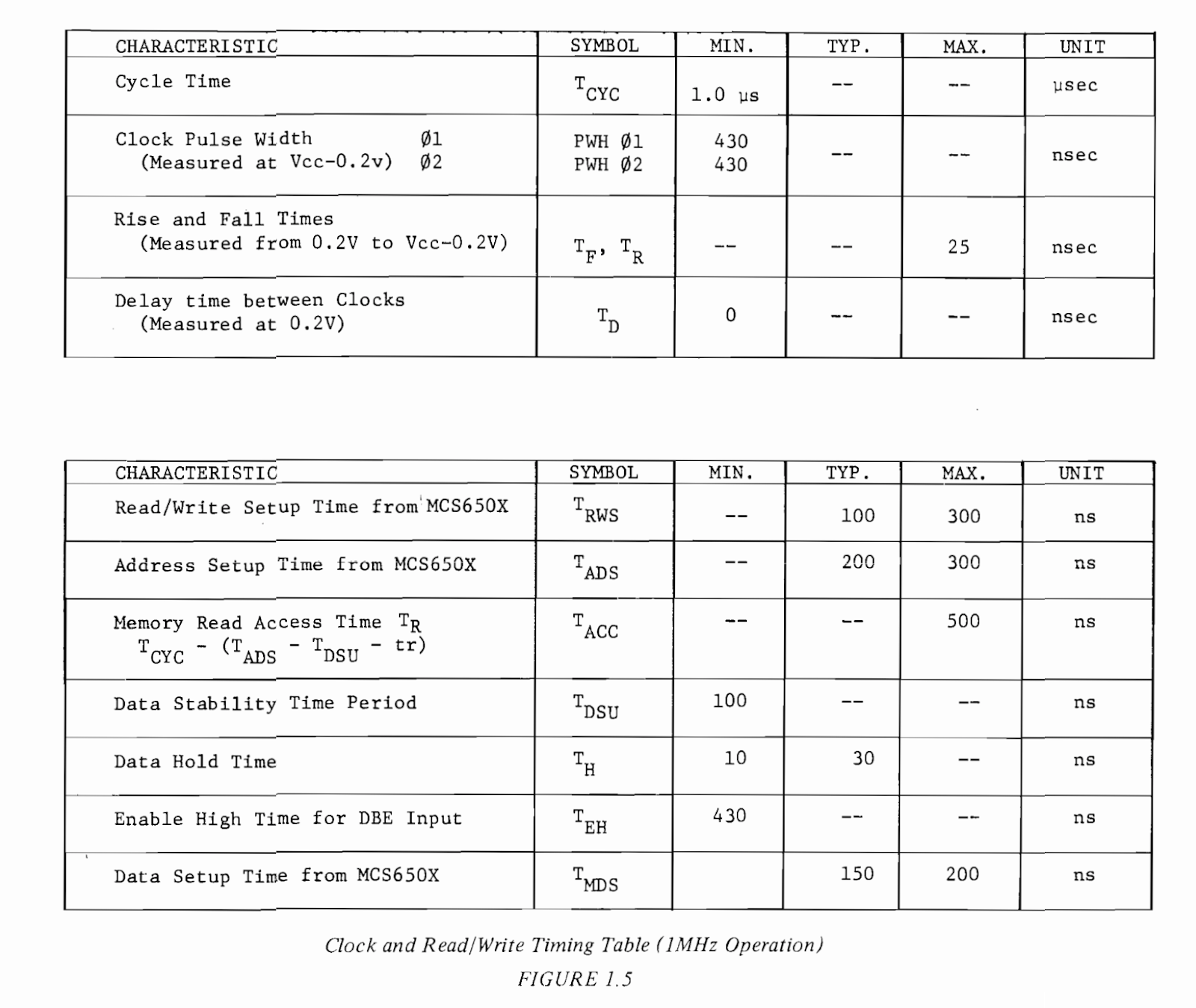

Timing en el procesador 6510

El timing en el 6510 es bastante más lento que en el 6502 y eso debemos tomarlo en cuenta, observemos estos valores y diagramas del datasheet original, el primer diagrama es de lectura y el segundo tiempos de escritura.

También tenemos algunos tiempos diferentes que los del 6502 más moderno

Así por ejemplo podemos observar el timer tADS o Address Setup Time el cual tarda 300ns en lugar de los 30ns del 6502 moderno. Si tuviéramos que hacer la cuenta con los tiempos para nuestra memoria ahora deberíamos comenzar así:

tADS = 300ms

tAH = 10ms

tDHR=tHR=10

0ns a 300ns necesitamos que el address sea estabilizado tADS

300ns a 1010ns el address el válido tAH

1000 ns a 1010ns tDHR

Y nuestra RAM muestra datos válidos desde

(tADS+tAA) a (tAH+tOE) = 300ns+70ns a 1010ns + 5ns

370ns a 1015ns la RAM da valores de highs y lows válidos en el bus de datos

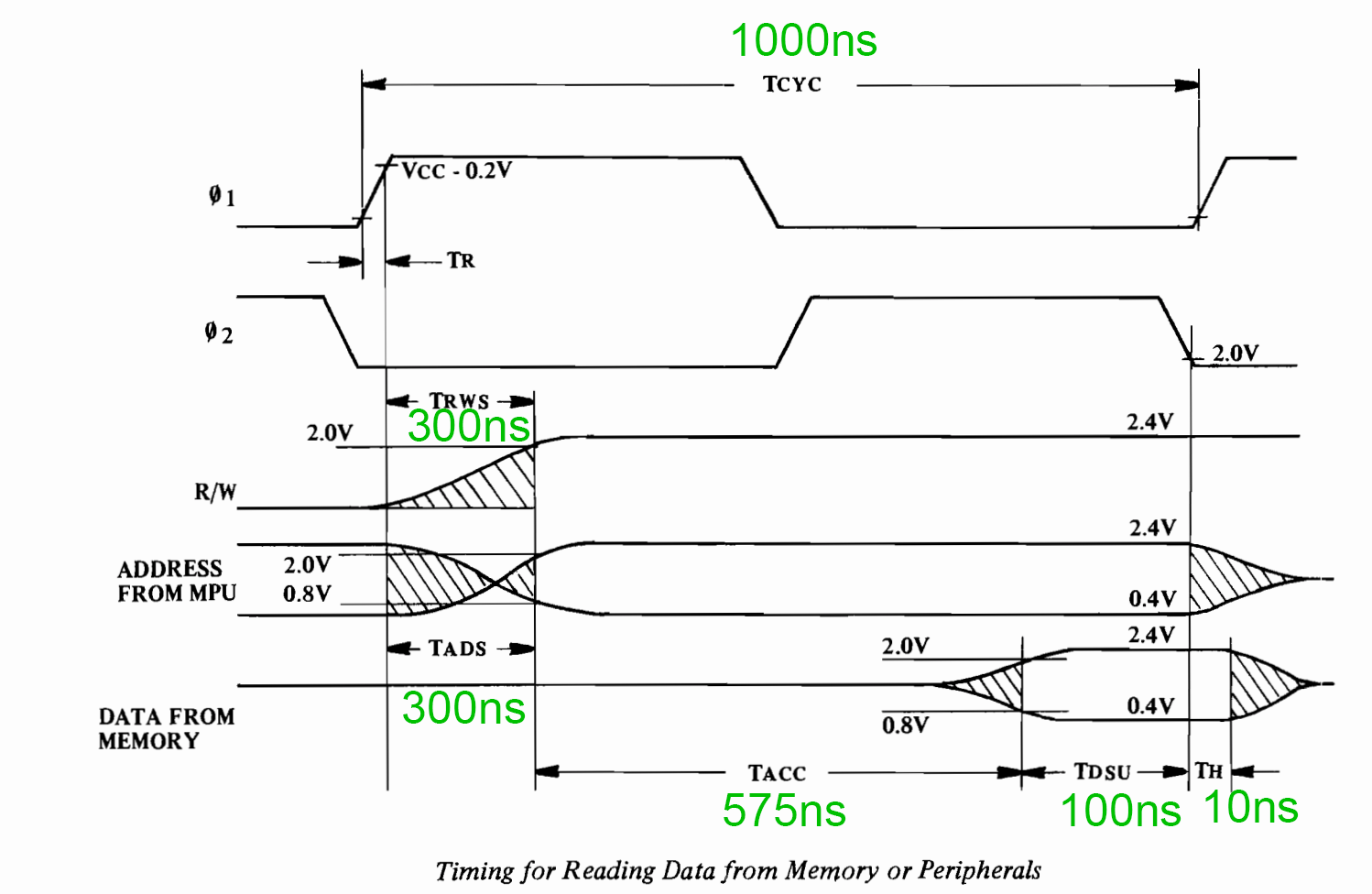

Si nos referimos al manual de Hardware de la línea de procesadores 6500 él mismo nos dice que a 1Mhz el address está estable. sí o sí, 300 nano segundos después de que comienza la fase uno y los datos deben estar estables al menos 100 nanosegundos antes de que termine la fase dos de nuestro ciclo de reloj. Esto nos da 575 ns para poner los datos en el bus de datos.

Y podemos observar los diagramas para timings de Read y Write respectivamente.

Read Timing Diagram

Write Timing Diagram

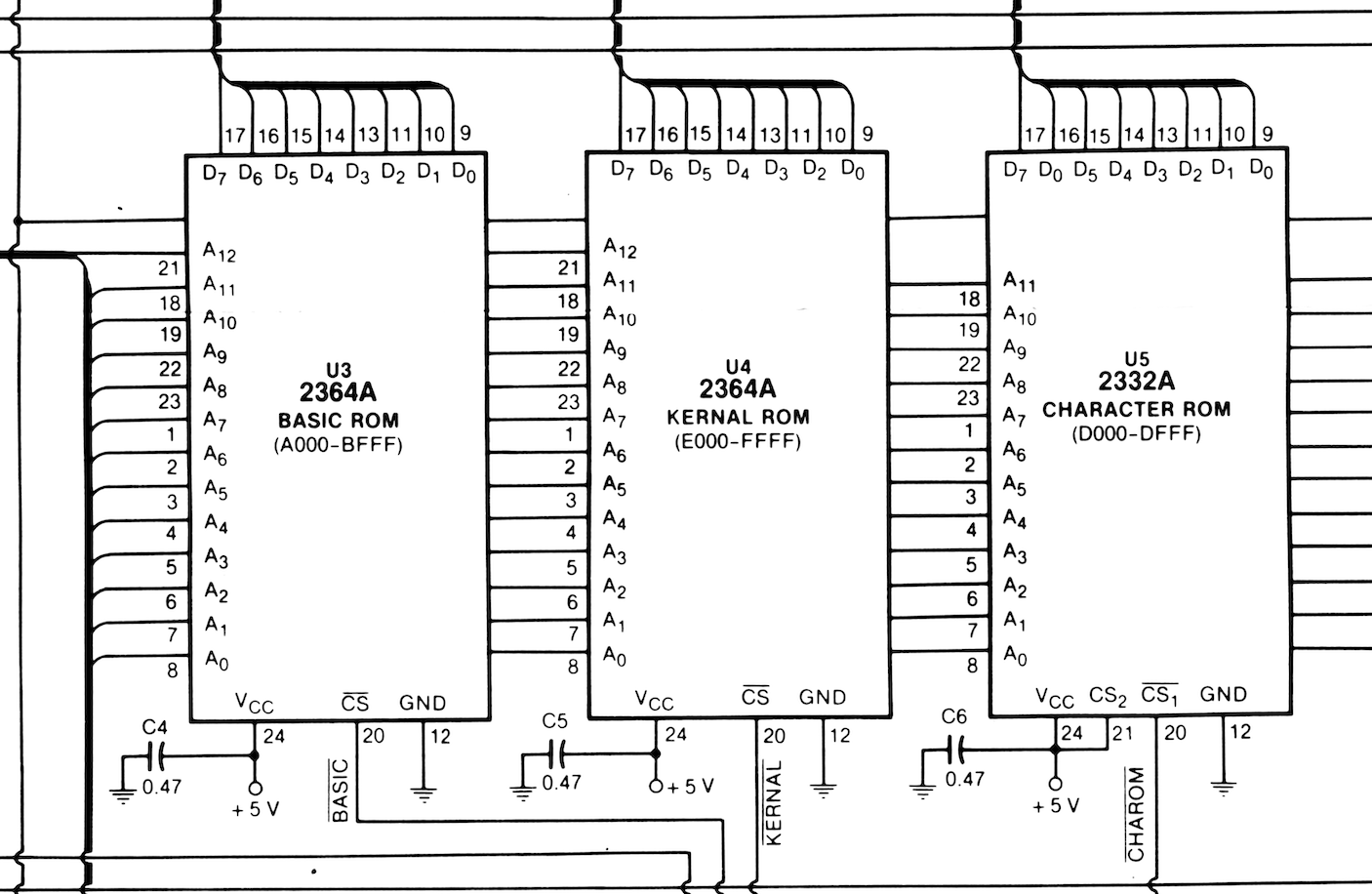

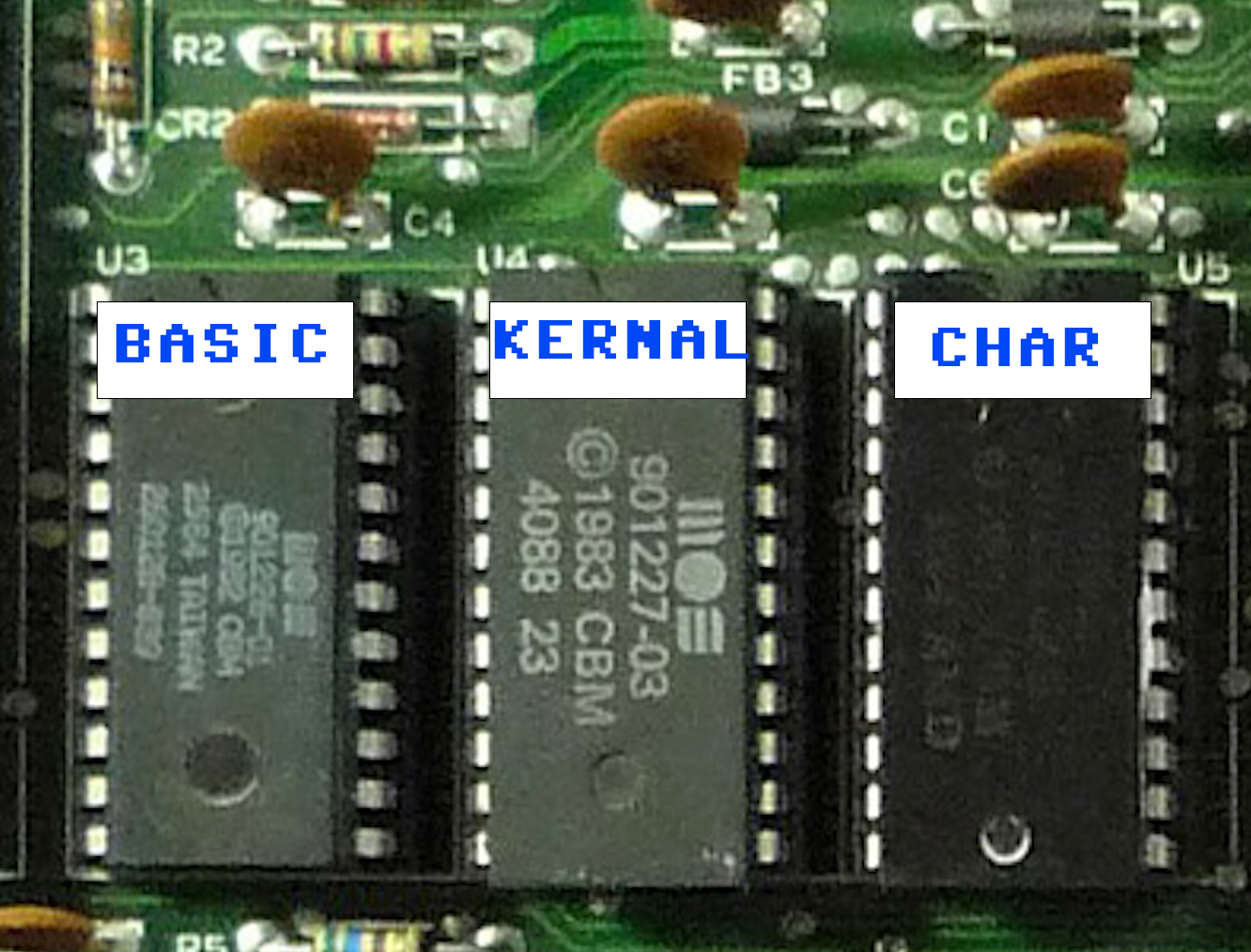

Cómo funciona en el Commodore 64

En nuestra querida Commodore 64 no estamos usando una memoria estática como la de este empleo si no que es dynamic ram, esta misma debe ser refrescada constantemente de lo que se encarga el chip de video VIC2. Esta memoria se selecciona por filas y columnas utilizando las señales de RAS y CAS.

Tampoco tenemos un sólo chip sino 8 chips cada uno de 64536 entradas y 1 bit de datos en cada entrada, con lo que si queremos representar un byte necesitamos los 8 chips y 1 bit de cada uno de ello, de ahí que cuando se rompe un chip de ram nada funciona ya que afecta al contenido de un bit en cada posición de la RAM.

Estudio visual

Para poder estudiar visualmente cómo conectar una ram estática y programarla les dejo esta video que complementa al artículo.

RAM con 6510/CIA y 6502/VIA – 6502 vs 6510 Parte 10

Referencias

A continuación les dejo algunos links donde profundizar el tema:

VIDEOS

Video de la serie 6502 vs 6510 Parte 10 – RAM

RAM con 6510/CIA y 6502/VIA – 6502 vs 6510 Parte 10

Aquí tiene acceso a toda la serie:

6502 vs 6510 estudio detallado y comparación

PAPERS

Visual Guide to 65xx CPU Timing

MOS 6500 Family Hardware Manual

Y como siempre la serie de Ben Eater del 6502

Build a 6502 computer | Ben Eater

Todos los ejemplos de código de los videos los pueden encontrar en:

Mozo, hay un Huevo de Pascua en mi ordenador!

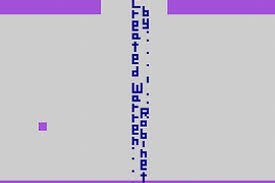

Algunos de los easter eggs mas famosos, revisitados en esta entrega en el dia de pascuas.

La película Ready Player One (2018) dirigida por Steven Spilberg y basada en el libro homónimo de Ernest Cline popularizó el ya ultra conocido (gracias a internet) “primer easter egg (huevo de pascua) de la historia”. De la historia de los videojuegos, aclaremos. Y también aclaremos que eso es lo que creemos, solo hasta que aparezca uno anterior.

Cuenta la historia que Atari era reacia a dar a conocer los nombres de los programadores, artistas y diseñadores de sus videojuegos que por aquel entonces se publicaban para sus sistemas, en este caso para el Atari VCS/2600. Lo cual tenía a estos personajes algo disconformes. Así fue que en un acto de rebeldía, en el juego Adventure (1979), si el jugador hacía una cierta serie de acciones aparecería en pantalla la leyenda”Created by Warren Robinet”, en clara declaración de autoría e inmortalizando un nombre que de otra forma, hubiese quedado como uno más del montón.

Hay que entender el contexto, claro. No es que Atari fuera un explotador tampoco. Simplemente, la industria aún estaba en pañales. Y “el Atari” era, de alguna manera, considerado un juguete. Se vendía en los mismos mostradores que los juegos electrónicos, y las máquinas de pong hogareñas. Entonces los cartuchos de juegos eran meros accesorios que uno podía comprar (o pedirle a Santa) para cambiar el juego de la consola. Un gran avance sobre la generación anterior (las maquinas de Pong), que solo tenían un juego (o variantes de esta) y la cosa ya se estaba poniendo aburrida. Fairchild ya lo había hecho un año antes, pero la idea estaba en el aire. Y bajo esa lógica, así como Mattel no publicaba los accesorios de Barbie con el nombre de sus diseñadores, ¿porque lo haría Atari o quien fuese con sus cartuchos? “Sí, lo hizo un ingeniero. Un empleado. Pero te lo vende Atari”. Desde el punto de vista de la empresa, daba igual quién fabricaba qué parte.

Pero sucede que a diferencia del caso de Barbie, los juegos terminaron siendo lo más importante de la consola. Y si le sumamos el hecho que la VCS/2600, debido a sus limitaciones, era extremadamente difícil de programar, estos tipos era Rockstars. Invaluables y… mal pagos. Bueno, según ellos. Artistas. Así que no es de extrañar esa necesidad de querer firmar la obra.

Vamos a repasar algunos easter eggs fomosos que tal vez ya nuestros lectores conozcan, o tal vez no. En cualquier caso, siempre es divertido encender alguna de estas máquinas de 40 años y ver que todavía siguen ahí. Y esto las hace un poquito mas humanas… ¿no les parece?

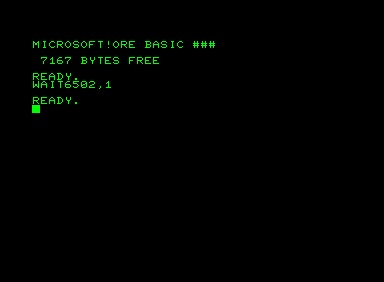

Microsoft!

Cuenta la historia que Jack Tramiel, fundador de Commodore, en una maniobra (y canchereada a lo “che pibe”) le dijo a Bill Gates “yo ya me casé una vez” cuando éste le propuso la idea de que el interprete BASIC que le había vendido para sus nuevas microcomputadoras PET lo usaran bajo el modelo de licencias. Pero Jack ya había pagado una vez y no quería atarse a nadie. Bill entonces, previendo un posible juicio donde tuviese que demostrar autoría, dejó escondido dentro del código de su interprete la palabra “Microsoft!”. El comando mágico es

WAIT 6502,x

…donde X es la cantidad de veces que se escribe.

Claro que luego los ingenieros de Commodore lo descubrieron (Bill no se contuvo y lo escribió en una CES…) y lo eliminaron; pero si aún tienen acceso a una de las primeras PET, Billy sigue saliéndose con la suya.

Corolario: cuando Commodore necesitó un nuevo BASIC para la flamante y pronto a estrenarse Amiga… bueno digamos que por eso es que en la pantalla de la contemporánea C128 tuvieron que poner “BASIC 7.0 (c)1977 Microsoft Corp.” Pero Jack ya no estaba.

Software y Herdware

Ya que mencionamos la Commodore 128, los ingenieros que participaron en su desarrollo también quisieron dejar su marca. Bueno. Es que se había puesto de moda. Dentro de los gabinetes de las “súper avanzadas” Apple Macintosh (1984) y Commodore Amiga (1985) podemos ver inmortalizadas en el plástico las firma de los artistas que las crearon. Cada plataforma que salia al mercado era un sistema completamente nuevo al cual había que inventarle todo, esto requería de trabajo en equipo. Y mucho esfuerzo. Así que había que dejar la huella.

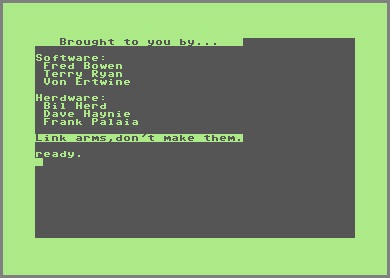

El comando mágico es entonces:

SYS 32800,123,45,6

… y aquí podemos ver quienes fueron los encargados del Software y quienes del Hardware o “herdware”, juego de palabras porque Bill Herd fue el encargado de liderar el equipo.

Pero ya lo habían hecho antes también. Si en la Commodore 16, Commodore 116 o Commodore Plus/4 (son básicamente la misma maquina en diferentes configuraciones) escribimos:

SYS 52651

… aparecerán los nombres de los involucrados.

Rebeldes

Como vimos al principio, los Easter Eggs no son solo una manera de firmar la obra. Sino también pretenden dejar un mensaje. A veces menos y a veces más explicito.

Terminando este artículo (que podría volverse infinito), me pareció muy emblemático el caso de la Amiga 500 (1987).

Commodore era una empresa que tras la renuncia de Jack Tramiel se volvió algo caótica. Cuando los ingenieros terminaron el desarrollo del Amiga, tenían en sus manos la computadora de consumo masivo (léase “hogareña” o “personal”) más poderosa del momento. Pero fue un fracaso en ventas, principalmente porque la gente de Marketing (al menos la gente de marketing de USA, aclaremos), no supo venderla. Eran áreas que estaban muy desconectadas entre si, lo que trajo mucha rivalidad interna y frustración en los desarrolladores.

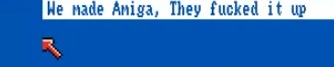

Así que para la salida de la Amiga 500 nuestros enojados amigos dejaron en ROM (Kickstart 1.2) lo siguiente: Al presionar ambas teclas ALT, ambas teclas SHIFT, y las teclas de función obtenemos los siguientes mensajes en la barra de menu:

… + F1 : “System Software: Carl, Neil & Kodiak”

… + F2: “Graphics Software: Dale, Bart, Jim & :RJ:

… + F3: “QA: Jon, Bruce, Stan, Kim & Jerry

… + F4: “LG Support: Caryn, Dave, Victor, Terry, Cheryl & Nancy”

… + F5: “CBM Software: Andy, Barry, Dave & Eric”

… + F6: “Pics: Sheryl & Jack”

… + F7: “Docs: Rick, Mitch, Peggy & Rob”

… + F8: “Chips: Jay, Akio, Glenn, Edwin, Mark & Dave”

… + F9: “HW: Dave, Bill, ChrisR & Josh”

… + F10: “Me Made Amiga, They fucked it up.”

Wow.

Cuando Commodore descubrió ese ultimo, imagínense que no les resultó nada gracioso, porque si bien la combinación de teclas es algo … digamos … complicada, no es tan difícil que se dé, así que pidieron que se remueva.

Pero lejos de hacerlo, solo lo escondieron más. En las siguientes revisiones del ROM, con F10 podíamos leer: “Moral Support: Joe Pillow & The Dancing Fools” (la explicación de estos personajes requiere un artículo aparte)

Pero si presionamos la combinación antes citada con F1 y quitamos el diskette del drive interno, aparecerá el mensaje “The Amiga, Born a Champion”.

Pero esto no es todo. Si luego, sin soltar nada, presionamos el botón izquierdo del mouse y volvemos a introducir el disquette, vuelve a aparecer “We made Amiga…”

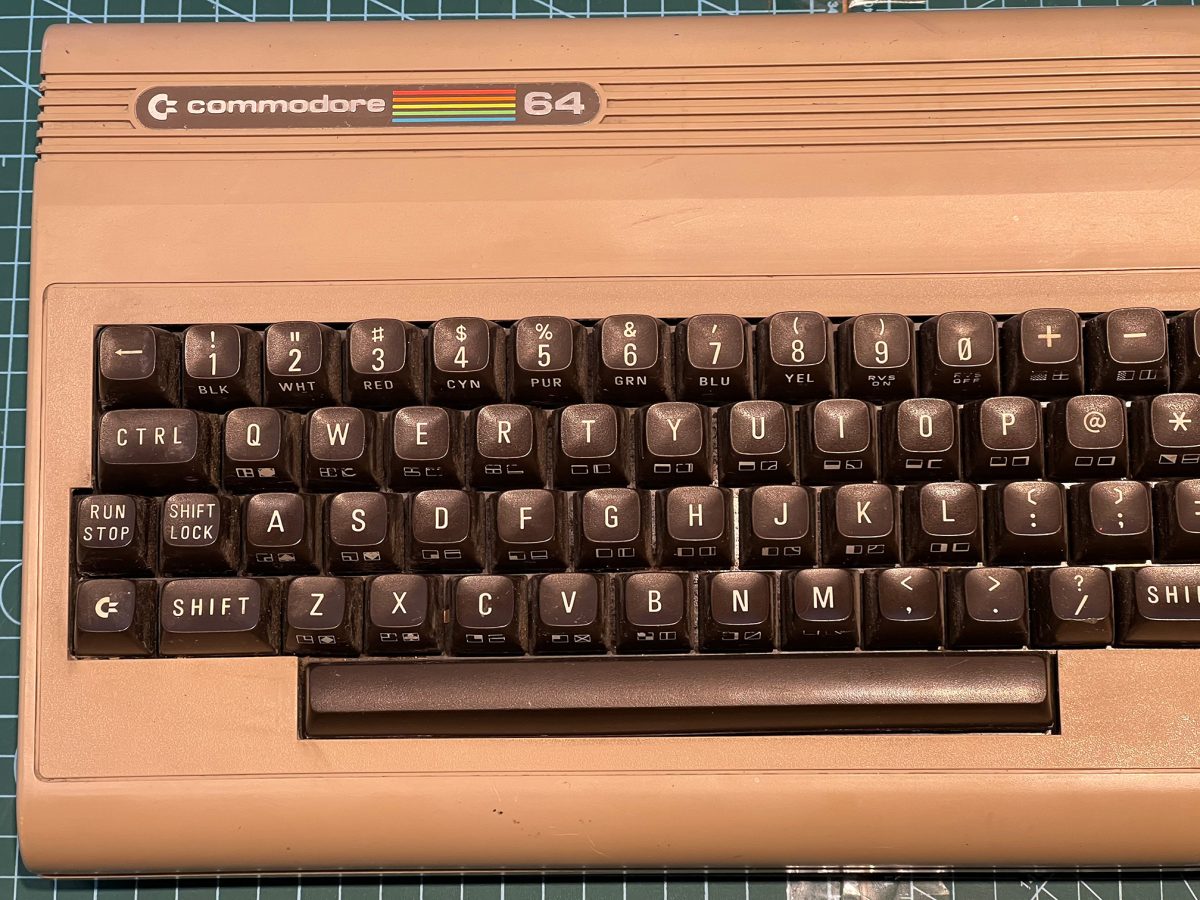

Los Chiches de la Commodore 64 – Ep 1 – El Reset Jabonera

En esta ocasión vamos a estudiar a un gran amigo que nos dejó excelentes recuerdos a la hora de obtener vidas infinitas en nuestros videojuegos, El Reset o Jabonera.

Vamos a estudiar que hacía, como funciona por dentro, que circuitos tenía y cómo lograr poner vidas infinitas en alguno de nuestros videojuegos favoritos.

Qué es el reset

El reset es un dispositivo que nos dejaba llamar al circuito de reset del procesador 6510 sin tener que apagar el mismo y sin la necesidad de borrar la memoria y comenzar desde cero. De esta forma podemos modificar posiciones de memoria con un programa cargado en la misma.

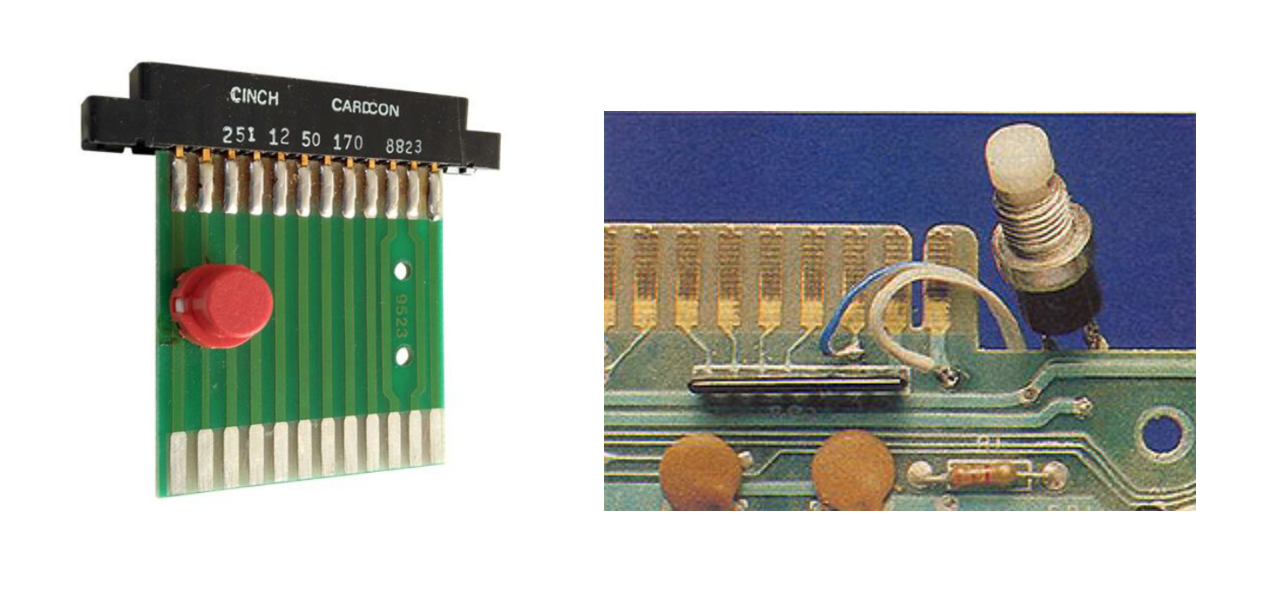

Su forma más típica es la de un cartucho blanco con un botón rojo que se conecta al puerto de usuario.

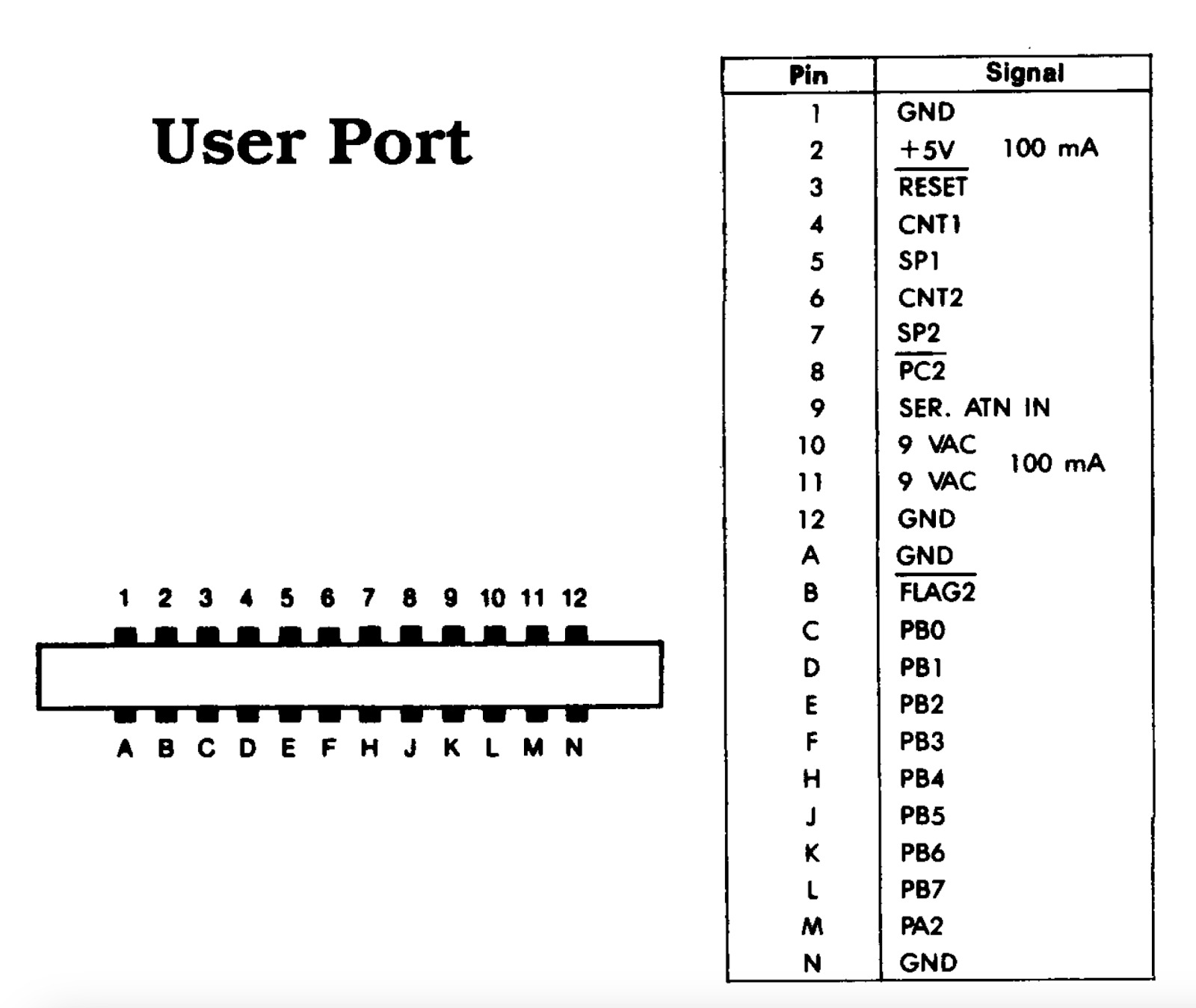

El puerto de usuario posee el siguiente pinout

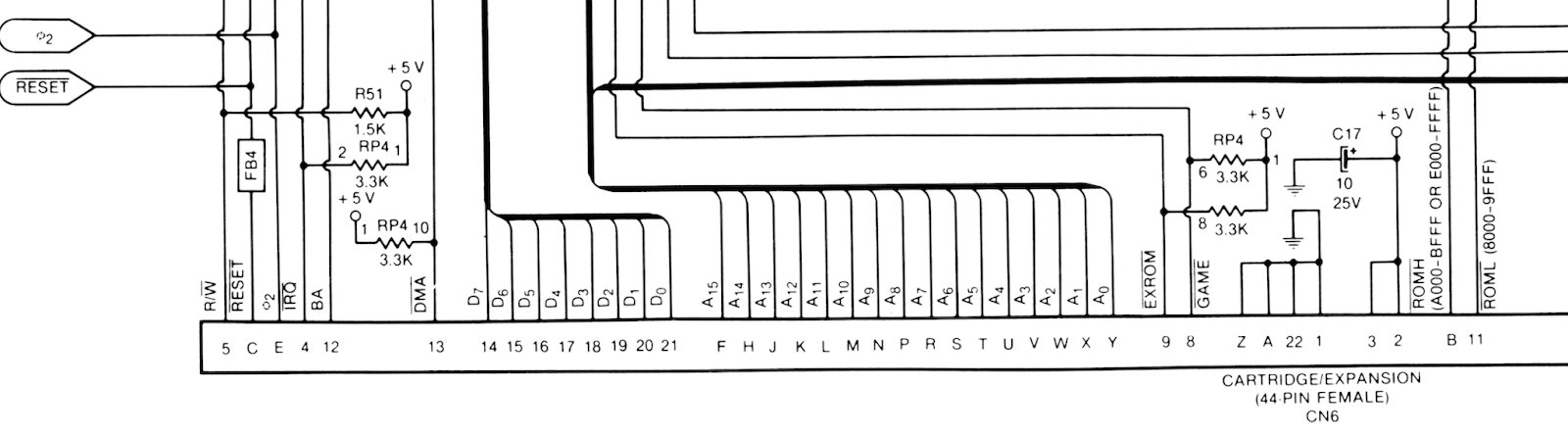

Estamos interesados en dos pines específicos el pin 12 de ground o tierra que nos va a poder dar valores LOW o cero y el PIN 3 o Reset. Algunos diseños también usan el pin 1, el pin N o el pin A como ground.

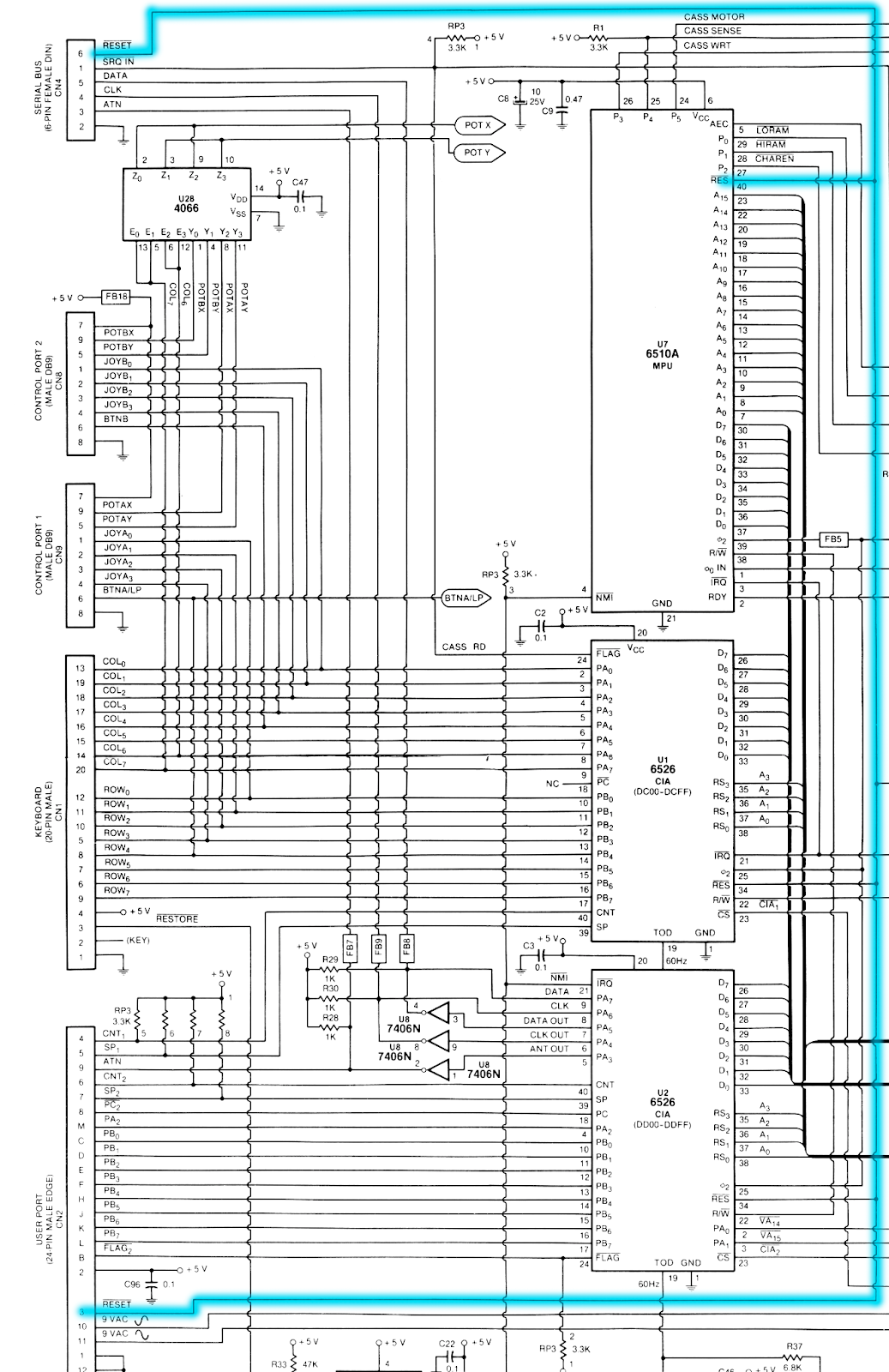

El PIN 3 está conectado a través del PCB del Commodore 64 directamente con el Pin 40 o de Reset del Procesador 6510. El Botón de reset activa el reset del procesador.

Así se ve la conexión de ambos resaltada en azul donde vemos la conexión del Pin 3 del puerto de usuario al pin 40 del procesador 6510. También existe otro modelo de reset que está conecta al puerto serial y hasta puede estar conectado en la disquetera.

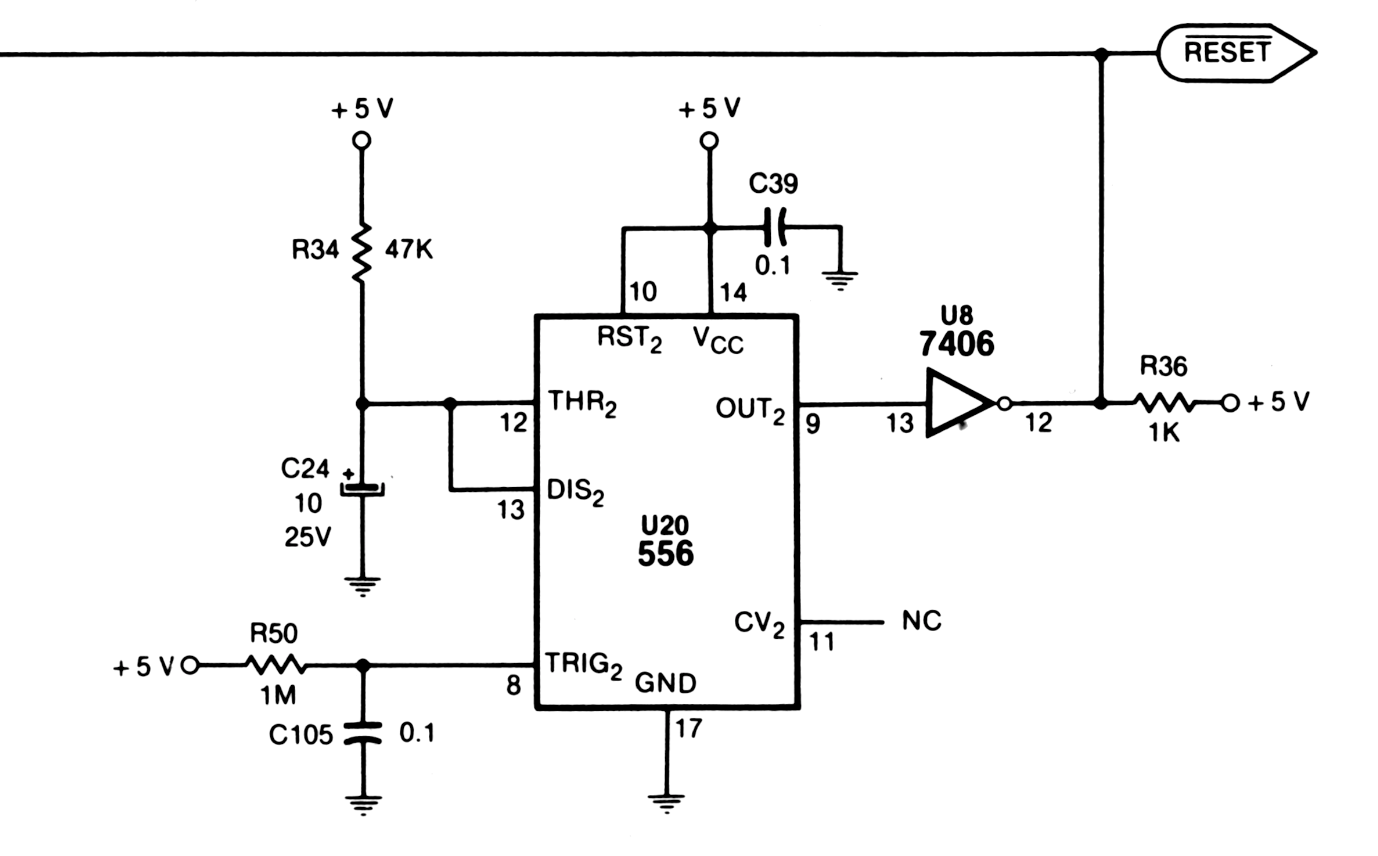

La línea de reset se mantiene en High cercano a los 5 Volts gracias a una resistencia de 1Kilo ohms que conecta la línea de reset con los 5 Volts del mother, en el diagrama R36.

Cómo funciona el reset internamente

El botón de reset internamente es un circuito que conecta el pin 3 de reset al pin 12 de ground a través de un botón de push que se encuentra normalmente abierto, al presionarlo y unirlo al pin 12 de ground hace que el pin 3 del user port conectado al pin 40 del procesador reciba un voltaje de low (menor a 0,4 Volts).

En esta foto podemos ver el pin 1 unido al pin 3 (recordar que una alternativa de pin de grund era el uno) y un botón para reset conectados a un placa que expande el puerto de usuario.

En nuestras latitudes (33 grados sur) hemos encontrado directamente cables soldados al botón y a los dos pines del user port de la mother lo que no solemos recomendar.

En nuestros pagos esta es la típica jabonera a la que estamos acostumbrados, la que conectamos al User port.

La misma posee un botón conectado a los pines 3 como reset y 12 como Ground a través de dos alambres.

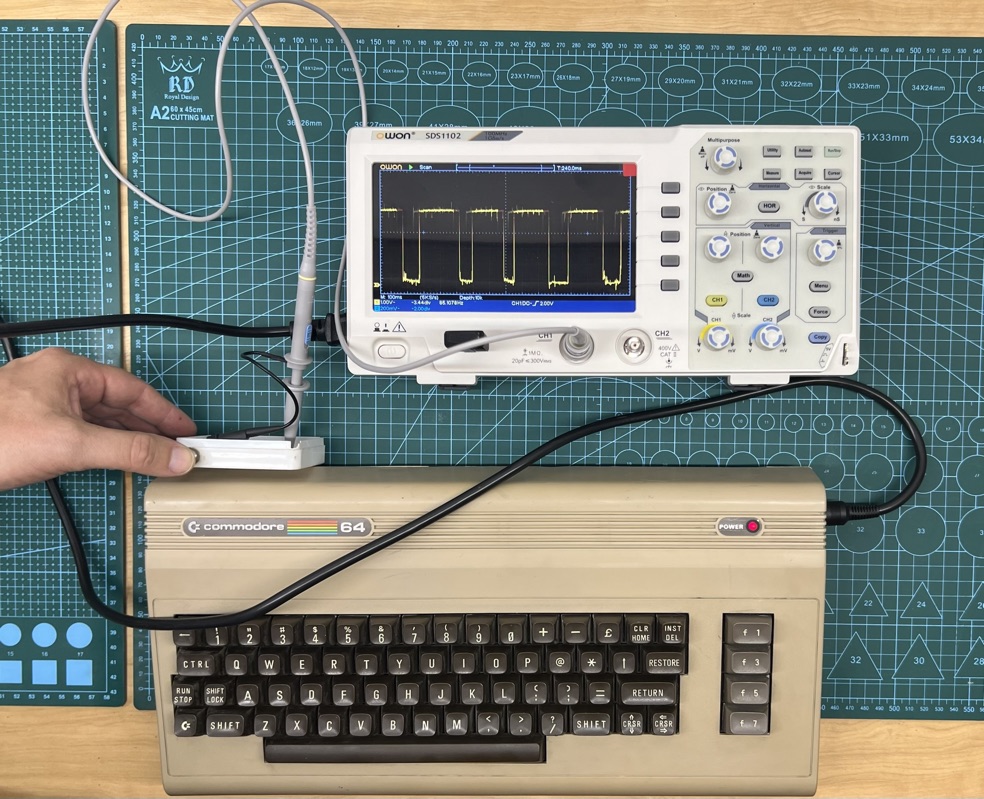

Si medimos con un osciloscopio cada vez que presionamos el reset vemos como la línea del reset conectada al pin 3 baja a 0 volts. En la imagen el probe o punta de testeo del osciloscopio está conectado al pin 3 de reset y el cable de ground al pin 12.

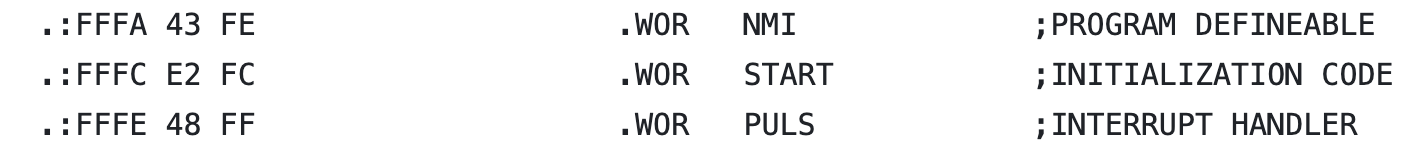

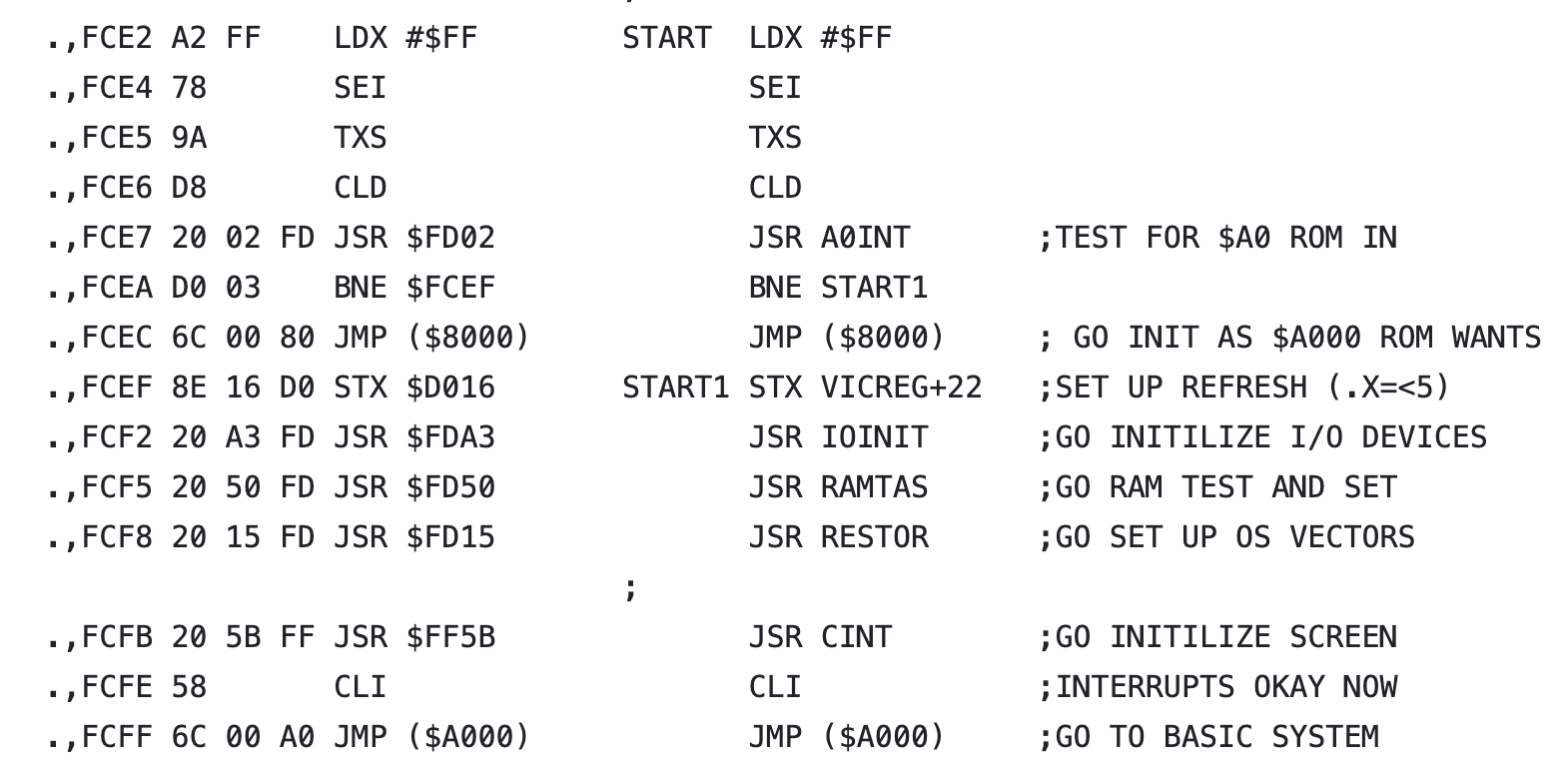

Al recibir un low en el pin 40 del procesador se activa la rutina de reset del 6510 que en este caso va hasta la posición de memoria $FFFC y $FFFD y se fija que dirección de memoria está aquí adentro y va a ejecutar ese programa.

En el caso de la Commodore 64 va a la rutina que está en la posición $FCE2 y ejecuta el siguiente programa:

Esta rutina inicializa la commodore sin borrar la memoria:

- Primero carga el valor $FF al registro X para luego configurar el stack pointer,

- Deshabilita las interrupciones prendiendo el flag de interrupciones,

- Configura el stack pointer en FF dejándole listo en $01FF,,

- Borra el flag de modo decimal del procesador,

- Se fija si existe algún cartucho con autostart y si existe este lo ejecuta (a partir de la posición $8000),

- Si no había cartucho llama a las rutinas de inicialización IOINIT (inicialización de dispositivos),, RAMTAS (inicilaiza y testea la RAM), RESTOR (configura los vectores como ser también el de reset $FFFCy $FFFD), y por último CINT que inicializa la pantalla,,

- Limpia el flag de interrupciones habilitándolas nuevamente y

- Arranca el programa de Basic a través de la posición de memoria $A000.

Finalmente vemos que nos deja en el prompt de basic pero con el programa que estuviera en memoria a la hora de pulsar el botón de reset todavía cargado en la misma.

¿Cómo lo usamos?

Primero cargamos un programa a memoria desde disco o cassette y ni bien este terminó de cargar pulsamos el botón de reset.

Si el programa que había en memoria es un programa en basic debemos antes de usarlo restaurar los punteros al código y memoria del mismo. Esto se realiza con los siguientes comandos.

(pO = p [Shift] o; pE = p [Shift] e) estas son las abreviaturas de poke para po y peek para pe

pO2050,8:sys42291:pO46,(pE(35)-pE(781)>253):pO45,pE(781)+2and255:clr

Luego de esto podemos correr el programa Basic, listarlo con LIST o grabarlo a disco.

Si lo que tenemos es un programa en código máquina, como por ejemplo un juego, podemos verlo con un monitor de código máquina o por si ejemplo si tenemos el wonderboy y queremos ponerle como truco vidas infinitas tipeamos los siguientes comandos desde el basic.

POKE 2676,238

SYS 2112

El comando Poke modifica la posición de memoria de las vidas y el comando SYS es una llamada a ejecutar el programa que está en la dirección 2112 que es el comienzo del juego.

Conclusión

Y de esta forma funciona nuestra querida Jabonera que tanto hemos usado para poder interrumpir alguno que otro videojuego y ahora sí ,con vidas infinitas, poder terminarlo. Un circuito muy simple y uno de nuestros clásicos chiches de Commodore.

Estudio visual

Para poder estudiar visualmente cómo funciona el Reset Jabonera, les dejo este video que complementa al artículo.

Referencias

A continuación les dejo algunos links donde profundizar el tema:

VIDEOS

El Reset Jabonera – Lo Chiches de la Commodore 64 Parte 1

Aquí tiene acceso a toda la serie de videos:

Artículos

Aquí encuentran todos los Artículos sobre Los Chiches de la Commodore:

PAPERS

Esquema del Mother parte Izquierda Commodore 64

Esquema del Mother parte Derecha Commodore 64

Wonder Boy Cheats, Codes, and Secrets for Commodore 64 – GameFAQs

Todos los ejemplos de código de los videos los pueden encontrar en:

C64 a Fondo – 6502 vs 6510 Episodio 9 – 6502 con Display LCD

Continuamos este estudio comparativo del 6502 vs el 6510 conectando un LCD de 16 caracteres x 2 líneas y programándolo con un mensaje. Vamos a estudiar cómo conectar un VIA 6522 y un CIA 6526 al lcd HD4470U de Hitachi y utilizando nuestro 6502 y nuestro 6510 mostrar el texto “OsoLabs” en el display en dos maquetas breadboard simultáneas.

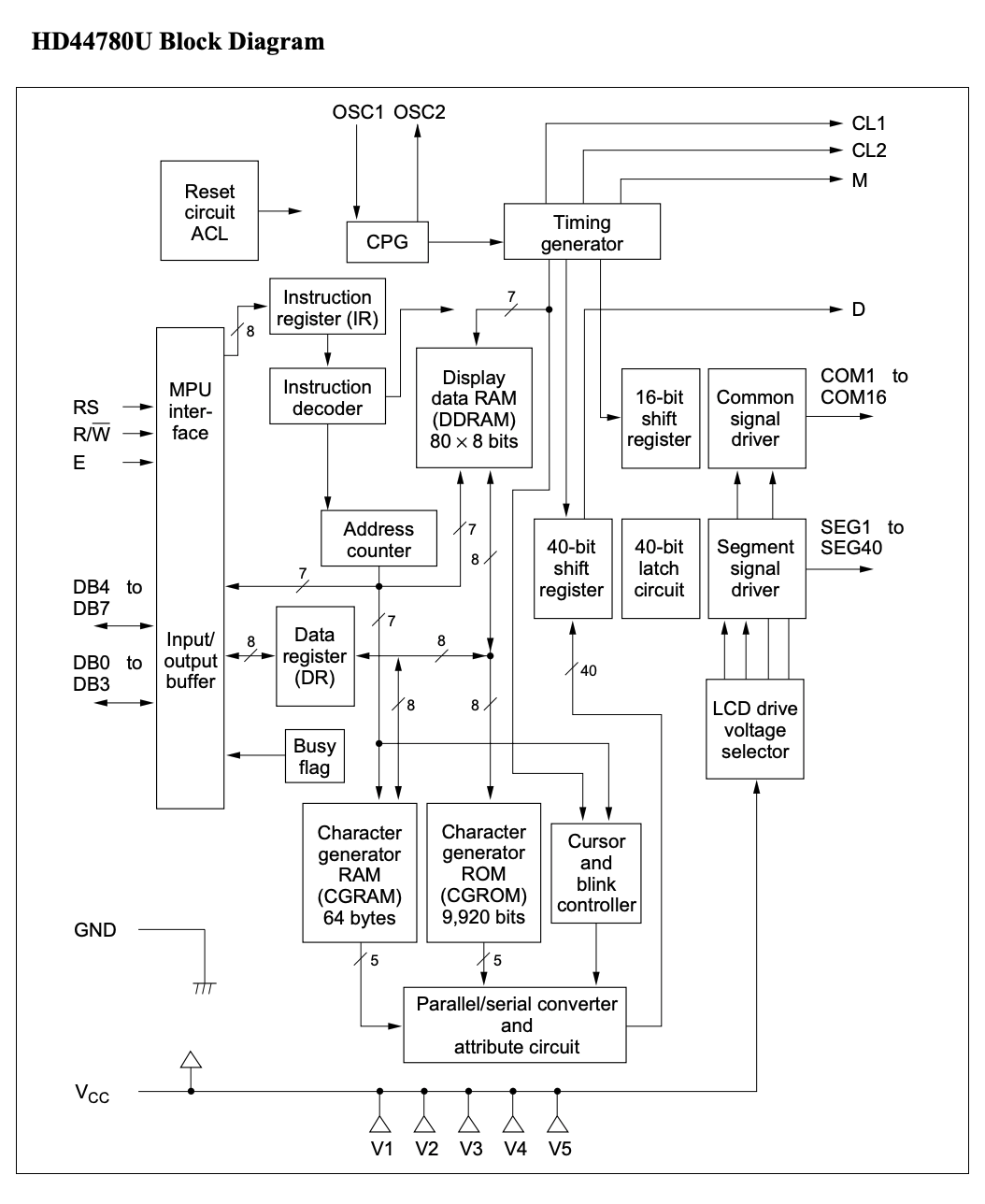

El LCD Hitachi HD44780U

Nuestro principal display es el LCD de Hitachi el mismo posee el siguiente diagrama esquemático.

Este LCD tiene 16 caracteres que se pueden mostrar en dos líneas y cada carácter puede ser de 5×8 o 5×10 puntos. Posee internamente el dibujo o font de varios tipos de caracteres que se eligen con valores correspondientes mayormente al ASCII. Estos caracteres incluyen el alfabeto tradicional, caracteres japoneses y símbolos. El LCD puede ser controlado por un procesador de 4 bits o uno de 8 bits, nosotros lo utilizaremos en modo 8 bits por estar usando la línea 6502/6510.

En cuanto a velocidad es compatible con un bus de datos de hasta 2Mhz, nosotros vamos a estar utilizando hasta 1Mhz el máximo de velocidad de nuestro 6510.

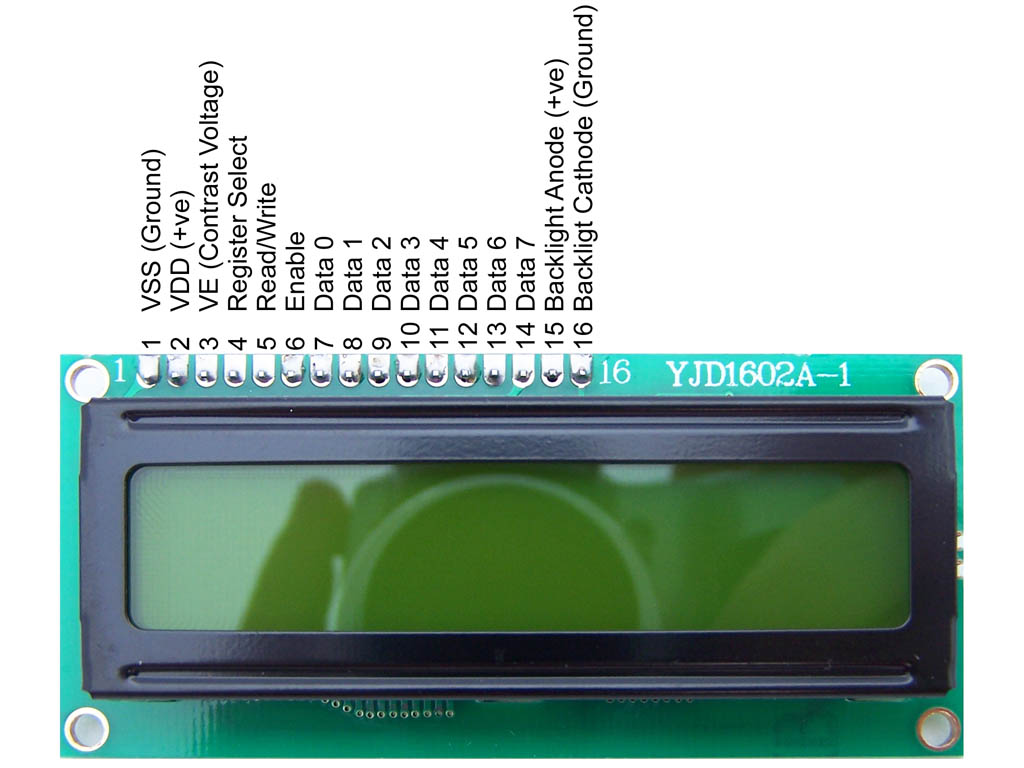

PinOut del LCD

El siguiente esquema muestra y explica el pin-out

VSS (Ground): conexión a tierra de nuestro LCD

VDD: conexión a 5 Volts +

VE: Pin de contraste, se conecta normalmente a un potenciómetro en su pin de polo y el otro pin va directo a tierra.

Register Select RS: Nos permite elegir si escribir al Instruction Register usando el valor 0 o al Data Register usando el valor 1

Read/Write : Permite escribir si el valor es cero y leer si el valor es 1

Enable: Comienza la lectura o escritura sacando los pines DB7 a DB0 de su modo de triestado.

DB7 a DB0: Bus datos para escribir o leer. En el modo de operación de 4 bits sólo se usando los pines DB7 a DB4

A : Ánodo (pin positivo +5 Volts) para encender la luz de backlight

K: Cátodo (pin negativo 0 Volts) para encender la luz de backlight

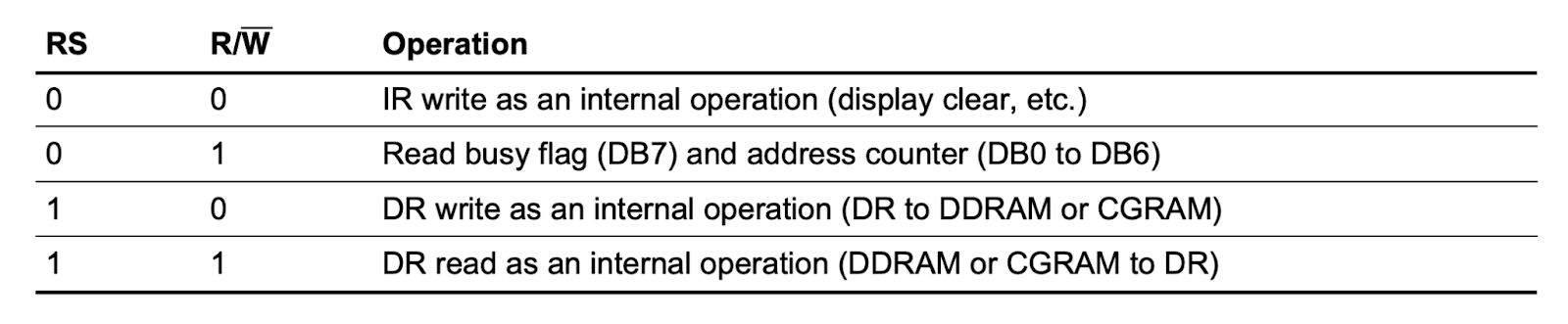

Cómo leer y cómo escribir nuestro LCD

Hay tres pines que funcionan para poder leer o escribir los registros internos y la pantalla de nuestro LCD, estos son RS, RW y E. En la siguiente Tabla especificamos cómo realizar cada operación.

RS = 0 /R/W = 0 E=1 permiten enviar una instrucción al LCD, escribiendo el instruction register

RS = 1 /R/W = 0 E=1 permiten enviar datos al LCD, escribiendo el data register.

Generalmente el valor del pin Enable se usa como un Toggle o pulso y este se dispara cuando ya tengo todos los datos de los demás pines (RS, RW y DB7 a DB0) estables y con valores correctos.

Instrucciones internas del LCD

El LCD posee instrucciones internas que sirven para desde limpiar la pantalla o elegir el ancho de los caracteres hasta encender o apagar el display, las mismas estan explicadas en la siguiente tabla:

El formato de estas instrucciones es:

Valor del pin RS,

Valor del pin /R/W,

Una cantidad de ceros y luego un 1 para identificar la instrucción en los pines DB7 a DB0,

El resto después del 1 que identifica la instrucción, son los parámetros de la misma.

Por ejemplo la instrucción Display on/off control que controla tres funciones de nuestros display está codificada de la siguiente forma:

| RS | /R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | D | C | B |

El valor RS es cero para indicar que estamos escribiendo al instruction register del LCD

El valor /R/W es cero para indicar que es una escritura

La instrucción está indicada por los pines DB7 a DB3 y es 00001

El pin DB2 es un parámetro que indica si prender o apagar el display

El pin DB1 es un parámetro que indica si está prendido o no el cursor

El pin DB0 es un parámetro que indica si el cursor parpadea o no

Si quisiéramos que el display esté prendido, mostrando el cursor y que este no parpadee enviaríamos la siguiente secuencia

| RS | /R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

Inicializar nuestro LCD

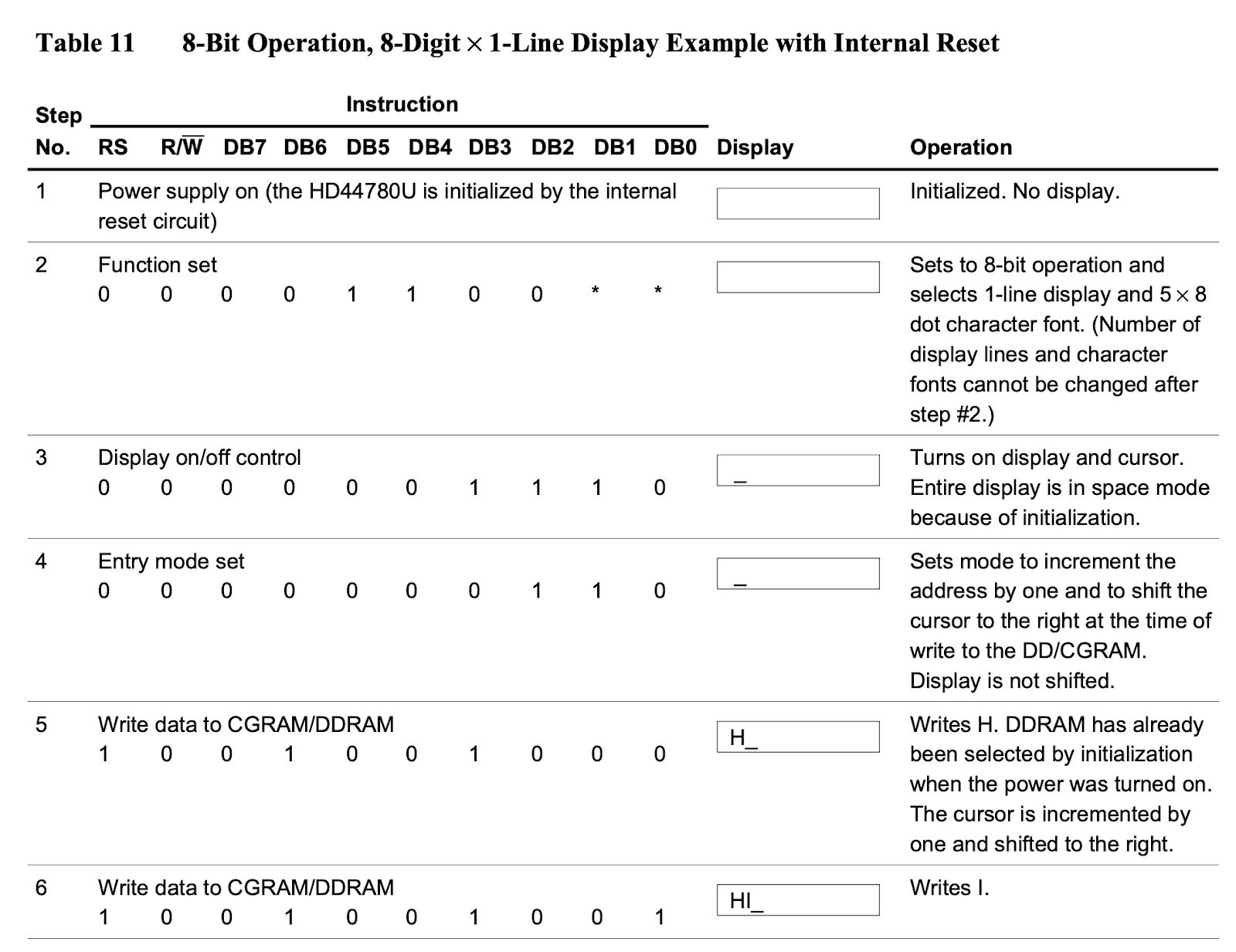

Para poder empezar a enviar letras a nuestro LCD primero debemos inicializarlo, el datasheet nos indica una secuencia de inicialización que vamos a analizar.

El primer paso es conectar al suministro eléctrico de 5 volts a nuestro LCD, para esto no necesitamos ninguna instrucción solo conectar correctamente los cables.

El segundo paso es enviar la instrucción Function Set que en este caso elige la operación del display como 8 bits (usa todos los pines de DB7 a DB0), una sóla línea y formas de caracteres de 5×8 puntos.

| RS | /R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | N/A | N/A |

El tercer paso es enviar la instrucción Display on/off control donde indicamos prender el display, mostrar el curso y que este no parpadee.

| RS | /R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

El cuarto paso y último paso en la inicialización es enviar la instrucción Entry Mode Set para decidir cómo es que vamos a mostrar los caracteres en este caso decidimos que después de mostrar una letra corra el cursor un lugar a la derecha

| RS | /R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

Finalmente ya estamos listos para escribir nuestra primera letra.

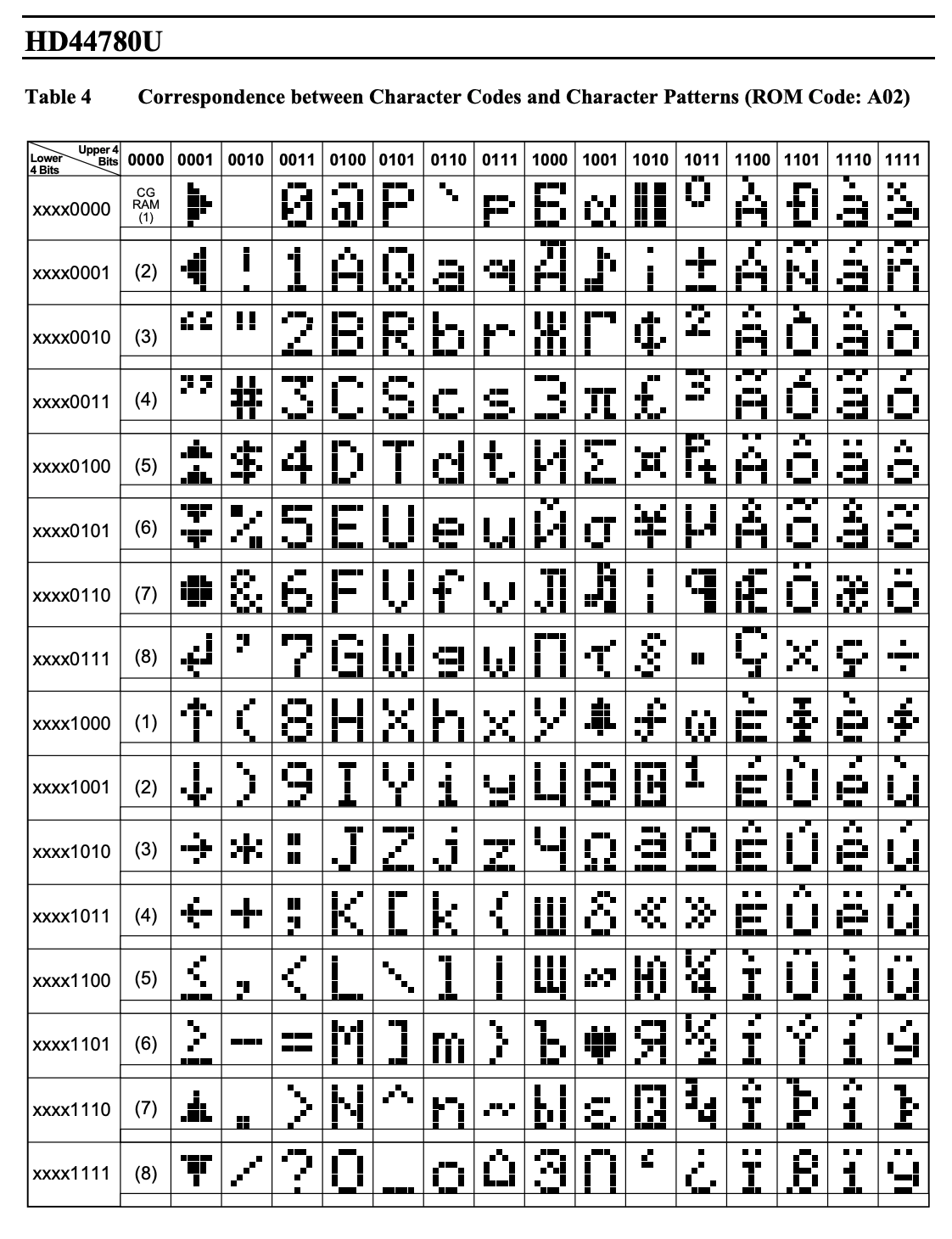

Escribiendo una letra en nuestro LCD

Al tener preparado ya nuestro LCD para recibir nuestra primera letra, el mismo espera la información en código ascii explicitado en los pines del DB7 al DB0 por ejemplo, a continuación la tabla de caracteres del lcd.

Para escribir la letra H mayúscula por ejemplo vemos que la combinación es 0100 1000 com lo que deberemos enviar estos valores:

| RS | /R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| 1 | 0 | 0 | 01 | 0 | 0 | 1 | 0 | 0 | 0 |

El valor RS es 1 para indicar que estamos escribiendo al data register del LCD

El valor /R/W es 0 para indicar que es una escritura

En los pines DB7 a DB0 espera el dato a escribir en memoria y es 01001000

Cómo funciona el CIA en la Commodore 64

La Commodore 64 posee dos CIA 6526 pero ninguno está conectado a un LCD, utilizando al chip VIC2 y un modulador de RF la Commodore puede comunicarse con monitores con su salida de video y a televisores con su salida RF, en una futura entrega vamos a desarrollar el funcionamiento del chip VIC2.

Estudio visual

Para poder estudiar visualmente como conectar el LCD a nuestros procesadores y CIAs/VIAs y como programarlo en assembler para mostrar un mensaje les dejo esta video que complementa al artículo.

LCD con 6510/CIA y 6502/VIA – 6502 vs 6510 Parte 9

Referencias

A continuación les dejo algunos links donde profundizar el tema:

VIDEOS

Video de la serie 6502 vs 6510 Parte 9 – LCD con 6510/CIA y 6502/VIA

LCD con 6510/CIA y 6502/VIA – 6502 vs 6510 Parte 9

Aquí tienen acceso a toda la serie:

6502 vs 6510 estudio detallado y comparación

Aqui tienen acceso a todos los artículos publicados en Espacio Tec

Artículos en la serie C64 a Fondo

A continuación les dejo los links a los artículos anteriores de la serie

Parte 3 – Codeando a Mano la Primera Instrucción de Código Máquina

Parte 4 – Primer Programa desde EEPROM

Parte 5 – I/O Pins del Procesador

Parte 7 – VIA MOS 652 Interfaz con periféricos

Parte 8 – MOS 6526 CIA Interfaz con periféricos reloaded

PAPERS

HD44780U (LCD-II), (Dot Matrix Liquid Crystal Display Controller/Driver)

Y como siempre la serie de Ben Eater del 6502

Build a 6502 computer | Ben Eater

Todos los ejemplos de código de los videos los pueden encontrar en:

C64 a Fondo – 6502 vs 6510 Parte 8 – MOS 6526 CIA Interfaz con periféricos reloaded

Hola, en esta entrega vamos a estudiar el MOS 6526 también conocido como CIA o complex adapter interface. Son los famosos chips que usa la Commodore 64 entre el procesador y el teclado, ports de usuario y ports de joystick (control port 1 y 2) entre otras conexiones.

¿Por qué necesito algo entre el cpu 6510 y un periférico?

Los procesadores tienen como características ser muy rápidos, estamos hablando de 1 millón de operaciones o ciclos de reloj por segundo en el caso del 6510. Un periférico como el datasette o la disquetera está en el orden de 300 bytes por segundo de transferencia.

Si el procesador tuviera que esperar cada acceso de información disponible sería toda la computadora extremadamente lenta, por eso ponemos un chip en el medio para que medie entre el procesador y los periféricos.

Este chip tiene como función recibir la información que el 6510 le envía, mantenerla disponible y pasarla al periférico cuando este la requiera; también recibir la información desde el periférico, mantenerla y avisar al procesador que tiene información disponible para él. De esta forma el bus de datos se mantiene libre hasta que el procesador tenga que comunicarse con el periférico.

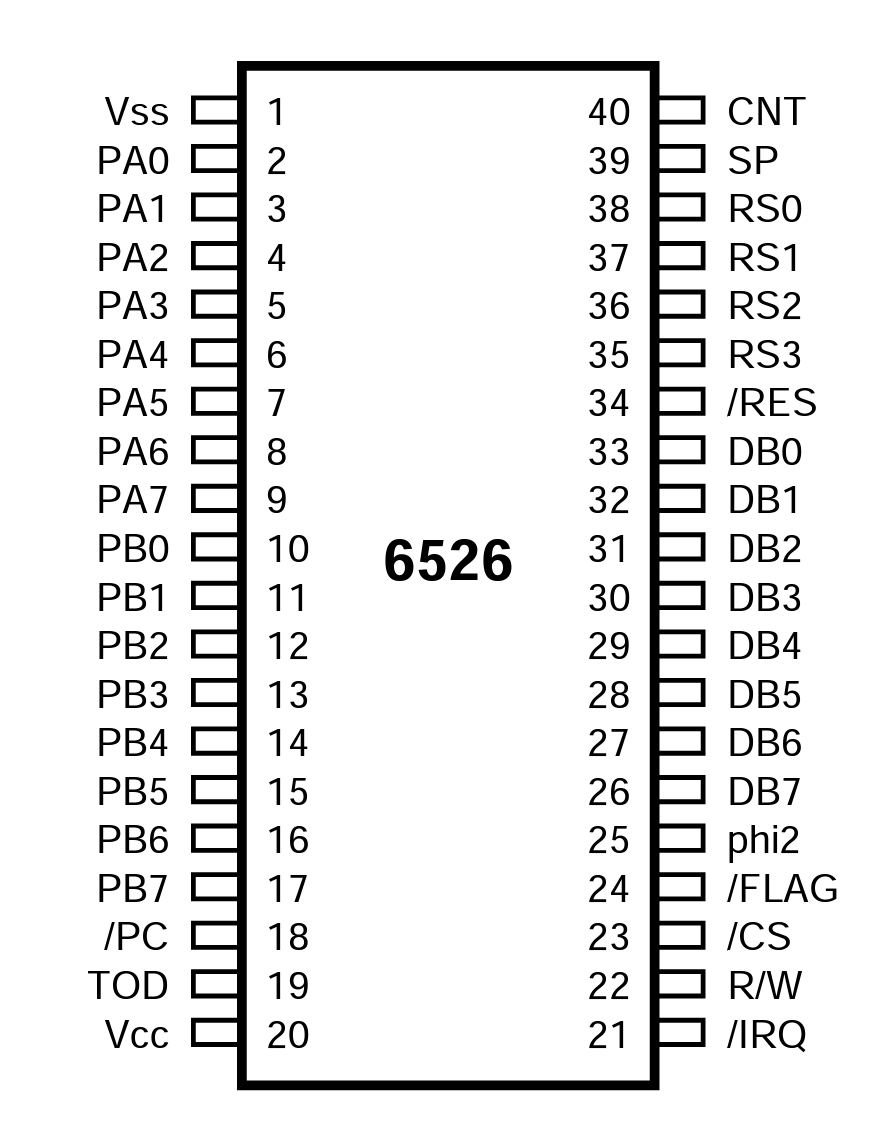

El CIA – Complex Interface Adapter MOS 6526

Pinout

Los pines, VCC, RS0 a RS3, /RES, DB0 a DB7, PHI2, R/W, /IRQ presentan funcionamientos similares al VIA MOS 6522, pero primero vamos a dar detalles de funcionamiento de los pines presentes sólo en el CIA. Cuando en el diagrama un puerto comienza con una / leer como BARRA y significa que este pin es Active Low.

/PC y /FLAG se utilizan juntos para realizar un handshake entre el procesador y el CIA, también el pin /FLAG sólo ,puede utilizarse para recibir una señal de otro 6526 y quedar marcado como flag de interrupción encadenando ambos CIA. El pin /PC es output y pin /FLAG es input siempre.

TOD este pin requiere una conexión externa de 60Hz o 50Hz con un nivel programable de TTL para mantener el reloj interno del CIA.

CNT puede recibir pulsos para usar como un contador en Timer A o Timer B o ser output y escribir pulsos del timer A o B.

SP Es un pin de input o output donde los BITS del puerto serial del chip son escritos. El Serial Data Register se conecta con el Shift Register y cuando recibe un pulso en el pin CNT hace un shift out del Shift Register un bit a la vez en el pin SP, esto lo hace por 8 pulsos o 8 bits del registro momento en el cual se genera una interrupción para avisar que se pueden enviar más datos.

/CS el CIA posee un sólo pin que funciona como Chip Select, al estar en Low el chip responde a los datos en DB0 a DB7

Aquí repasamos los pines con funcionamiento similar al VIA

VSS y VCC/VDD son los pines de Ground y 5 Volts respectivamente

PA0 a PA7 Port Address A: son pines de datos bidireccionales (input y output) para el primer puerto de periféricos el A, el periférico se comunica con el 6526 por esos pines.

PB0 a PB7 Port Address B: son pines de datos bidireccionales (input y output) para el segundo puerto de periféricos el B, el periférico se comunica con el 6526 por esos pines.

RS0 a RS3 son pines que permiten seleccionar qué registro interno del CIA se accede cuándo el procesador lee o escribe los puertos de datos D0 a D7

RESB puerto de reset, el 6526 necesita de un reset cuando el 6510 es prendido por primera vez o pasa por un reset, en este pin recibe la señal. (Active Low).

DB0 a DB7 Data Bus: en estos pines el procesador 6510 se comunica con el 6526 para leer o escribir datos y acceder a cualquiera de los registros internos del CIA.

PHI2 en este pin se recibe la señal de reloj que es la misma que tiene el 6510, al estar diseñado el 6526 para trabajar con estos procesadores todo el timing interno funciona coordinadamente con toda la línea 6500.

RWB en este pin específico, se indica si se está realizando una lectura (high) o una escritura (low) a los pines D0 a D7.

IRQB este pin cuando está en estado low crea una interrupción al procesador para que este tome información del puerto de periférico que corresponde.

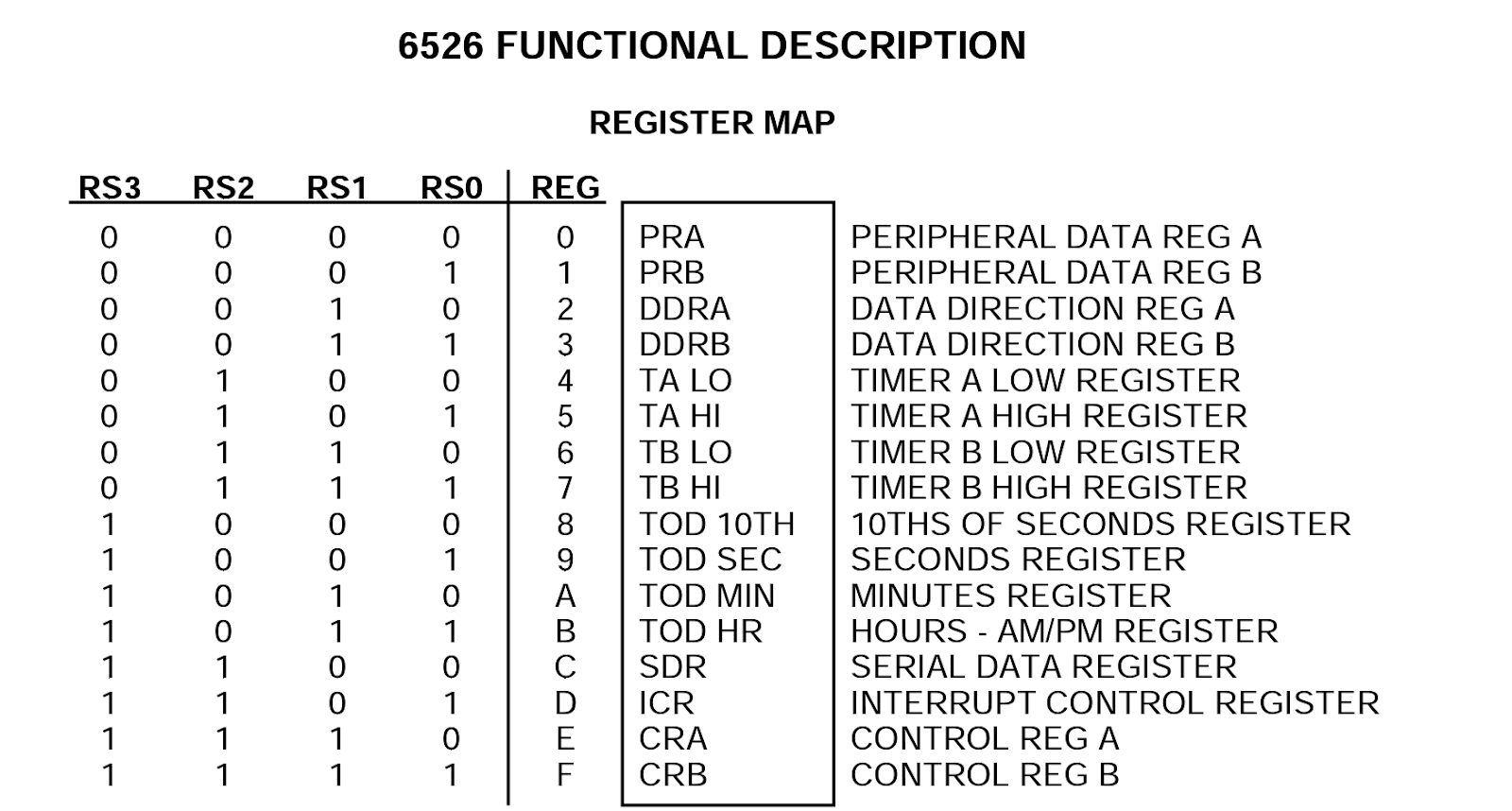

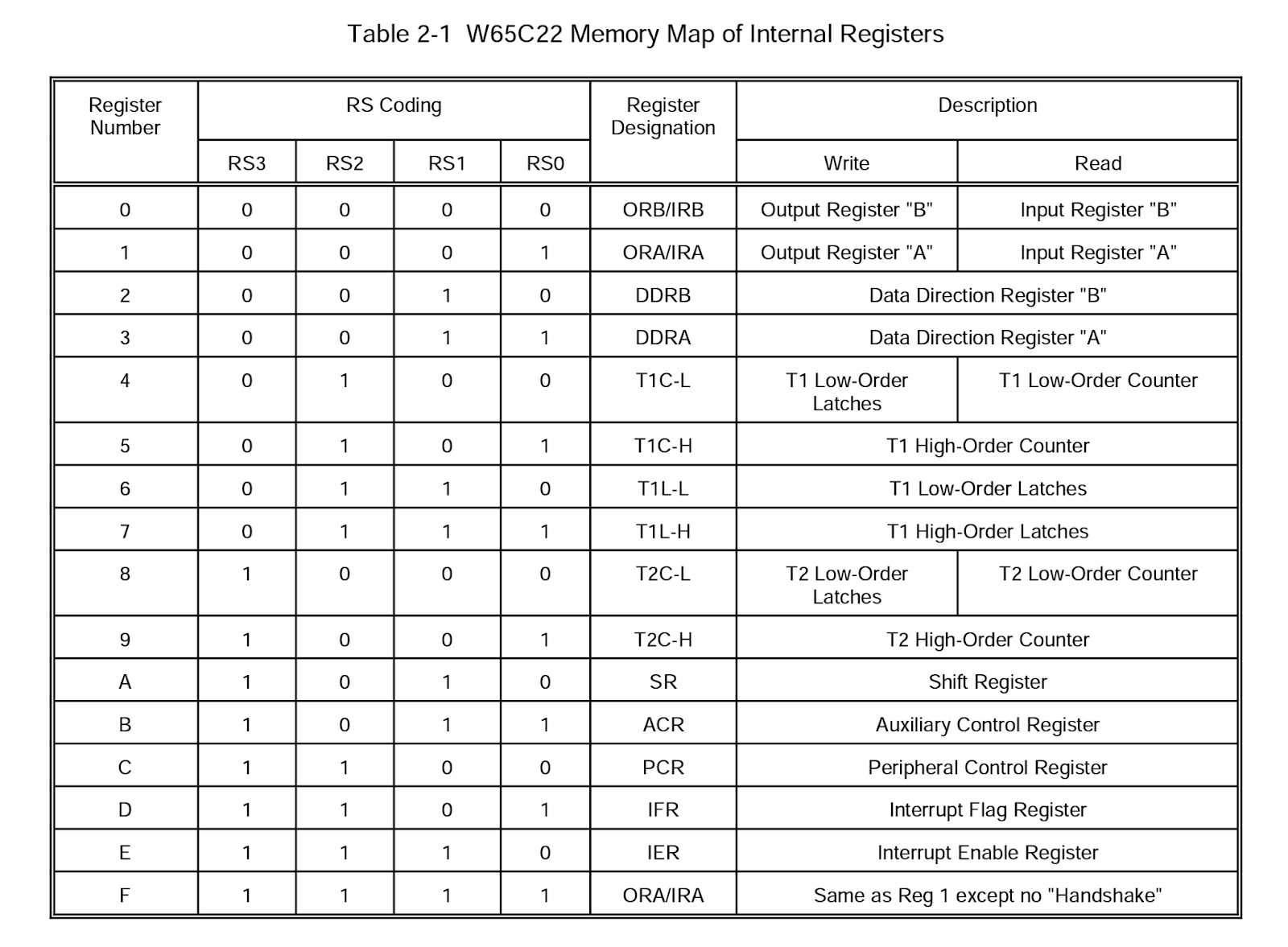

Registros

Los registros varían para reflejar la diferencia en algunas funciones con respecto al VIA que ya estudiamos, el CIA posee 16 registros diferentes aquí los detalles de algunos de ellos.

Este chip posee 16 registros internos que permiten entre otras funciones:

- Seleccionar si los pines del canal de datos son de input o output

- Almacenar la información que entrega o recibe el procesador de modo de mantener el canal de datos vacío pero la información preservada.

- Elegir si el CIA puede o no interrumpir al procesador cuando tiene información para entregar.

Si queremos usar por ejemplo los puertos del PB0 al PB7 como output para darle información al periférico debemos primero seleccionar el Data Direction Register B. El mismo se selecciona a través de los puertos RS0 a RS3 en este caso poniendo los pines con los valores de 0v o Ground (<0.4 volts) en caso de tener un 0 en la tabla siguiente o 5v en caso de tener un valor 1:

RS3= 0 RS2= 0 RS1= 1 RS0= 1

Esto corresponde con el valor 3 del Register Number (0011), nótese que es diferente al VIA que espera un valor de 0010 o sea de 2 para el data register B.

Luego de esta selección el procesador debe escribir el valor deseado a través de los pines D0 a D7. Para poner un pin en OUTPUT el valor deberá ser 1 y en INPUT deberá ser cero. Si quisiera poner todos los pines como output el procesador escribirá 1111 1111.

Luego el procesador debe enviar la información que quiere mandar de output al periférico para esto se utiliza el registro Output Register. En nuestro caso usaremos el Output Register B para seleccionarlo en los pines RS3 a RS0 poner los siguientes valores:

RS3= 0 RS2= 0 RS1= 0 RS0= 1

Que corresponden al valor de registro uno (0001), fijense que es diferente al valor usado en el VIA que era de cero (0000).

Si quisiera tener como valores de Salida en PB7 a PB0 los valores 10101010 debería escribir estos mismos en el registros enviando esta información por los pines D7 a D0.

Estos puertos soportan input latching, que es una característica por la cual el puerto conserva el valor de input que recibió desde el periférico aunque el mismo no refresque la señal. Los datos se mantienen (aunque cambien los valores en los pines PB0 a PB7) mientras el flag CB1 de interrupción este set y se borran cuando este flag es desactivado.

Handshaking

El CIA puede hacer handshaking usando el pin /PC como output y el /FLAG como input. /PC va a ir a valor cero o low por un ciclo de tiempo P después de una lectura o escritura del Puerto B. Esta señal puede usarse para indicar “data ready” en el puerto B o “data accepted” en el mismo puerto dependiendo si se trató de una lectura o una escritura respectivamente.

Se puede hacer handshake en transferencia de 16 bits usando ambos puertos A y B siempre leyendo o escribiendo primero al puerto A.

Cualquier señal low al pin /FLAG va a disparar una interrupción del bit FLAG, se puede usar como un puerto genérico para recibir interrupciones o se puede conectar al puerto /PC de otro CIA para recibir el low de ese pin y saber que sucedió un handshake en el puerto B de ese otro CIA (CIA 2 por ejemplo)

Timers

Los timers A y B del CIA pueden ser arrancados y parados a voluntad usando el control register A o el B respectivamente.

Reloj

También como funciones adicionales presenta un reloj Time of Day (TOD). El TOD es un reloj de 24 horas con una graduación de una décima de segundo. Está organizado en 4 registros (que se seleccionan con los pines RS0 a RS3), décimas de segundo, segundos, minutos y horas. El mismo necesita en el pin TOD la conexión con un clock de 60 Hz o 50 Hz.

Contador

Otra función adicional es contar los pulsos del pin de reloj recibidos en PHI2 en TIMER A o TIMER B o los pulsos recibidos en el pin CNT.

Puerto Serial (Shift Register)

El CIA también posee un puerto serial sincrónico de 8 bits con un buffer de 8 bits. Un bit de control selecciona si se va a recibir un input o output.

En modo input los datos recibidos en el pin SP se ingresan a un shift register cuando se recibe una transición de low a high en el pin CNT. Luego de 8 CNT los datos en el shift register se copian al Serial Data Register y una interrupción es generada. El procesador va a leer los 8 bits contenidos en el Serial Data Register a través de los pines D0 a D7.

En modo output el TIMER A se usa como generador de baudios. Los datos se envían por el pin de SP. La tasa máxima de transferencia en baudios es PHI2 dividido por 4. La transmisión va a empezar después de escribir al Serial Data Register, la señal del TIMER A aparece como pulsos de output en el pin CNT y los datos se escriben al Shift Register y luego saldrán uno a uno por el pin SP cuando un pulso CNT ocurra. Luego de 8 pulsos CNT se genera una interrupción para indicar que se pueden mandar más datos.

Si el procesador carga datos en el Serial Data Register antes de que se produzca la interrupción cuando esta se produzca y se transmitan los datos el Shift Register va a ser cargado automáticamente luego de la transmisión. Si el procesador se mantiene en forma constante 1 byte adelantado al consumo del Shift Register la transmisión será continua.

Los datos son transmitidos con el Most Significant Bit primero.

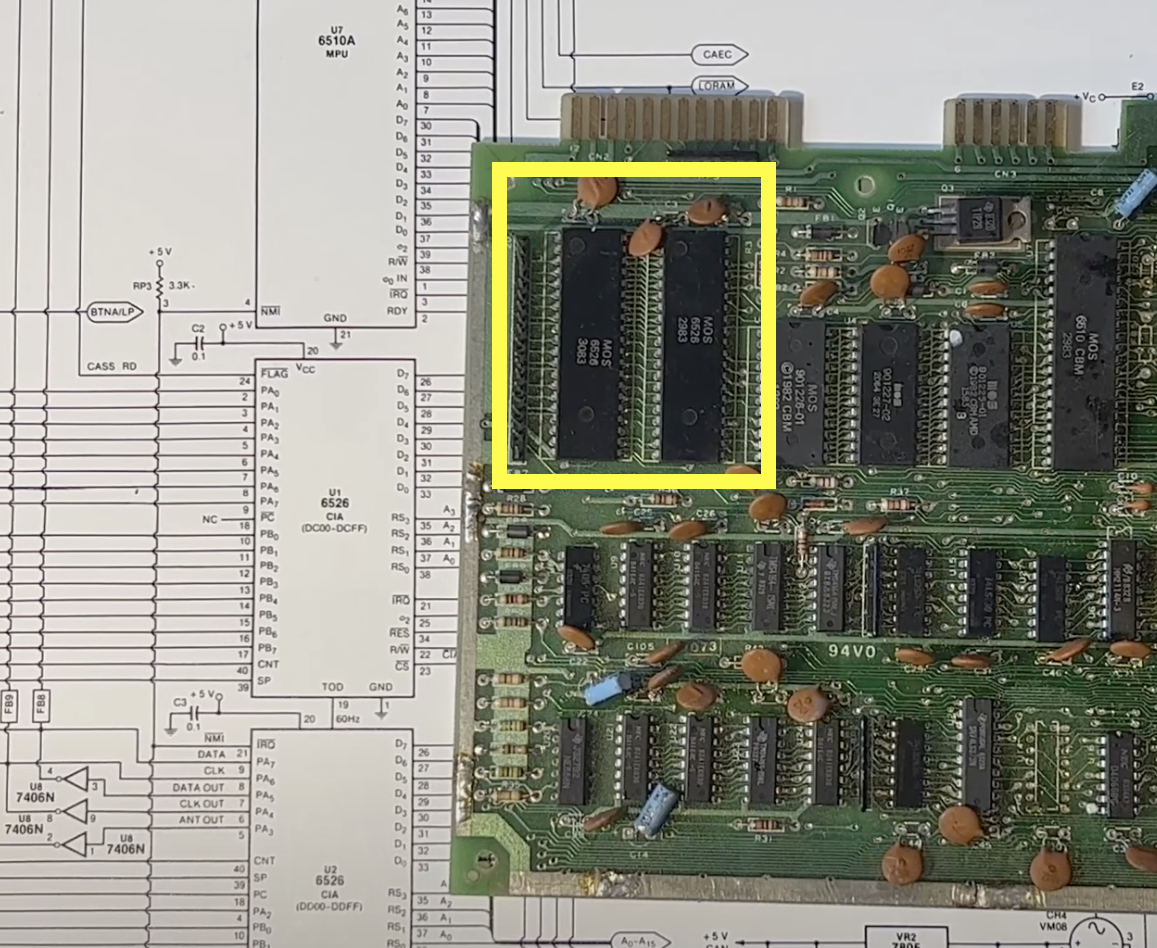

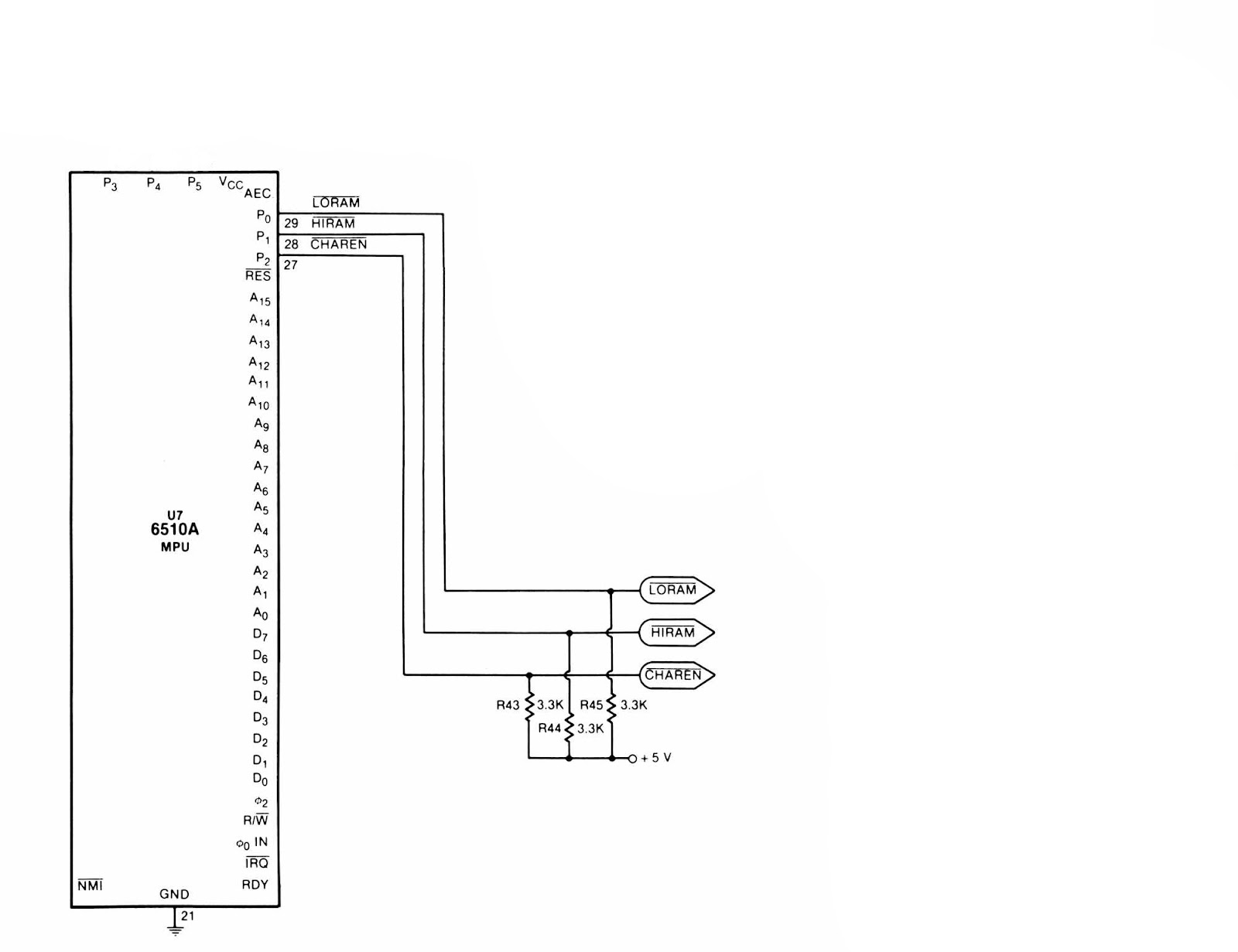

Cómo funciona el CIA en la Commodore 64

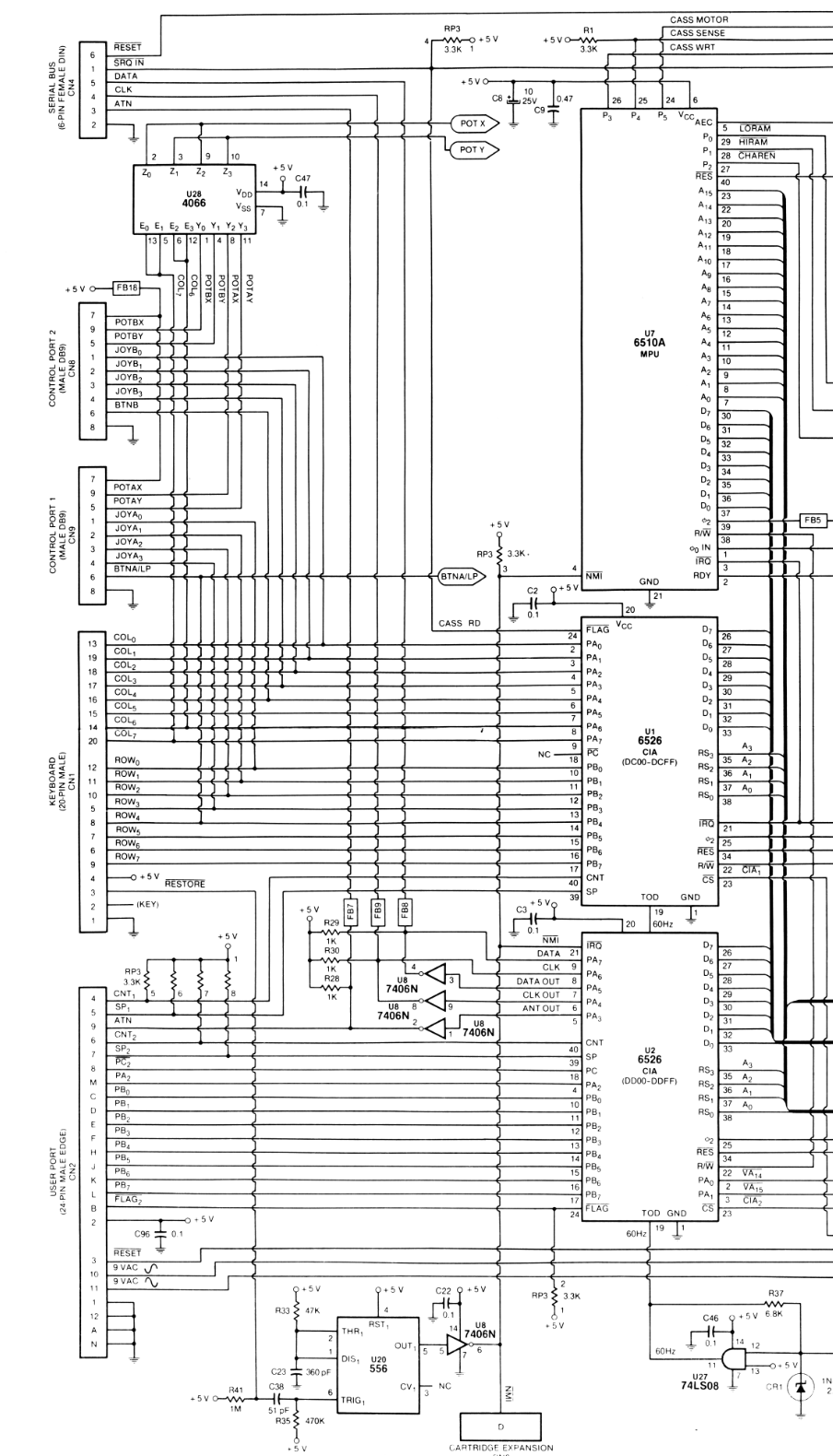

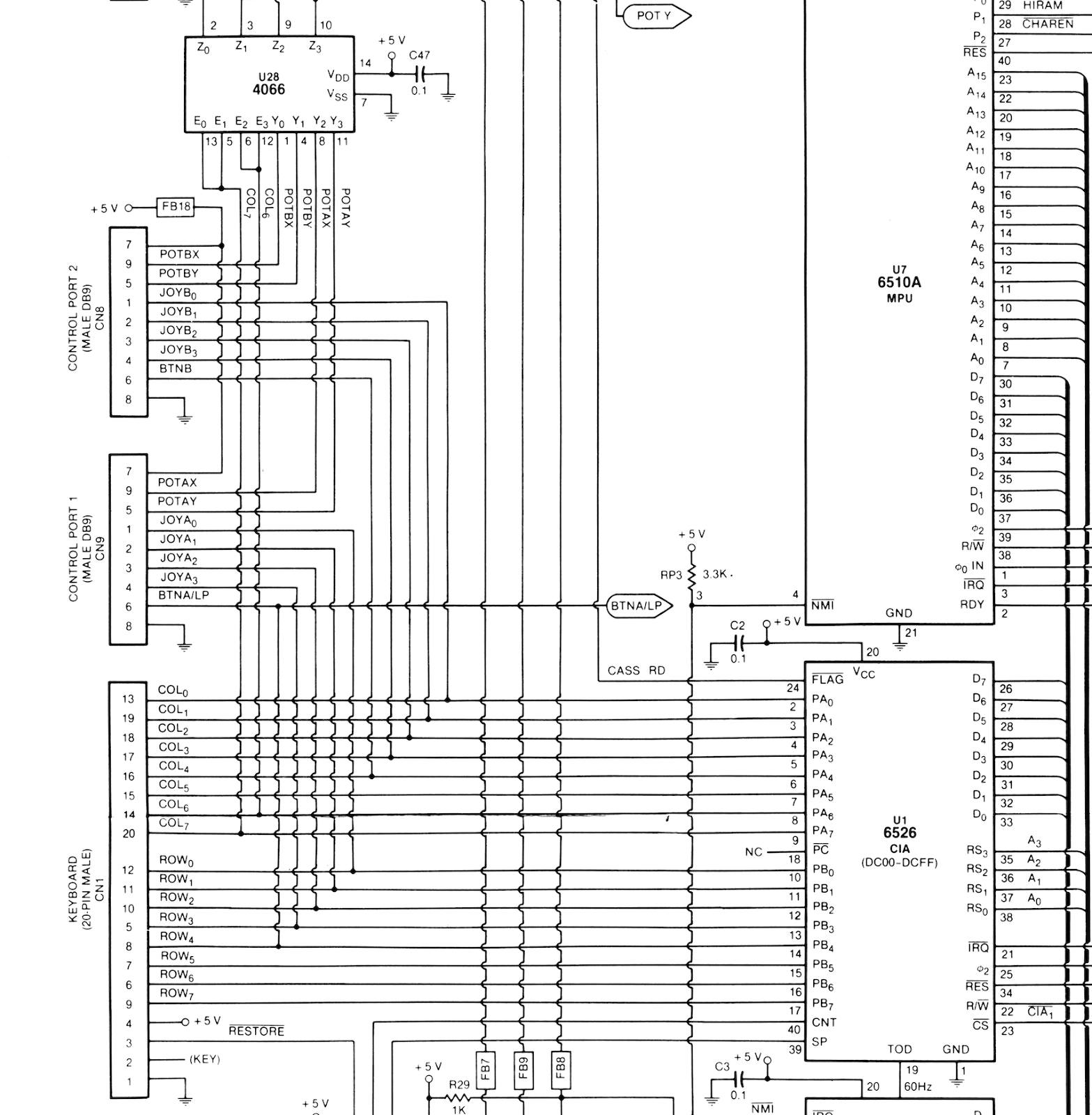

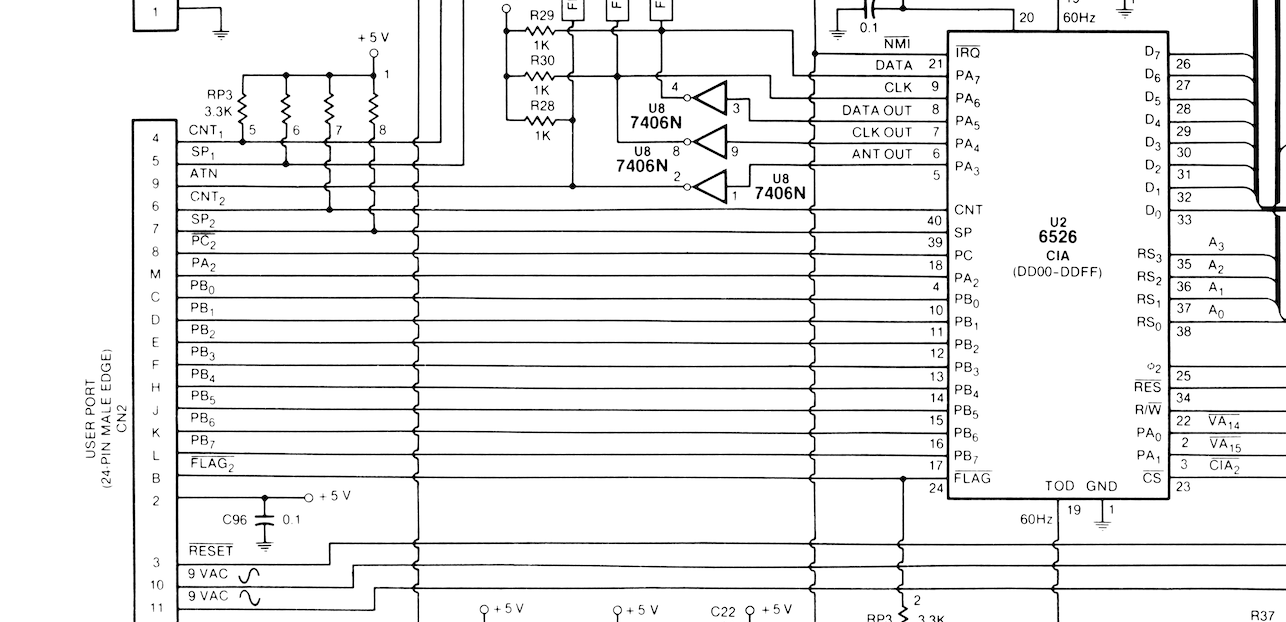

La Commodore 64 posee dos CIA conocidos en el mother como U1 y U2, aquí podemos ver su conexión esquemática con otras partes de la computadora:

Esquema de conexión

Funciones CIA 1 (U1)

Las funciones de la CIA 1 incluyen el control del teclado, control de dos puertos de joystick, el control de los dispositivos tipo paddle (potenciómetro como para el Arkanoid) y la lectura de datos del datasette conectado al pin de Cassette RD.

Los 8 pines del Port A están seteados como input y conectados a los 8 conectores de columnas del conector de teclado CN1. Los pines del del Port B están seteados como inputs y conectados a los 8 conectores de filas del conector de teclado CN1 (20 pines machos).

Las cuatros direcciones del Control Port 2 (JOYB0, JOYB1 ,JOYB2 y JOYB3) y el pin de botón BTNB están conectadas al puerto A. Las cuatros direcciones del Control Port 1 (JOYA0, JOYA1 ,JOYA2 y JOYA3) y el pin de botón BTNB están conectadas al puerto B. Si están cruzados los A y los B !

Funciones CIA 2 (U2)

Este posee dos funciones principales que son la conexión al puerto de Usuario, la conexión al bus serial de la commodore, conexión al puerto RS-232, la configuración del VIC (selección de la posición de la memoria interna) y el control de las interrupciones no enmascarables NMI.

El Port B está enteramente conectado al User Port al cuál también se conecta el pin 2 del Port A. El Port A en sus conexiones desde el pin PA7 a PA3 están dedicados al puerto serie.

Direccionamiento de Ambos CIA

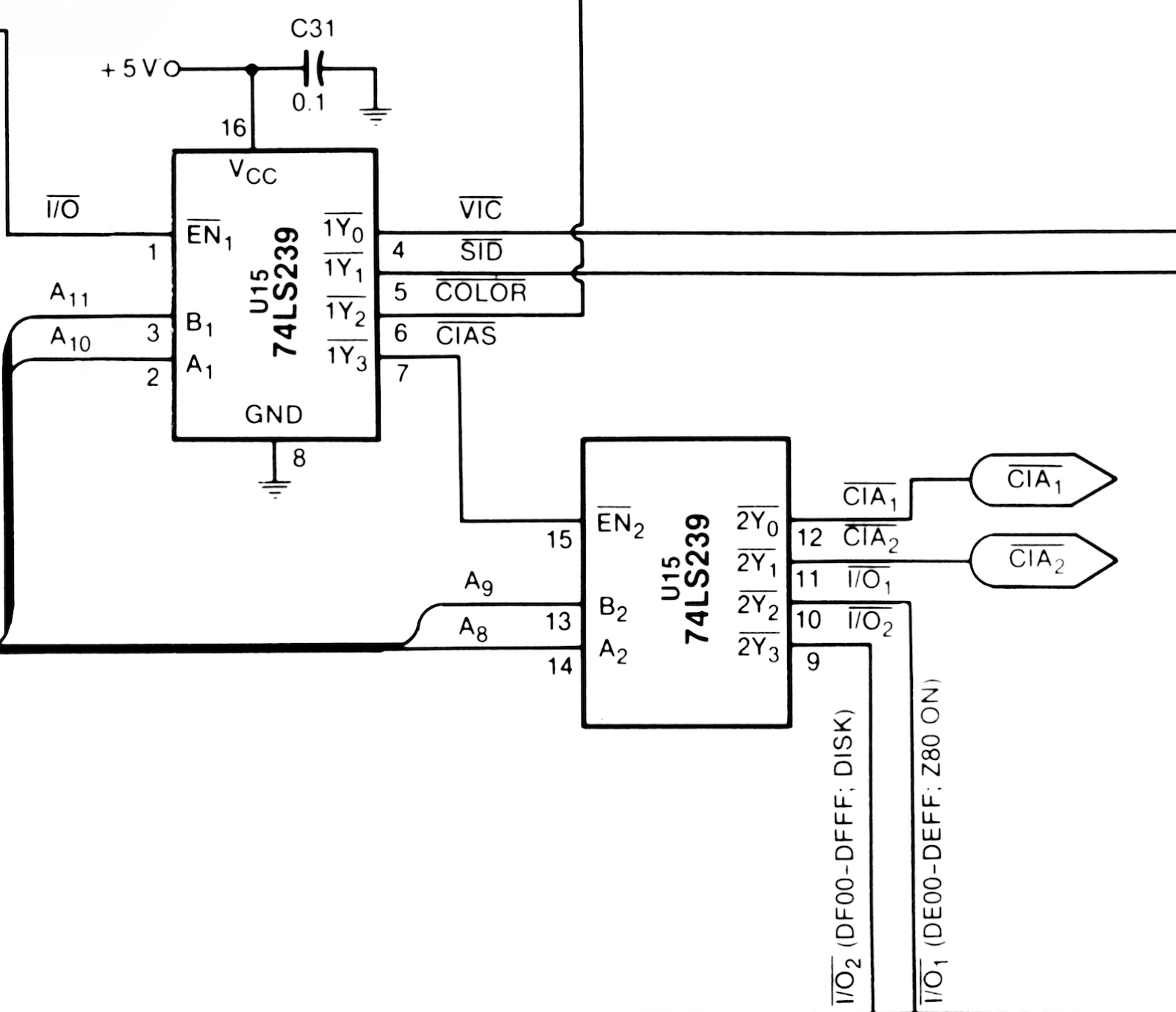

Para acceder a los CIA vamos a usar los puerto RS3 a RS0 que están conectados a los puertos de direccionamiento A3 a A0 del 6510. De esta forma podemos acceder a los registros del CIA 1 con las direcciones de DC00 a DC0F y al CIA 2 con las direcciones de DD00 a DD0F

Los pines de chip enable de cada CIA (recordemos que esperan un resultado de 0 volts o LOW) están conectados a la PLA ( a través del pin 1 de I/O) y a dos chips 74LS239 que son decodificadores y entre ambos conectan la CIA, el VIC y el SID.

El chip select no va a funcionar a menos que también se reciba la señal high del clock Phi2 al mismo tiempo.

El CIA responde al 6510 cuando el ciclo del reloj PHI2 va de low a high y a low nuevamente , esto toma aproximadamente unos 1000 nanosegundos. Durante ese tiempo el pin de CS (chip select) es mantenido en Low y si el pin de R/W es high ocurre una lectura y si es low ocurre una escritura, los pines RS reciben una dirección a un registro interno con el databus dando o recibiendo datos.

Teniendo en cuenta el diagrama de timing para que los datos sean válidos y por ejemplo puedan ser leídos, el 6510 tiene acceder al CIA mientras el pin CS esté en low, el registro interno sea direccionado por los register select RS3 a RS0, PHI2 debe estar high y los datos tienen que ser válidos (mantenidos correctamente en el tiempo).

En Resumen

Nuestros dos CIAs manejan teclado, joystick, timers, lectura de datasette, puerto de usuario, paddles y comunicaciones seriales.

El CIA en funcionamiento

Para ver visualmente como conectar un CIA al 6510 y setearlo como output y también en su función de uso de reloj les dejo como siempre un video en detalle de la serie.

En este vamos a ver cómo se conectan los pines, que código máquina escribir para comunicarnos con los registros internos y un ejemplo de output.

6526 CIA Complex Interface Adapter Programado – 6502 vs 6510 parte 8

Artículos en la serie C64 a Fondo

A continuación les dejo los links a los artículos anteriores de la serie

Introducción

Parte 1 – El módulo de reloj

Parte 2 – Pinout 6510 y 6502

Parte 3 – Codeando a Mano la Primera Instrucción de Código Máquina

Parte 4 – Primer Programa desde EEPROM

Parte 5 – I/O Pins del Procesador

Parte 6 – MOS 6503 Una Rareza

Parte 7 – VIA MOS 6522 Interfaz con periféricos

Referencias

6526 CIA Complex Interface Adapter Programado – 6502 vs 6510 parte 8

Video para profundizar el saber sobre la CIA

A continuación les dejo algunos links donde profundizar el tema

Libro Machine Language for the Commodore 64,128, y otras Computadoras Commodore Anexo I

Commodore 64 clock using the CIA TOD clock (from “Compute!”) | Retro64

vasm portable and retargetable assembler

Reemplazo Moderno de la CIA

J-CIA64 6526/8521 Replacement for Commodore 64/128/1570/1571 – Retro 8bit Shop

Referencias de velocidades de transferencias de periféricos:

Y como siempre la serie de Ben Eater del 6502

Build a 6502 computer | Ben Eater

Todos los ejemplos de código de los videos los pueden encontrar en:

C64 a Fondo – 6502 vs 6510 Parte 7 –VIA interfaz con periféricos

Hola, en esta entrega vamos a estudiar que usan los procesadores para hablar con los periféricos (datasette, disquetera) sin tener que estar constantemente congelados esperando una respuesta de ellos.

¿Por qué necesito algo entre el 6502/6510 y un periférico?

Los procesadores tienen como características ser muy rápidos, estamos hablando de 1 millón de operaciones o ciclos de reloj por segundo en el caso del 6510. Un periférico como el datasette o la disquetera está en el orden de 300 bytes por segundo de transferencia.

Si el procesador tuviera que esperar cada acceso de información disponible sería toda la computadora extremadamente lenta, por eso ponemos un chip en el medio para que hable con el procesador y los periféricos.

Este chip tiene como función recibir la información que el 6510 le envía, mantenerla y pasarla al periférico y también recibir la información desde el periférico, mantenerla y avisar al procesador que tiene información disponible para él. De esta forma el bus de datos se mantiene libre hasta que el procesador tenga que comunicarse con el VIA.

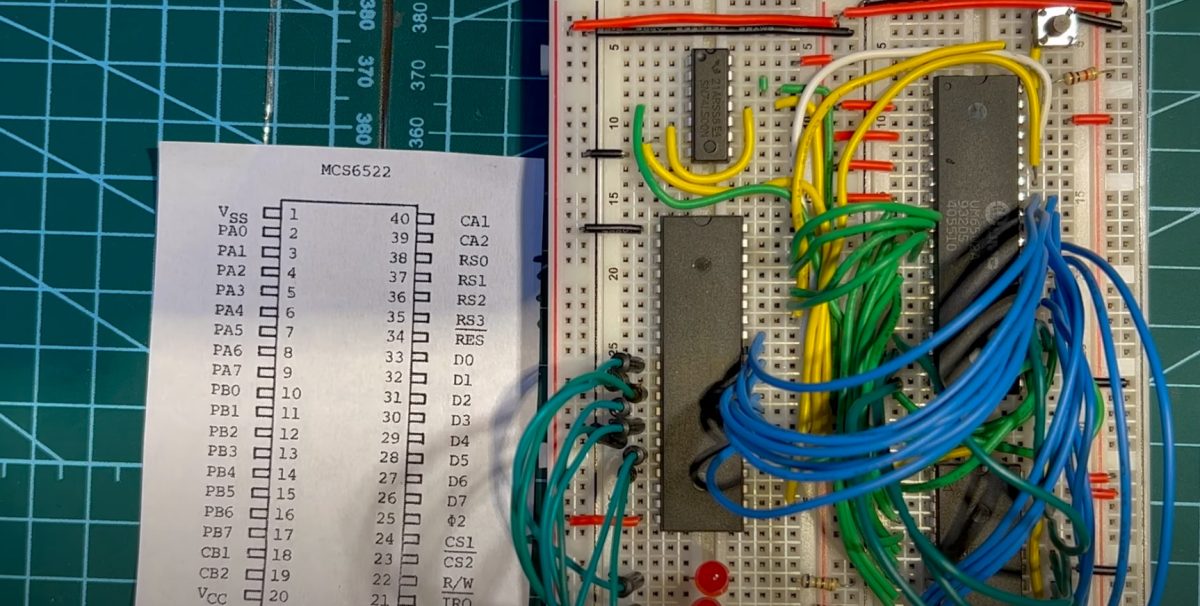

El VIA – Versatile Interface Adapter

El MOS 6522 conocido también como VIA es un chip que nos permite tener comunicación con dos puertos para periféricos (A y B) que manejen hasta 8 bits de información en el canal de datos cada uno, la misma cantidad que manejan el 6502 y el 6510 en su bus de datos.

Cada puerto tiene capacidad de mantener la información recibida por el periférico (input latching) y cada bit de los puertos puede ser seleccionado como input o output, lo que permite una comunicación directa y bidireccional entre el procesador y el periférico.

Este chip posee 16 registros internos que permiten entre otras funciones:

- Seleccionar si los pines del canal de datos son de input o output

- Almacenar la información que entrega o recibe el procesador de modo de mantener el canal de datos vacío pero la información preservada.

- Elegir si el VIA puede o no interrumpir al procesador cuando tiene información para entregar.

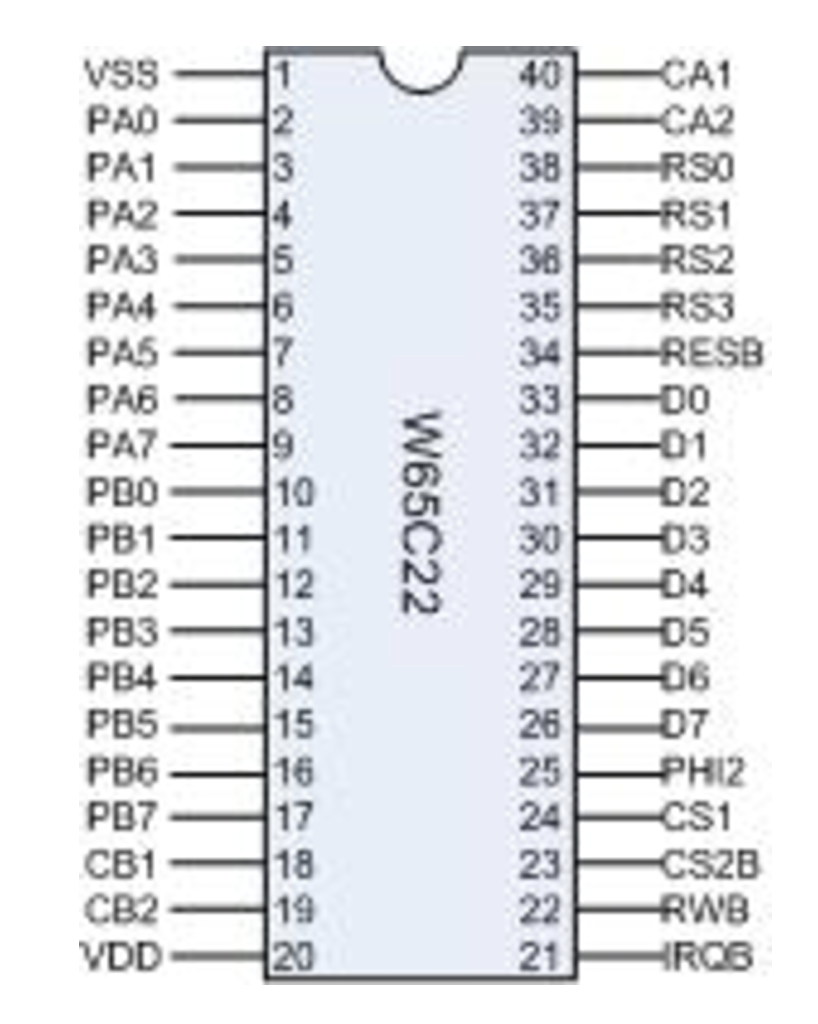

Pinout del VIA

El VIA posee 40 pines que permiten desde realizar direccionamiento, seleccionar o no el chip, hacer un reset, interrumpir al procesador y comunicarse con los periféricos. Cuando algún puerto tenga como última letra una B larga, en este diagrama significa BARRA, leer como si tuviera una barra encima o sea que el pin es Active Low, se activa cuando el voltaje va a cero (<0,4v en este caso)

VSS y VDD/VCC son los pines de Ground y 5 Volts respectivamente

PA0 a PA7 son pines de datos bidireccionales (input y output) para el primer puerto de periféricos el A, el periférico se comunica con el 6522 por esos pines.

PB0 a PB7 son pines de datos bidireccionales (input y output) para el segundo puerto de periféricos el B, el periférico se comunica con el 6522 por esos pines.

CB1 y CB2 son pines de control del puerto B permitiendo cosas como decidir en base a sus input si interrumpe o no al procesador

CA1 y CA2 son pines de control del puerto A permitiendo cosas como decidir en base a sus input si interrumpe o no al procesador

RS0 a RS3 son pines que permiten seleccionar que registro interno del VIA se accede cuándo el procesador lee o escribe los puertos de datos D0 a D7

RESB puerto de reset, el 6522 necesita de un reset cuando el 6502 es prendido por primera vez o pasar por un reset en este pin recibe la señal. (Active Low).

D0 a D7 en estos pines el procesador 6502/6510 se comunica con el 6522 para leer o escribir datos y acceder a cualquiera de los registros internos del VIA.

PHI2 en este pin se recibe la señal de reloj que es la misma que usa el 6502, al estar diseñado el 6522 para trabajar con estos procesadores todo el timing interno funciona coordinadamente con esta línea de procesadores.

CS1 y CS2B ambos pines son usados para seleccionar al chip (pines de chip enabled) cuando el CS1 es high y el CS2 es low el chip sabe que se están comunicando con él y lee o escribe en el bus de datos respectivamente.

RWB este pin específico se está realizando una lectura (high) o una escritura (low) a los pines D0 a D7.

IRQB este pin cuando está en estado low crea una interrupción al procesador para que este tome información del puerto de periférico que corresponde.

Función de input/output

La función de input output del VIA esta programada a través de los registros internos del chip.

Si queremos usar por ejemplo los puertos del PB0 al PB7 como output para darle información al periférico debemos primero seleccionar el Data Direction Register B. El mismo se selecciona a través de los puertos RS0 a RS3 en este caso poniendo los pines con los valores de 0v o Ground (<0.4 volts) en caso de tener un 0 en la tabla siguiente o 5v en caso de tener un valor 1:

RS3= 0 RS2= 0 RS1= 1 RS0= 0

Esto corresponde con el valor 2 del Register Number (DDR B). Luego de esta selección el procesador debe escribir el valor deseado a través de los pines D0 a D7. Para poner un pin en OUTPUT el valor deberá ser 1 y en INPUT deberá ser cero. Si quisiera poner todos los pines como output el procesador escribirá 1111 1111.

Luego el procesador debe enviar la información que quiere mandar de output al periférico para esto se utiliza el registro Output Register. En nuestro caso usaremos el Output Register B para seleccionarlo en los pines RS3 a RS0 poner los siguientes valores:

RS3= 0 RS2= 0 RS1= 0 RS0= 0

Que corresponden al valor de registro cero. Si quisiera tener como valores de Salida en PB7 a PB0 los valores 10101010 debería escribir estos mismos en el registros enviando esta información por los pines D7 a D0.

Estos puertos soportan input latching, que es una característica por la cual el puerto conserva el valor de input que recibió desde el periférico aunque el mismo no refresque la señal. Los datos se mantienen (aunque cambien los valores en los pines PB0 a PB7) mientras el flag CB1 de interrupción este set y se borran cuando este flag es desactivado. Para controlar si usamos o no input latching o si los pines solo reflejan el valor eléctrico que poseen en el instante usamos el registro C, Peripheral Control Register. Lo mismo aplica para el Port A.

Funciones adicionales

El VIA también provee dos timers y un Shift Register de paralelo a serial / serial a paralelo.

Timers

El Timer 1 es un contador de cuenta regresiva de 16 bits que se carga usando los registros 4 y 5 donde primero se carga la información en dos registros de tipo latch, recordando el chip la misma y luego se pasa la información a los registros del contador. Cuando este llega a cero se produce una interrupción y se pone a ground el pin de IRQB.

El Timer 2 es un contador por intervalo en el cual desde que se carga su valor inicial comienza a contar o puede también contar los pulsos recibidos en el pin PB6 del Puerto B.

Los modos de ambos Timers se setean con el registro B el Auxiliar Control Register.

Shift Register

El shift register es un registro que va a rotar los 8 bits que posee a través del pin CB2 o puede cargarse (input) a través del pin CB1 o también vaciarse (output) a través del mismo pin CB1. Muy útil para hacer conversiones serial/paralelo paralelo/serial.

El timing del shift register puede ser controlado por el Timer 2, el reloj del sistema PHI2 o un reloj externo.

Cómo funciona el de la Commodore 64 el VIA

¿Dónde usaba Commodore al VIA?

Commodore usó el VIA en diferentes productos no así en la Commodore 64 donde uso el CIA o MOS 6526 que revisaremos en un próximo artículo. Podemos ver a continuación los motherboard del VIC 20 y la disquetera 1541 donde sí fue utilizado.

El VIA en funcionamiento

Para ver visualmente como conectar un VIA al 6502 y al 6510 les dejo como siempre un video en detalle de la serie. En este vamos a ver cómo se conectan los pines, que código máquina escribir para comunicarnos con los registros internos y un ejemplo de output utilizando Leds. Todo programado directamente en código máquina.

6522 VIA Versatile Adaptive Interface – 6502 vs 6510 parte 7

Artículos en la serie C64 a Fondo

A continuación les dejo los links a los artículos anteriores de la serie

Parte 3 – Codeando a Mano la Primera Instrucción de Código Máquina

Parte 4 – Primer Programa desde EEPROM

Parte 5 – I/O Pins del Procesador

Referencias

A continuación les dejo algunos links donde profundizar el tema

Video de la serie 6502 vs 6510 Parte 7 – El VIA

MOS 6522 Versatile Adaptive Interface VIA – 6502 vs 6510 parte 7

Libros y artículos

Libro Machine Language for the Commodore 64,128, y otras Computadoras Commodore Anexo I

MCS6522 VERSATILE INTERFACE ADAPTER

W65C22 (W65C22N and W65C22S) Versatile Interface Adapter (VIA) Datasheet

Commodore 64 clock using the CIA TOD clock (from “Compute!”) | Retro64

Referencias de velocidades de transferencias de periféricos:

Y como siempre la serie de Ben Eater del 6502

Build a 6502 computer | Ben Eater

Todos los ejemplos de código de los videos los pueden encontrar en:

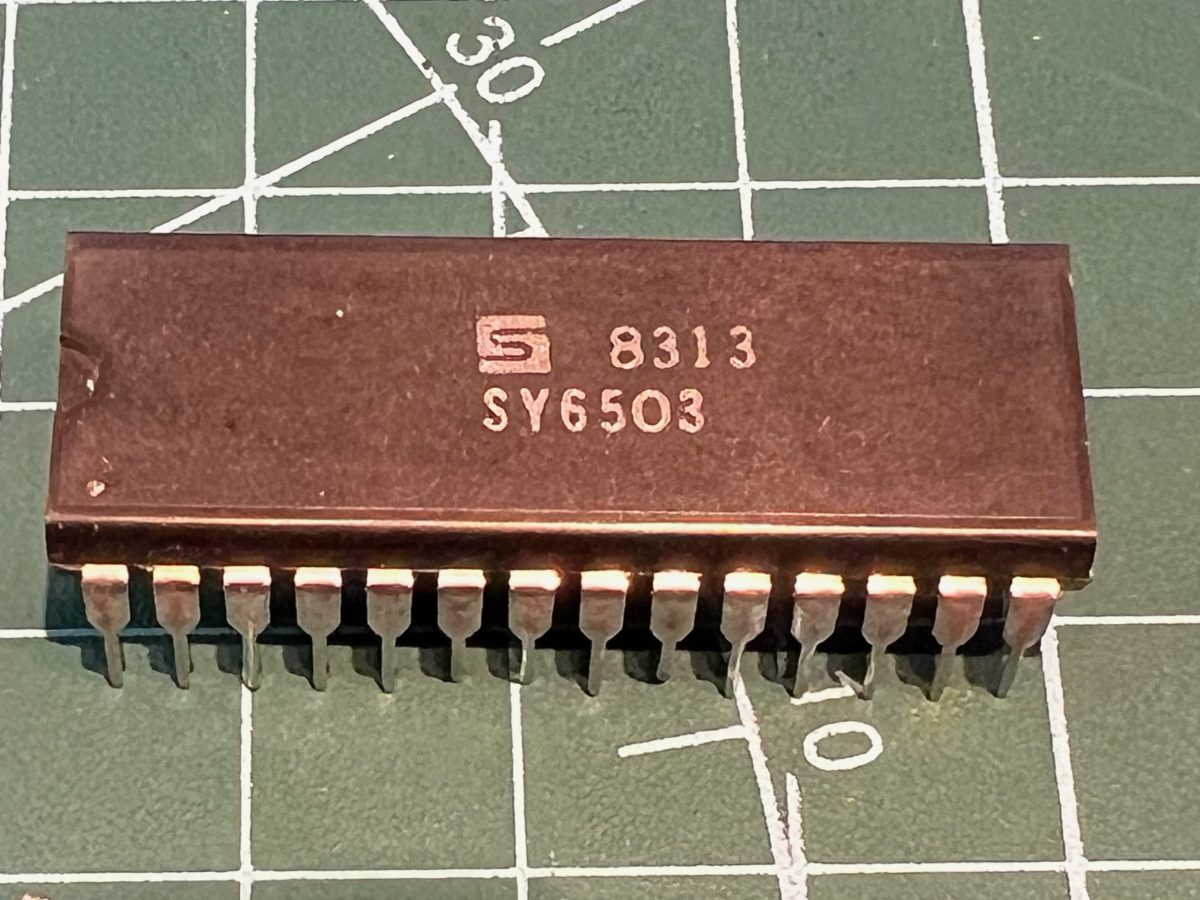

C64 a Fondo – 6502 vs 6510 Parte 6 – MOS 6503 Una Rareza

Hola, en esta entrega vamos a estudiar al Procesador MOS 6503 una verdadera rareza. Se trata de un procesador de la familia del 6502 y del 6510 pero con muchos menos pines (28 en lugar de 40) y la capacidad de direccionar solo 4kb de memoria ram.

Cosas en común con la familia 6500

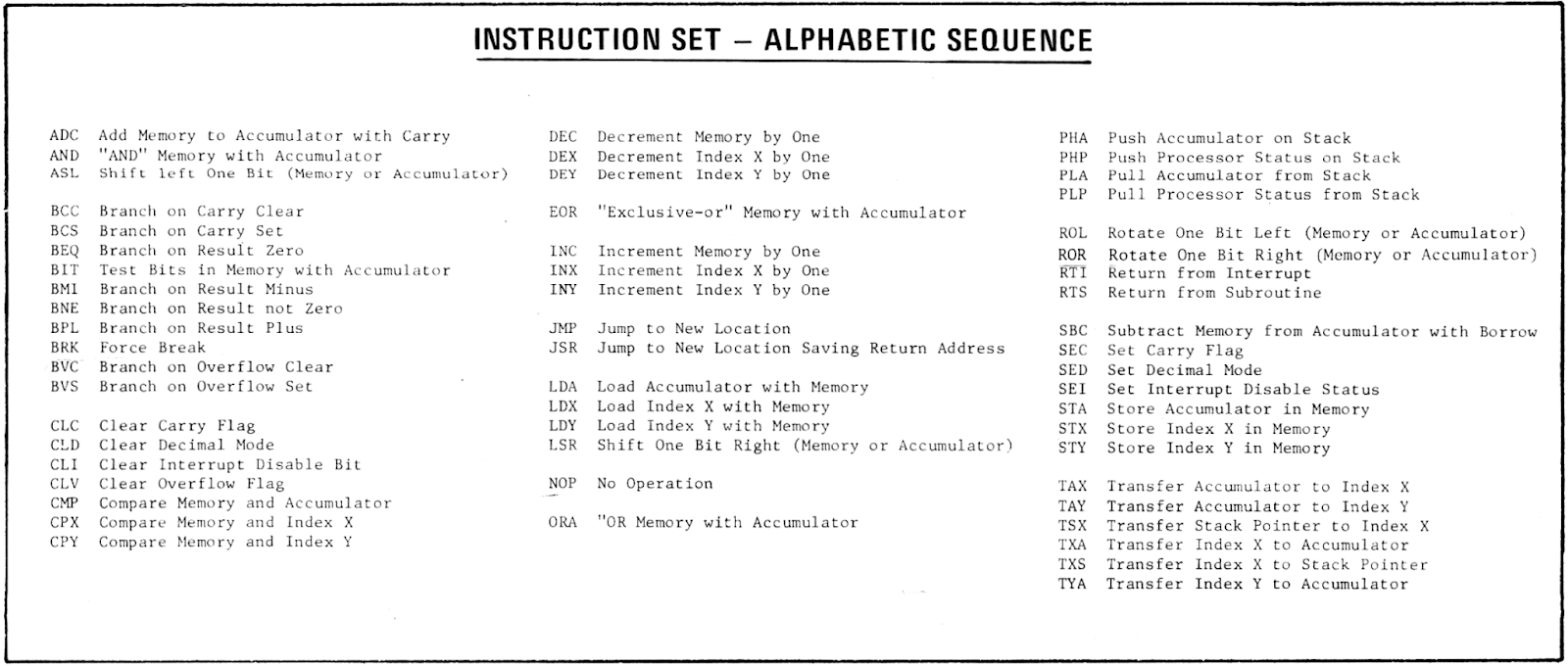

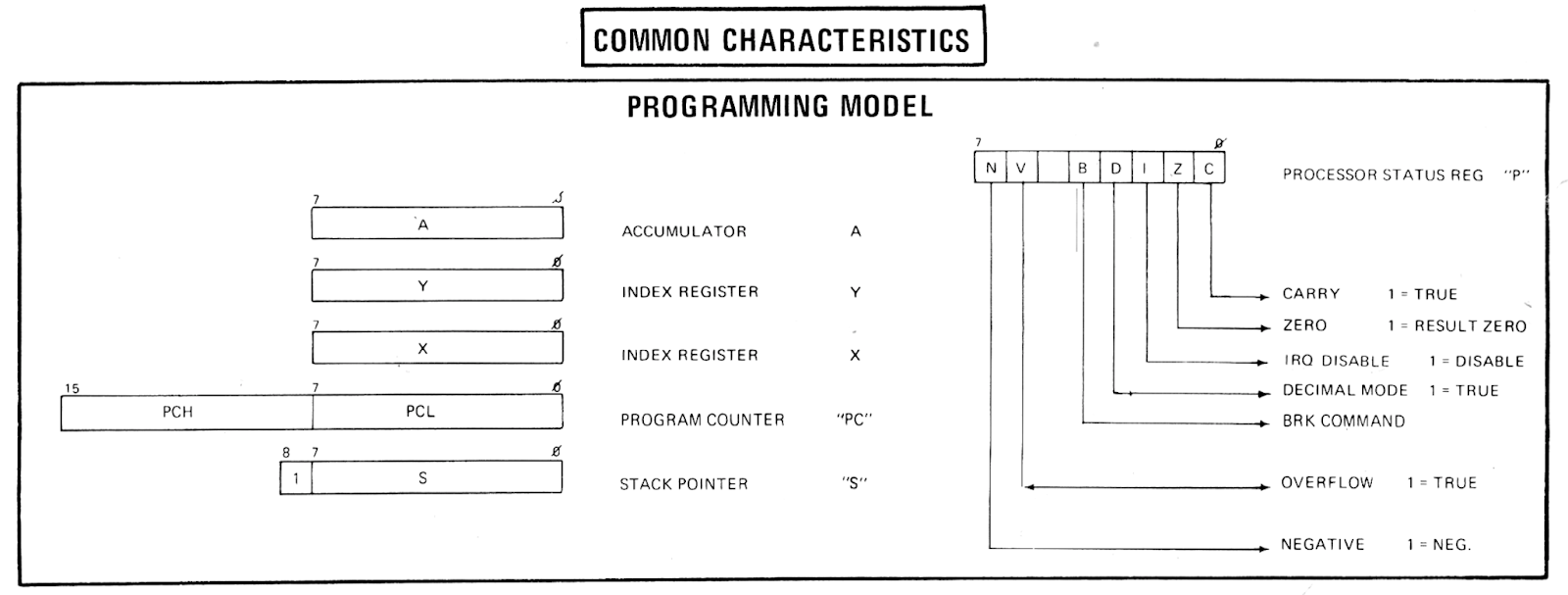

Este 6503 tiene algunas cosas fundamentales en común con la familia del 6500 sin las cuales cualquier desarrollo en esta plataforma sería muy pero muy difícil.

La primera es el código máquina, este posee las mismas instrucciones a las que ya estamos acostumbrados en nuestros 6502 y 6510, poseyendo también los mismos modos de direccionamiento de memoria.

El timing del mismo está dentro de lo esperado para la familia pudiéndose comunicar con los VIA y CIA si se sincronizan los relojes de estos chips entre sí.

La cantidad de registros y la forma de accederlos se mantienen para toda la familia estos son los familiares A, X e Y, el Status Register y el Stack Pointer, los 5 registros, de 8 bits y el Program Counter de 16 bits.

Tomando en cuenta el análisis de Jim Butterfield – Wikipedia un prócer del lenguaje en código máquina para Commodore el 6503 es sólo un 6502 con menos pines e idéntico funcionamiento.

También posee 8 bits bidireccionales de datos. Todavía podemos encontrar procesadores compatibles como el Synertek 6503

Pin-Out y diferencias

Aquí salta a la vista la diferencia más grande ya que ¡A este chip le han robado unas patitas! Sí, su formato es DIP28 en lugar de los ya tradicionales DIP40 que nos acostumbraron el 6502 y el 6510. ¿Y dónde es que nos faltan esas patitas? Ni más ni menos que en el address bus.

Este posee solo 12 pines (pin AB0 a AB11) en lugar de los tradicionales 16 direccionando solo 2ˆ12 bytes, o sea 4096 bytes o 4 kb para direcciones de memoria.

Aquí hay que tener especial cuidado al armar alguna placa que tenga chips que esperen 15 o 16 bits en su direccionamiento, en las mismas tenemos que asegurarnos que esos pines no queden flotando (no conectados ni a ground ni a 5v). Típicamente en una maqueta de breadboards pueden conectar los pines sobrantes a ground o 5v dependiendo si queremos 0 o 1 para ese bit en particular.

/RES Pin de reset, este pin sirve para realizar un reset del procesador cuando se conecte a 0v. El reset tomará 7 ciclos de reloj y buscará en las posiciones de memoria $0FFC y $0FFD donde está el vector (otra posición de memoria) que posee la primera instrucción a ejecutar. El reset debe ser mantenido en 0v por lo menos durante dos ciclos de reloj para que sea reconocido. Nótese que no usamos las tradicionales $FFFC y $FFFD.

VSS Pin de Ground, este pin se conecta al common ground del diseño.

PHI1 o 01 (OUT) Pin de Salida de Reloj, el mismo es una salida de reloj para conectar a otros dispositivos. El PHI1 es típicamente la señal del PHI2 pero invertida.

/IRQ Pin de interrupción. Al conectar este pin a 0V, si las interrupciones están habilitadas, el procesador guardará el contenido de los registros actuales y buscará en las posiciones de memoria 0FFE y 0FFF donde está el vector (otra posición de memoria) que posee la primera instrucción a ejecutar para atender a esta interrupción. Nótese que no usamos las tradicionales $FFFE y $FFFF.

/NMI Pin de interrupción no enmascarable. Al conectar este pin a 0V el procesador guardará el contenido de los registros actuales y buscará en las posiciones de memoria 0FFA y 0FFB donde está el vector (otra posición de memoria) que posee la primera instrucción a ejecutar para atender a esta interrupción. Este tipo de interrupción es incondicional y siempre será honrada. Nótese que no usamos las tradicionales $FFFA y $FFFB.

VCC Pin de Energía. El procesador típicamente trabaja con +5v ± 5% de sobre o sub fluctuación en el voltaje.

AB0 a AB11 Pines del Bus de Direccionamiento. Son pines bidireccionales que permiten recibir las direcciones de los dispositivos a los cuales comunicarse (memorias, otros chip en la placa, registros de I/O, etc). Al ser un bus de 12 bits direcciona hasta 4096 bytes o desde $0000 hasta $0FFF.

DB0 a DB7 Pines del Bus de datos, Este es un bus bidireccional que permite recibir y escribir datos junto con el bit de R/W a memorias y registros de I/O.

R/W Pin de Lectura/Escritura. Este pin indica si el procesador está realizando una lectura o una escritura. Cuando se encuentra en 1 o en estado High el procesador está realizando una lectura cuando está en 0 o estado Low una escritura.

PHI0 o 00 (IN) Pin de entrada de Reloj, Este pin permite conectar un reloj interno al procesador para sincronizarse con otros dispositivos.

PHI2 o 02 (OUT) Pin de Salida de Reloj, el mismo es una salida de reloj para conectar a otros dispositivos.

Cómo funciona en la Commodore 64

El 6503 no se utilizó en la Commodore 64, ni en ninguna computadora Commodore conocida, fue hecho por MOS Technologies para dar un 6502 con un paquete de 28 pines, lo cual era más barato tanto en espacio de pcb utilizado como en costo del chip.

El 6503 en acción

Bueno aca les dejo un video del 6503 en acción donde vamos a explicar como funciona cada uno de sus pines, programarlo a mano utilizando resistencias con la instrucción de código máquina EA (correspondiente a NOP o no operación) y estudiar que pasa por sus pines y qué direcciones usa al bootear,

6503 una rareza, 6502 vs 6510 Parte 6

Artículos en la serie C64 a Fondo

A continuación les dejo los links a los artículos anteriores de la serie

Parte 3 – Codeando a Mano la Primera Instrucción de Código Máquina

Parte 4 – Primer Programa desde EEPROM

Parte 5 – I/O Pins del Procesador

Referencias

A continuación les dejo algunos links donde profundizar el tema:

Video de la serie 6502 vs 6510 Parte 6 – 6503 una rareza:

6503 una rareza, 6502 vs 6510 Parte 6

commodore.ca | The New 6500 Processors (CPU) by Jim Butterfield

Y como siempre la serie de Ben Eater del 6502

Build a 6502 computer | Ben Eater

Todos los ejemplos de código de los videos los pueden encontrar en:

C64 a Fondo – 6502 vs 6510 Parte 5 – I/O Pins del procesador

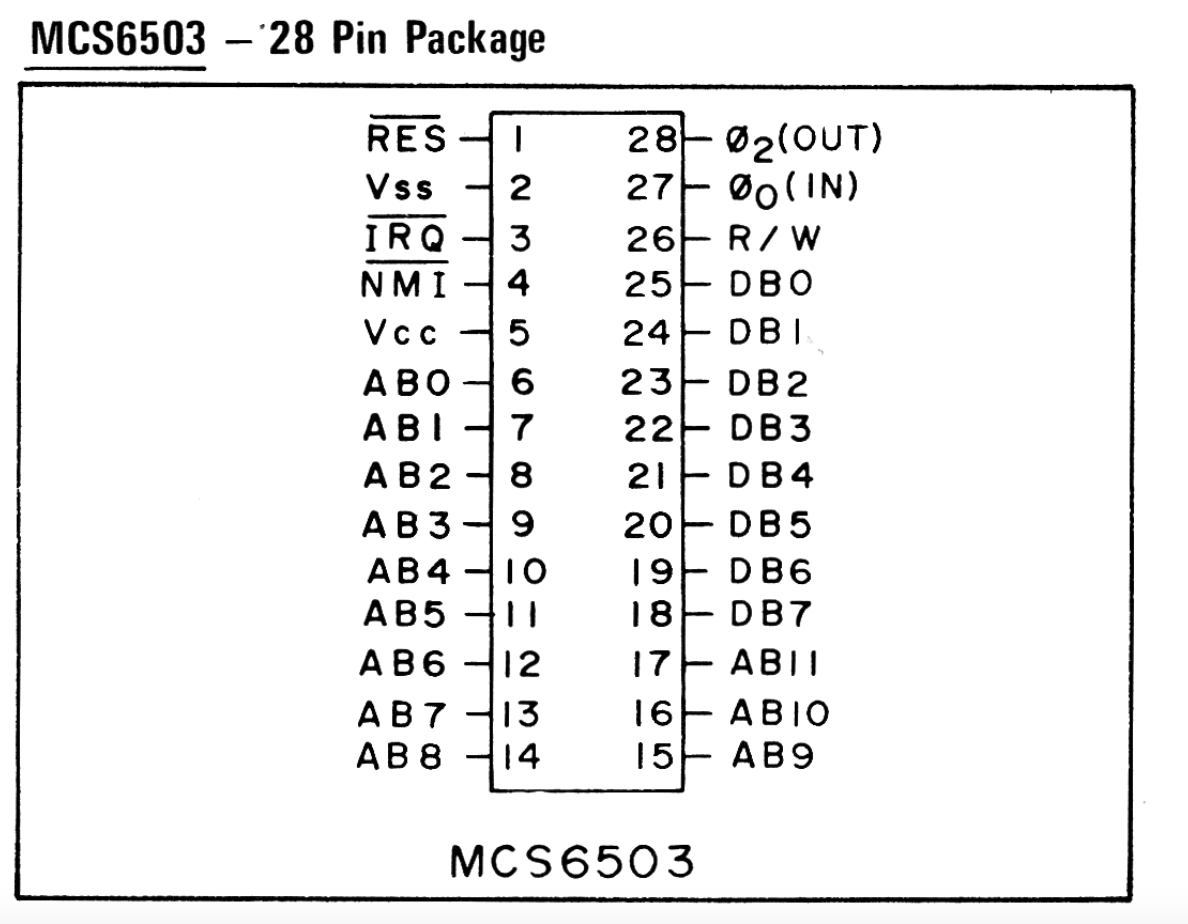

Continuamos este estudio comparativo del 6502 vs el 6510 en este caso descubriendo la principal diferencia entre el 6510 y el 6502 los pines de Input/Output que posee el 6510 y no posee el 6502.

Les dejo el link al articulo anterior en la serie, y al final como siempre los links a todos los artículos de la misma.

Parte 4 – Primer Programa desde EEPROM

Qué son los I/O Ports

La I/O ports son 6 puertos/pines/registros que pueden funcionar como Input o como Output en el procesador 6510.

P0 a P5 Pines de I/O Port. Este procesador en su más marcada diferencia presenta en estos pines 6 conexiones bidireccionales con periféricos como si fuera un pequeño 6522 VIA o un 6526 CIA.

Cómo se utilizan

Para poder utilizarlos se debe especificar si los vamos a usar como Input o Output. Esto se hace de una forma muy particular. El procesador 6510 a diferencia de todo el resto de la línea 6500 utiliza para sí dos direcciones de memoria que nunca pueden ser parte de la RAM o ROM y son las primeras dos direcciones la $0000 y la $0001.

La dirección $0000 es llamado DATA DIRECTION Register. En este vamos a especificar para cada uno de los seis pines si lo queremos utilizar como Input o como Output. Si el valor es 0 queda como Input y si es 1 queda como output. Si lo vamos utilizar como Input conectarlo con una resistencia a 0 Volts o +5 Volts mientras no se utilice para no tener inputs flotando. Esta especificación se realiza escribiendo un byte a la dirección $0000.

| Bit | Pin | Input/Output |

| 0 | 0 | 0/1 |

| 1 | 1 | 0/1 |

| 2 | 2 | 0/1 |

| 3 | 3 | 0/1 |

| 4 | 4 | 0/1 |

| 5 | 5 | 0/1 |

| 6 | No Utilizado | No Utilizado |

| 7 | No Utilizado | No Utilizado |

Por ejemplo si quisiéramos habilitar el pin 2 y el 4 como Output y el resto como Inputs deberíamos escribir el número binario %00010100 correspondiente al hexadecimal $18. Podríamos configurar al 6510 con la siguiente instrucción en assembler

lda #%00010100 ; cargamos al acumulador el número en binario

; antecedido por % para indicar que está em binário

; y # para indicar que es un número y no una posición

; de memoria

sta $00 ;guardamos el contenido del acumulador en el

;registro interno de memoria DATA DIRECTION REGISTER

Si ahora queremos leer la información de los I/O registers necesitamos utilizar otra dirección de memoria la $0001 también llamado de I/O port register.

| Bit | Pin | Input/Output |

| 0 | 0 | 0/1 |

| 1 | 1 | 0/1 |

| 2 | 2 | 0/1 |

| 3 | 3 | 0/1 |

| 4 | 4 | 0/1 |

| 5 | 5 | 0/1 |

| 6 | No Utilizado | No Utilizado |

| 7 | No Utilizado | No Utilizado |

Podemos cargar los valores de este registro al acumulador con el siguiente comando para leer por ejemplo:

Lda $01 ; lee el I/O port register

Sta $0400 ; escribe el contenido del acumulador en la posición

; de memoria $0400

Para poder escribir en este registro y por consecuencia cambiar el valor de los pines con valor 1 a +5 Volts o High usamos el siguiente programa assembler.

lda #%00111111 ;va a escribir todos los bits del I/O port para que

;sus pines sean +5 Volts

sta $01 ;escribir el registro

Cómo funciona en la Commodore 64

La Commodore 64 y su procesador 6510 pueden direccionar hasta 65536 direcciones de memoria, los famosos 64KB, pero ¿cuántos kb tenemos en la Commodore?

| Kbytes | Función |

| 64 | RAM |

| 8 | BASIC ROM |

| 8 | KERNAL ROM |

| 4 | Character Generator |

| 4 | I/O (Vic II, SID, CIA 1 y 2, Puerto de Cartucho) |

Esto nos da 64+8+8+4+4 = 88Kb para direccionar, lo cual es un problema ya que tendríamos 24Kb que no podrían ser direccionados, ahí entran los I/O Ports para ayudarnos.

Estos cumplen dos funciones: manejar parte del datasette y direccionar esta memoria extra para que puedan caber las 65536 direcciones.

Los puertos en cuanto a su configuración de Input o Output así se encuentran configurados en la Commodore.

| Bit | Pin | Input/Output | Nombre en C64 |

| 0 | 0 | 1 output | LORAM |

| 1 | 1 | 1 output | HIRAM |

| 2 | 2 | 1 output | CHAREN |

| 3 | 3 | 1 output | Cassette Write |

| 4 | 4 | 0 input | Cassette Sense |

| 5 | 5 | 1 output | Cassette Motor |

| 6 | No Utilizado | No Utilizado | No Utilizado |

| 7 | No Utilizado | No Utilizado | No Utilizado |

Manejo de Memoria

Memorias que se superponen, como vimos anteriormente veamos cómo es que estas memorias se están superponiendo y en qué direcciones.

| Nombre | Direcciones | Kbytes | Función 1 | Función 2 | Función 3 |

| Low Memory | $0000-$9FFF | 40kb | RAM | ||

| BASIC | $A000-$BFFF | 8kb | RAM | BASIC ROM | |

| High Memory | $C000-$CFFF | 4kb | RAM | ||

| I/O | $D000-$DFFF | 4kb | RAM | I/O | CHAR ROM |

| KERNAL | $E000-$FFFF | 8kb | RAM | KERNAL ROM |

Como se superponen estas memorias se controla principalmente con los I/O ports de P0 a P2.

P0 – Bit 0 del registro $0001, LOW RAM. Si este bit es 0 tenemos acceso a la RAM si es 1 a la BASIC ROM. ¿Cuándo lo apago? ,cuando creo un programa en código máquina con lo que aprovecho 8kb extras de ram.

P1 – Bit 1 del registro $0001, HIGH RAM. Si este bit es 0 tenemos acceso a la RAM si es 1 al KERNAL ROM. ¿Cuándo lo apago? ,cuando creo un programa en código máquina y no necesito ninguna rutina del KERNAL con lo que aprovecho 8kb extras de ram

P2 – Bit 2 del registro $0001, LOW RAM. Si este bit es 0 tenemos acceso a los I/O devices (VIC II, SID, CIA, etc) si es 1 a la ROM de character generation donde se almacenan los 2 juegos de caracteres de la commodore. Generalmente nunca debemos acceder a la ROM del CHAR GEN ya que el VIC II puede acceder a esta directamente para dibujar los caracteres en pantalla. Un motivo válido para acceder es leerla para copiarla en memoria y modificar el juego de caracteres.

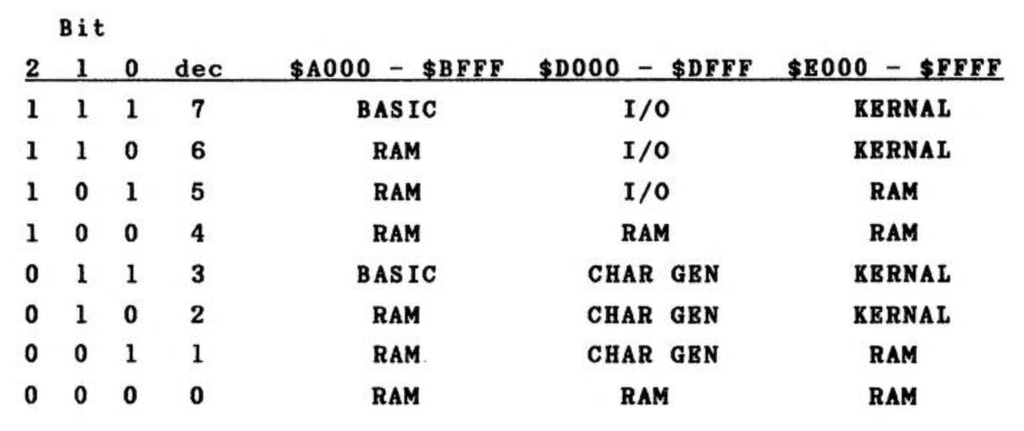

Aquí tenemos otro gráfico que muestra mejor la configuración de los 3 registros y que efectos tendrían en memoria.

A continuación les incluyo un programa en BASIC que les va a permitir apagar momentáneamente el basic y el kernel escribir y leer en la RAM oculta y volver a activar el basic y el kernel sacado del libro PEEKS & POKES para Commodore 64.

Para leer la RAM escondida usar:

PRINT USR(ADDRESS).

Para escribir haciendo un POKE usar:

SYS 715,ADDRESS,BYTE

Y este es el programa en código máquina con su loader en basic:

10 DATA 165,20,72,165,21,72,32,247,183,120,165,141,252,133

20 DATA 1,160,0,177,20,168,165,1,9,3,133,1,88,104,133,21

30 DATA 104,133,20,76,162,179,32,253,174,32,138,173,32,247

40 DATA 183,32,253,174,32,158,183,165,1,41,252,133,1,138

50 DATA 160,0,145,20,165,1,9,3,133,1,96

60 FOR 1=678 TO 747: READ A: POKE I, A: NEXT I

70 POKE 785,166:POKE 786,2

Manejo de Datasette

El datasette es manejado por 3 puertos del 6510 y la CIA. Los I/O Ports P3 a P5 están conectados a las funciones de CASSETTE Write, CASSETTE Sense, y CASSETTE Motor.

P3 – Bit 3 del registro $0001, Cassette Write. Este puerto es el que se utiliza cuando vamos a grabar información al cassette enviando pulsos con la información a grabar a través de este pin.

P4 – Bit 4 del registro $0001, Cassette Sense. Este puerto mide si alguna tecla fue presionada en el datasette. Cuando vemos el famoso mensaje “PRESS PLAY ON TAPE” el procesador está esperando que presionemos la tecla play en el datasette. Al presionar esta tecla y como el puerto es un input se lee un 0 Volts y el datasette sabe que una tecla fue presionada. Como podemos presionar 3 teclas en el datasette (play, rewind, forward) y sólo tenemos una línea de Casette Sense se produce el efecto curioso de que si presionamos rewind o forward la Commodore piensa que presionamos play y trata de cargar el programa de casette.

P5 – Bit 5 del registro $0001, Cassette Motor. Este puerto activa el motor del datasette cuando se presiona una tecla en el datasette, si alguna vez hicieron la prueba de presionar el botón de play y nada funciona si no está conectado a la Commodore no es sólo por una falta de power sino por que la tecla play no hace nada sólo el pin P5 activa el motor del datasette.

Si estudiamos el circuito exacto conectado a este puerto vemos que en realidad el procesador no prende el motor si no que activa un transistor que switchea 9 Volts para que estos sí vayan al conector del datasette y alimenten el motor

Para completar la discusión del datasette nos falta sólo el puerto de cassette read pero este está conectado al puerto /flag de la CIA1 y está fuera del contexto de los puerto I/O del 6510 y será analizado en un próximo artículo.

Estudiando los I/O Ports visualmente

Para poder estudiar visualmente cómo se conectan y funcionan los I/O ports del 6510 les dejo este video que complementa al artículo.

6502 vs 6510 IO Ports / Processor Ports – Parte 5

Artículos en la serie C64 a Fondo

A continuación les dejo los links a los artículos anteriores de la serie

Parte 3 – Codeando a Mano la Primera Instrucción de Código Máquina

Parte 4 – Primer Programa desde EEPROM

Referencias

A continuación les dejo algunos links donde profundizar el tema:

VIDEOS

Video de la serie 6502 vs 6510 Parte 5 – IO Ports / Processor Ports

6502 vs 6510 IO Ports / Processor Ports – Parte 5

Aquí tiene acceso a toda la serie:

6502 vs 6510 estudio detallado y comparación

PAPERS

The 6510 Processor Port | C64 OS

Y como siempre la serie de Ben Eater del 6502

Build a 6502 computer | Ben Eater

Todos los ejemplos de código de los videos los pueden encontrar en:

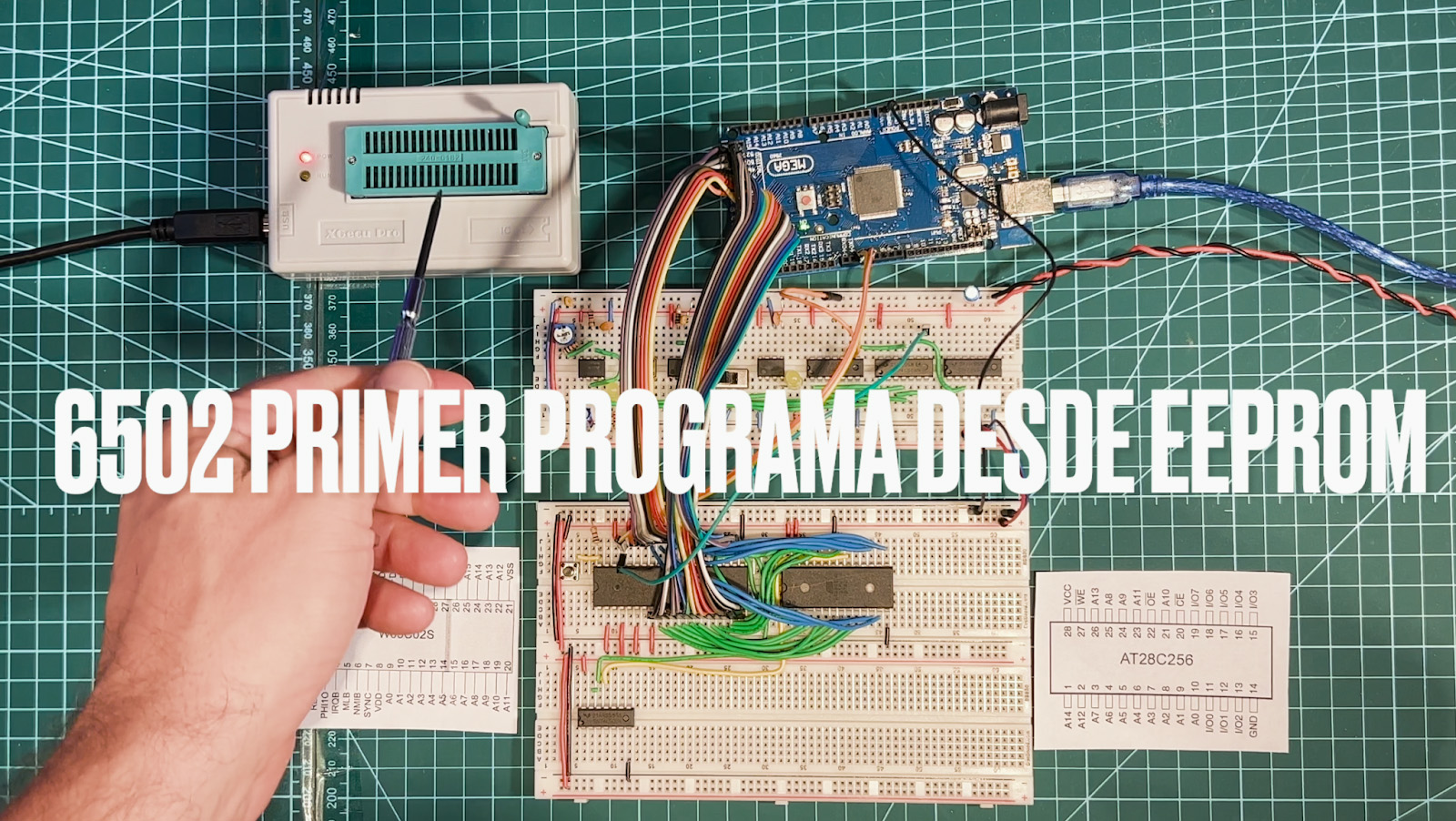

C64 a Fondo – 6502 vs 6510 Parte 4 – Primer Programa desde EEPROM

Continuamos este estudio comparativo del 6502 vs el 6510 en este caso creando nuestro primer programa en código máquina y grabándolo en una EEPROM, de esta forma vamos a indicarle al procesador que lea y ejecute el programa desde memoria.

Les dejo el link al articulo anterior en la serie, y al final como siempre los links a los artículos de la misma.

Parte 3 – Codeando a Mano la Primera Instrucción de Código Máquina

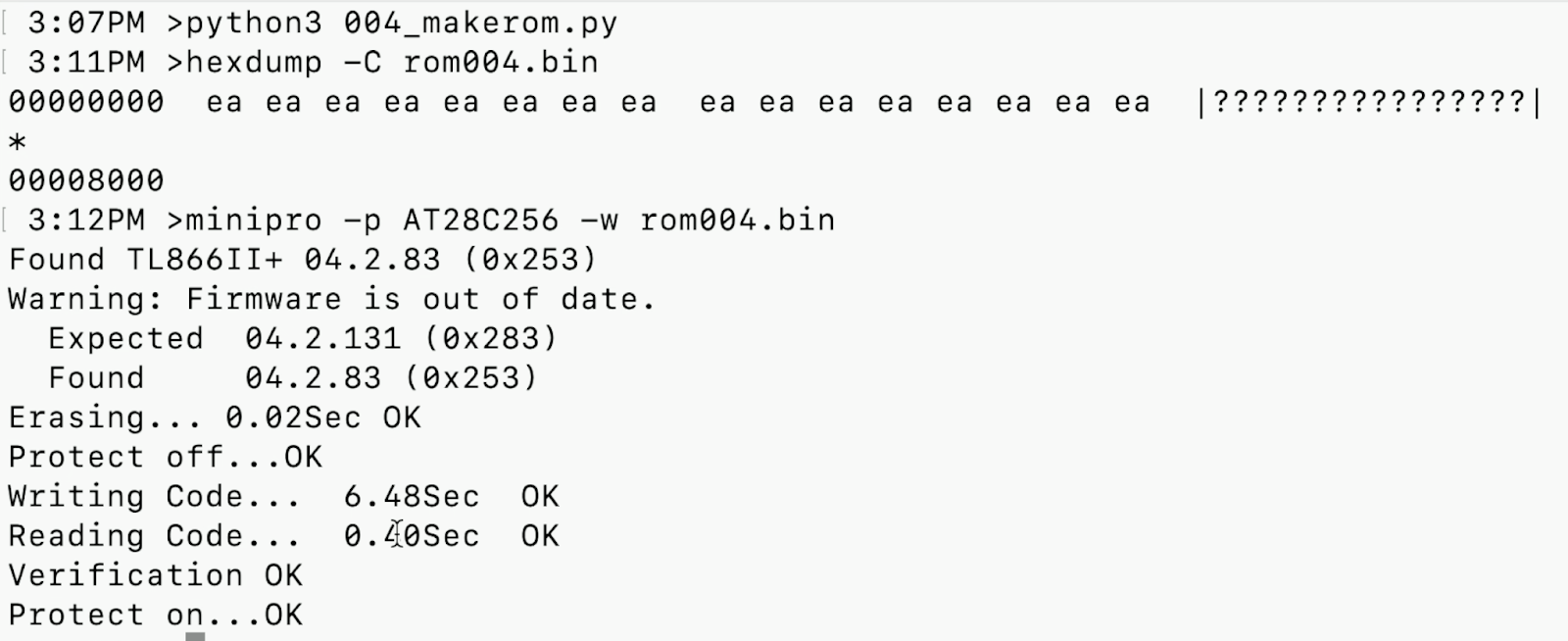

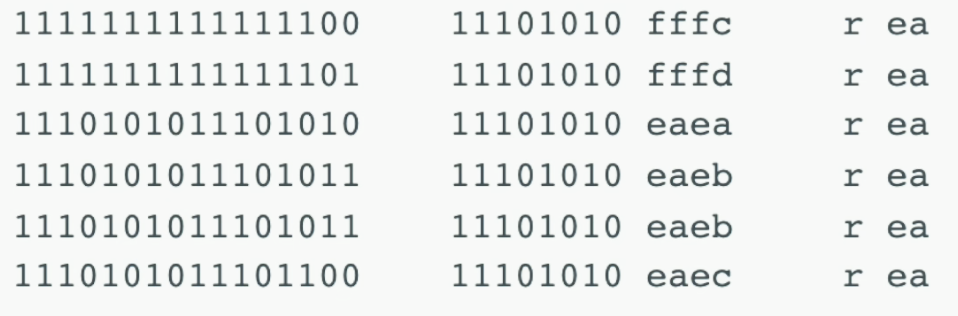

Qué es una EEPROM

Para poder avanzar en nuestro estudio de los procesadores vamos crear un programa en código máquina que vamos a almacenar en una memoria de sólo lectura. Esto es una eeprom Electrically Erasable Programable Read Only Memory, la cuál vamos a grabar fuera de nuestro breadboard utilizando un grabador de eeprom que el procesador va a tratar como si fuera una memoria de sólo lectura, leyendo instrucciones y datos de la misma pero nunca escribiendolos.