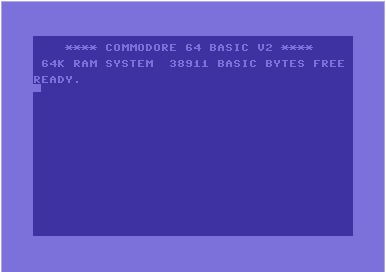

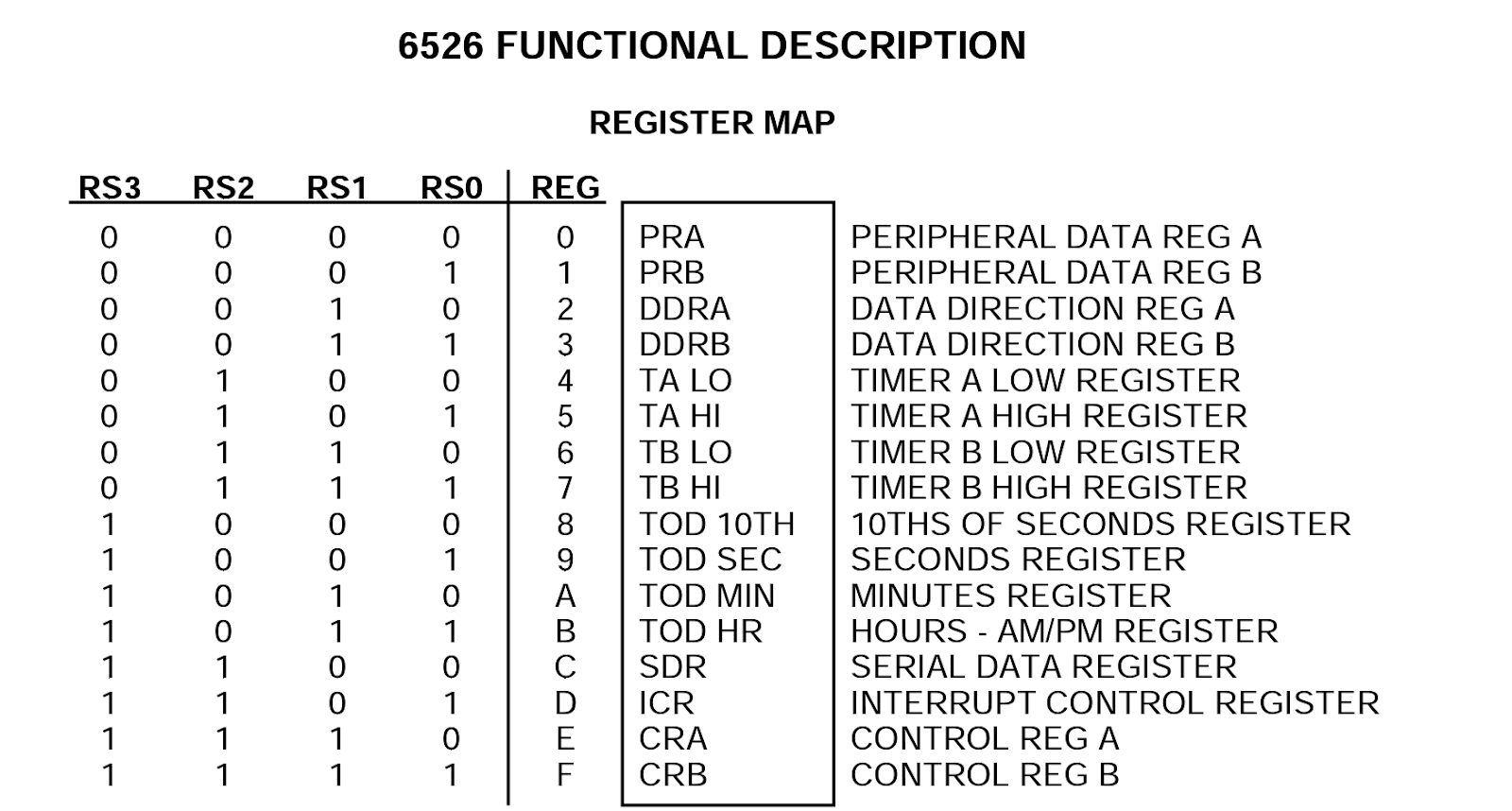

Continuamos este estudio comparativo del 6502 vs el 6510 esta vez conectando una memoria Static RAM del modelo 62256 que posee 32kb.

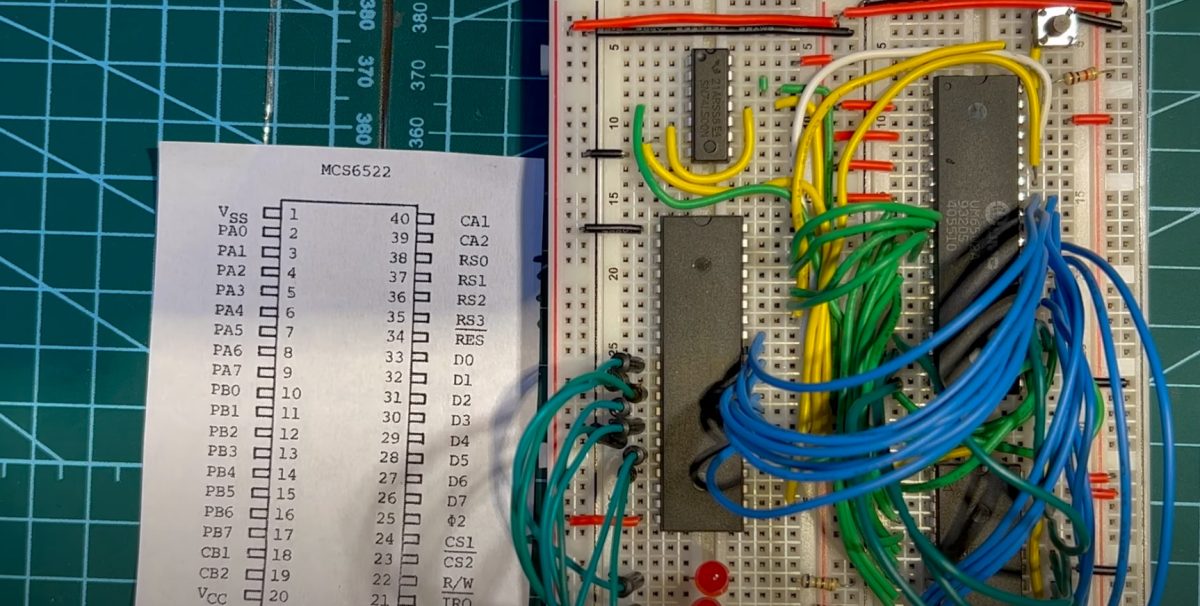

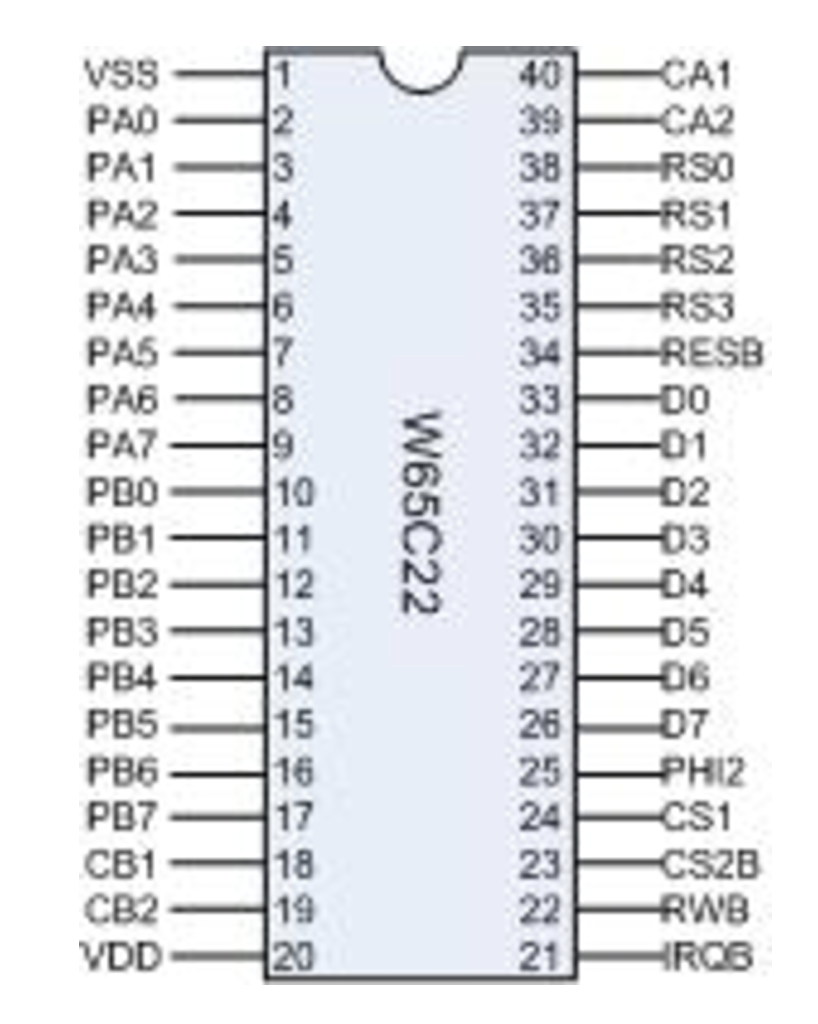

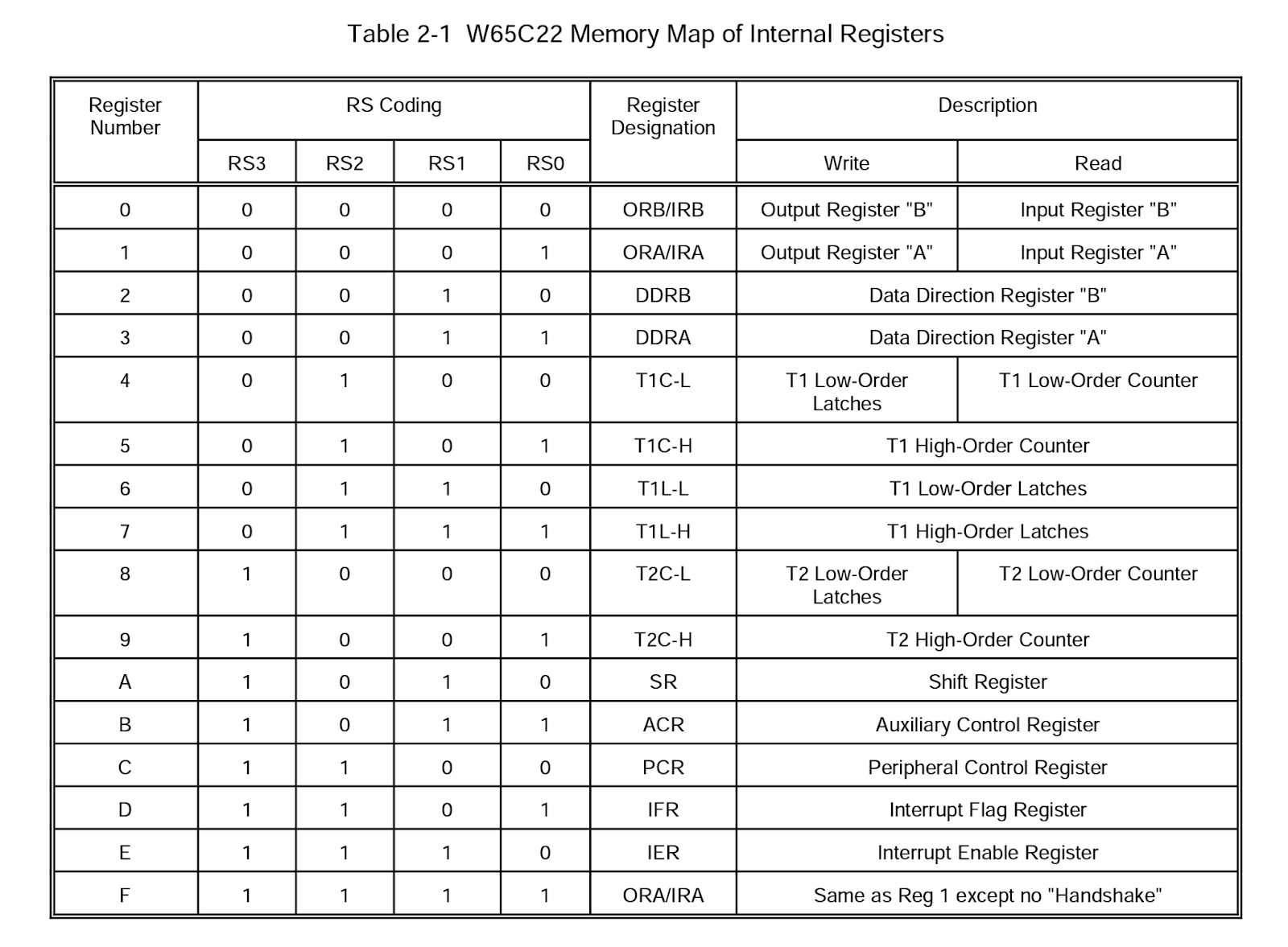

Vamos a estudiar cómo conectar esta memoria tanto a un 6510 con CIA 6526 como a un 6502 con VIA 6522, incluiremos todas las rutinas de assembler para poder probar la memoria, sus conexiones físicas y timing de la memoria con el procesador, punto central de su funcionamiento.

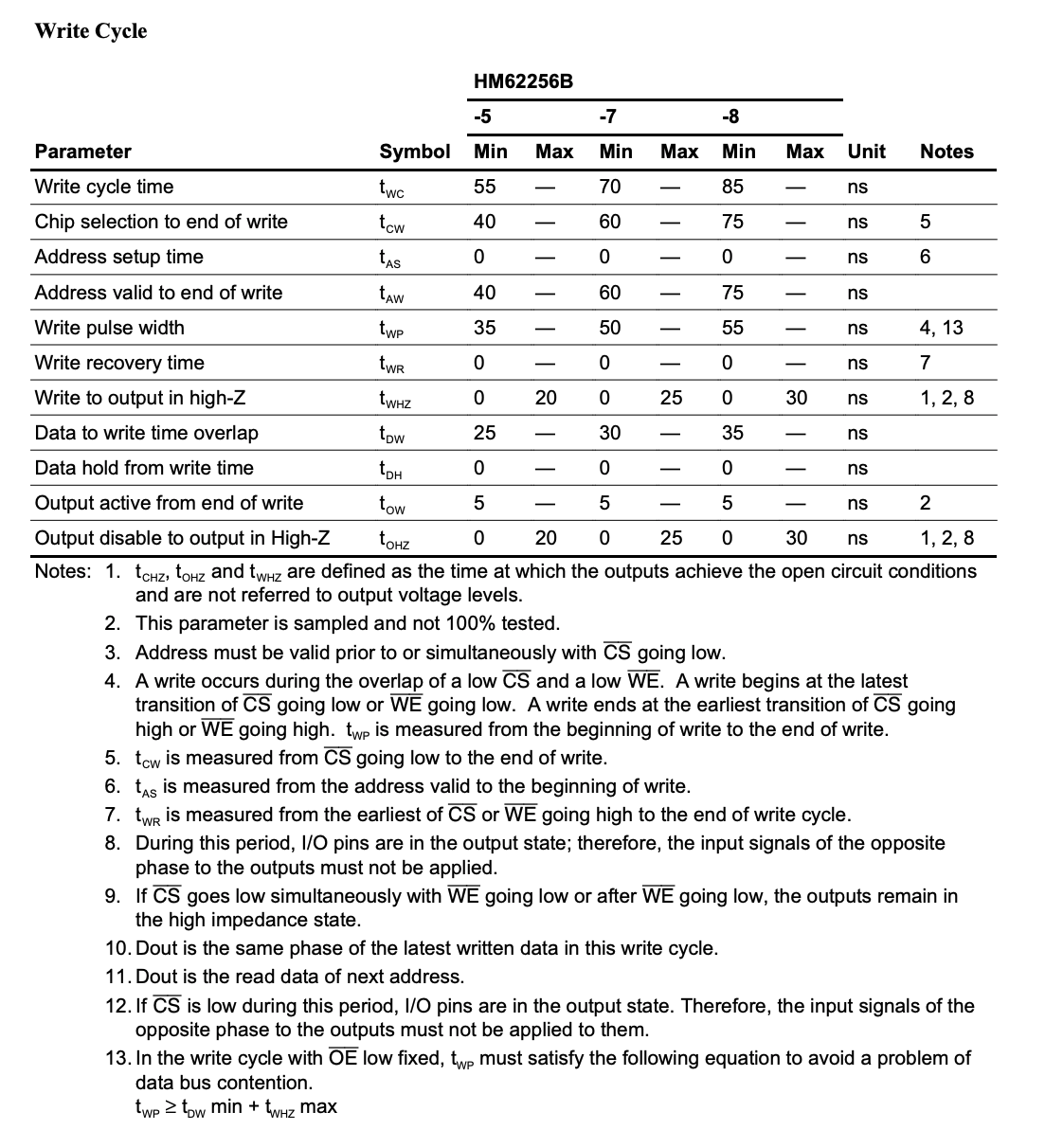

La Memoria HM62256B

Esta memoria es una static ram, esto implica que los datos que esta posee no necesitan ser refrescados cada cierta cantidad de ciclos de reloj sino que los mismos se conservan mientras esta no pierda electricidad.

Su denominación de 256 refiere a sus 256Kbits disponibles, estos están organizados en 32768 entradas de 8bits cada una lo que conocemos normalmente como 32Kbytes.

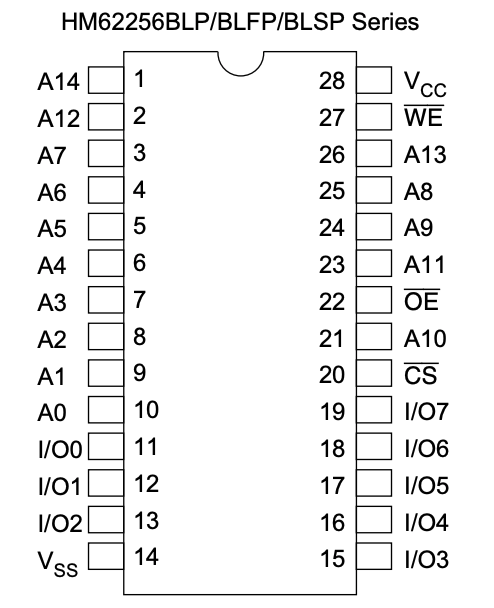

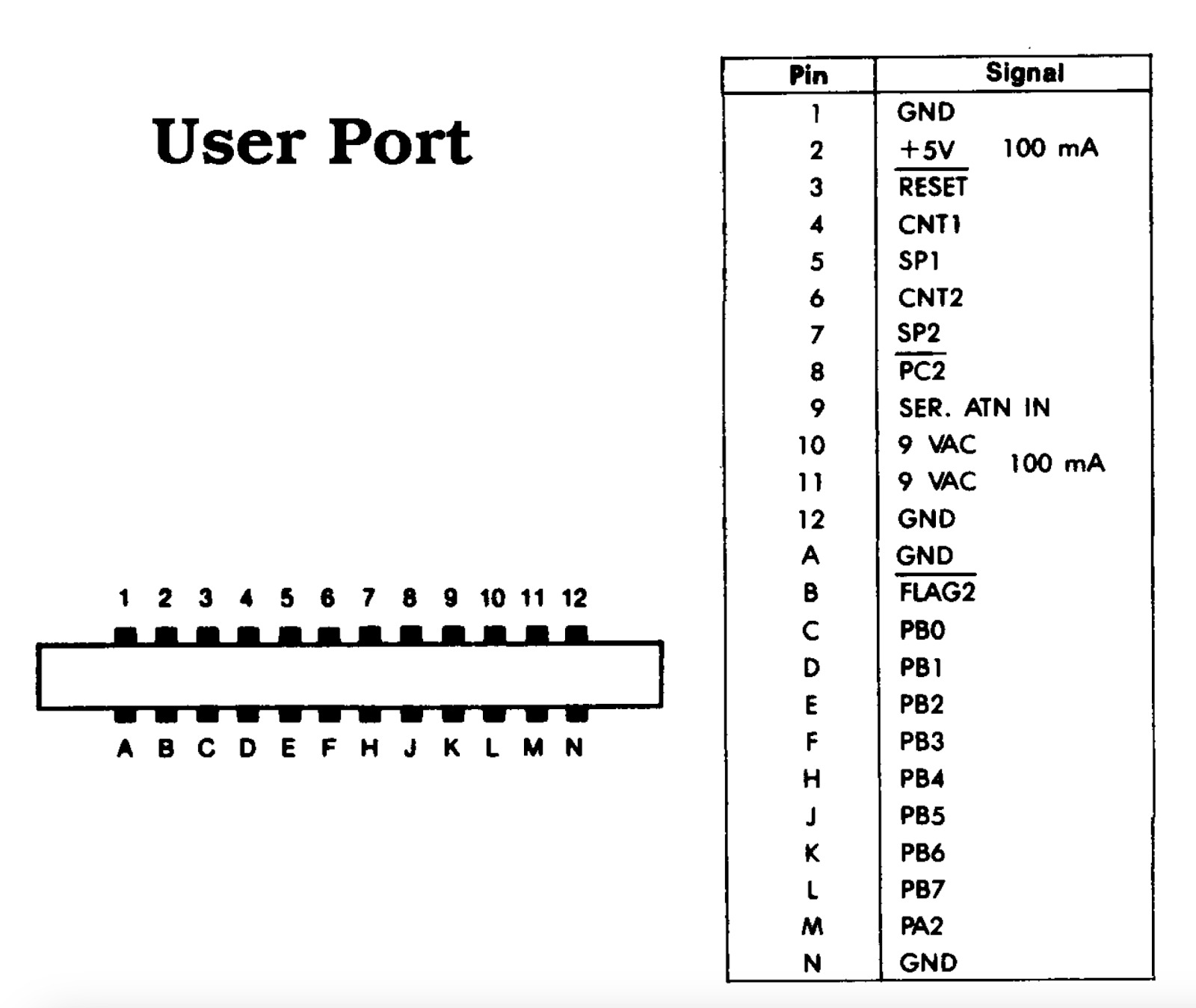

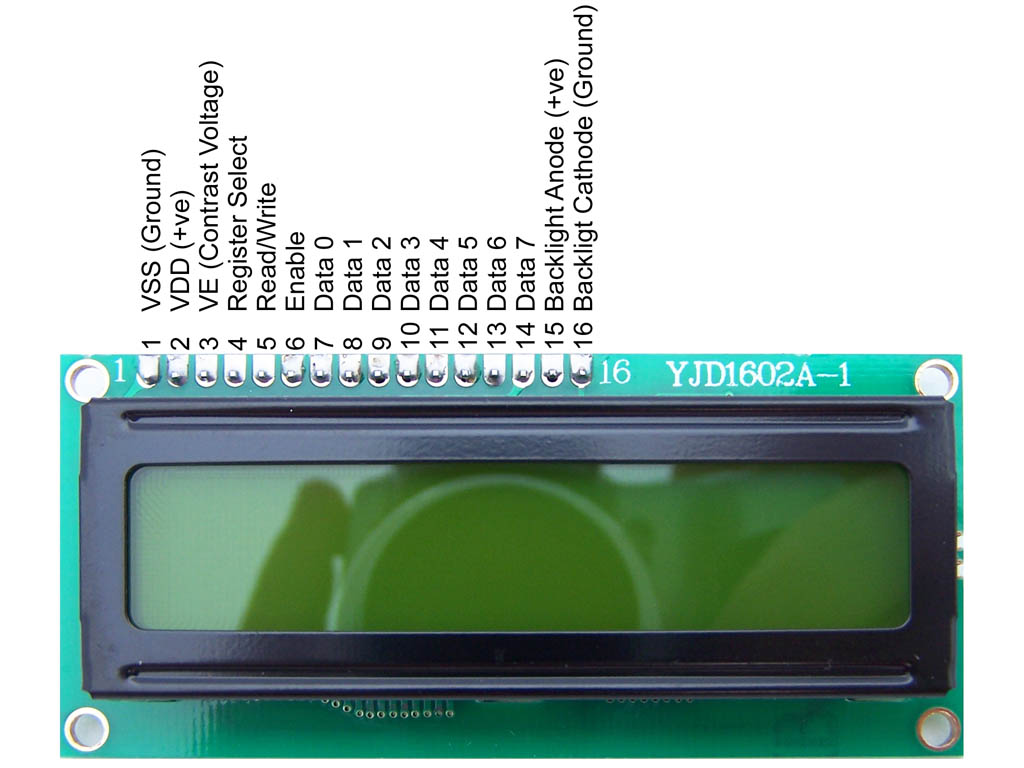

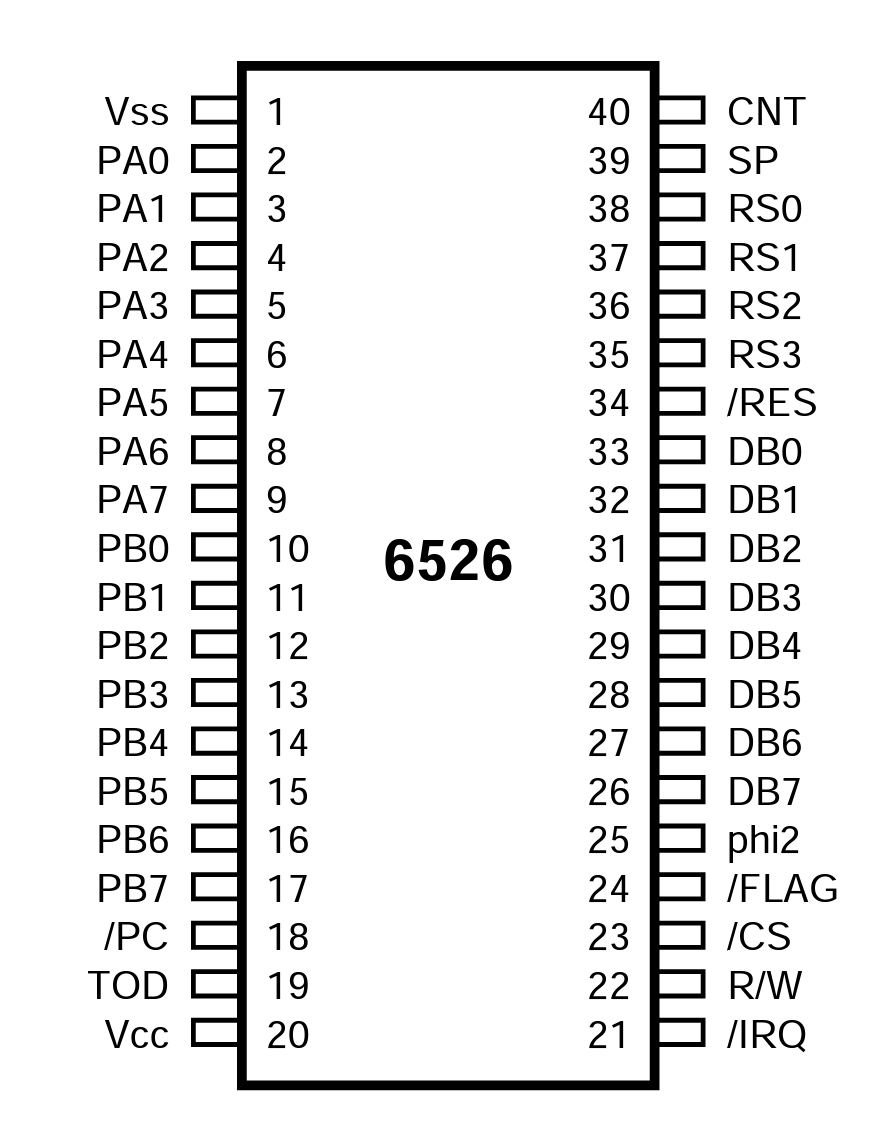

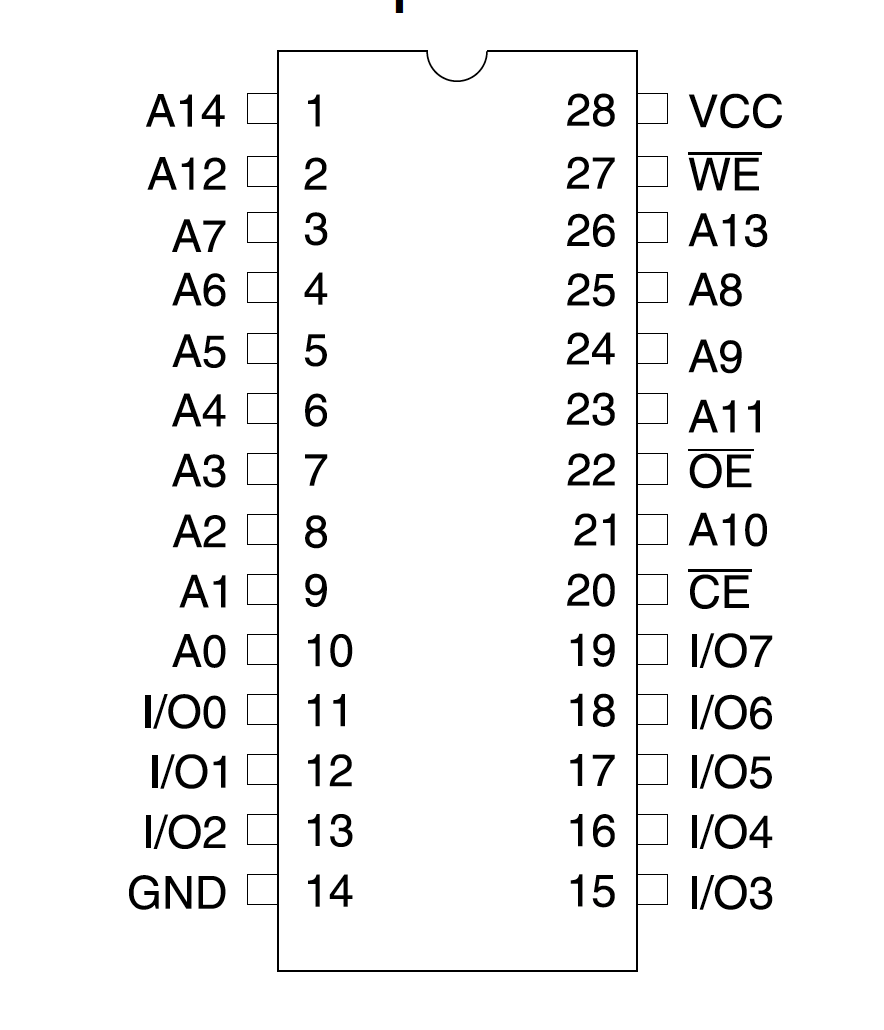

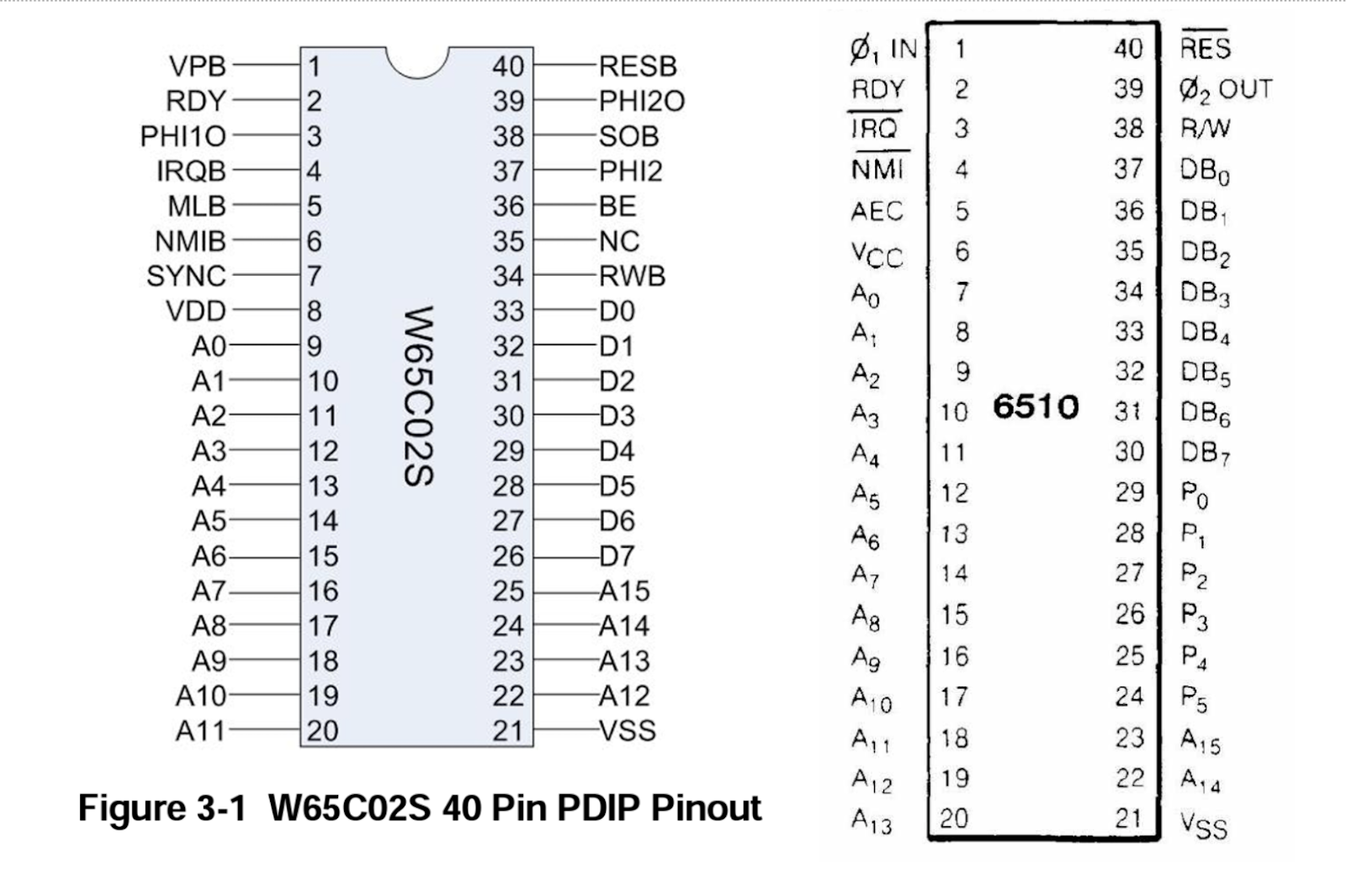

PinOut

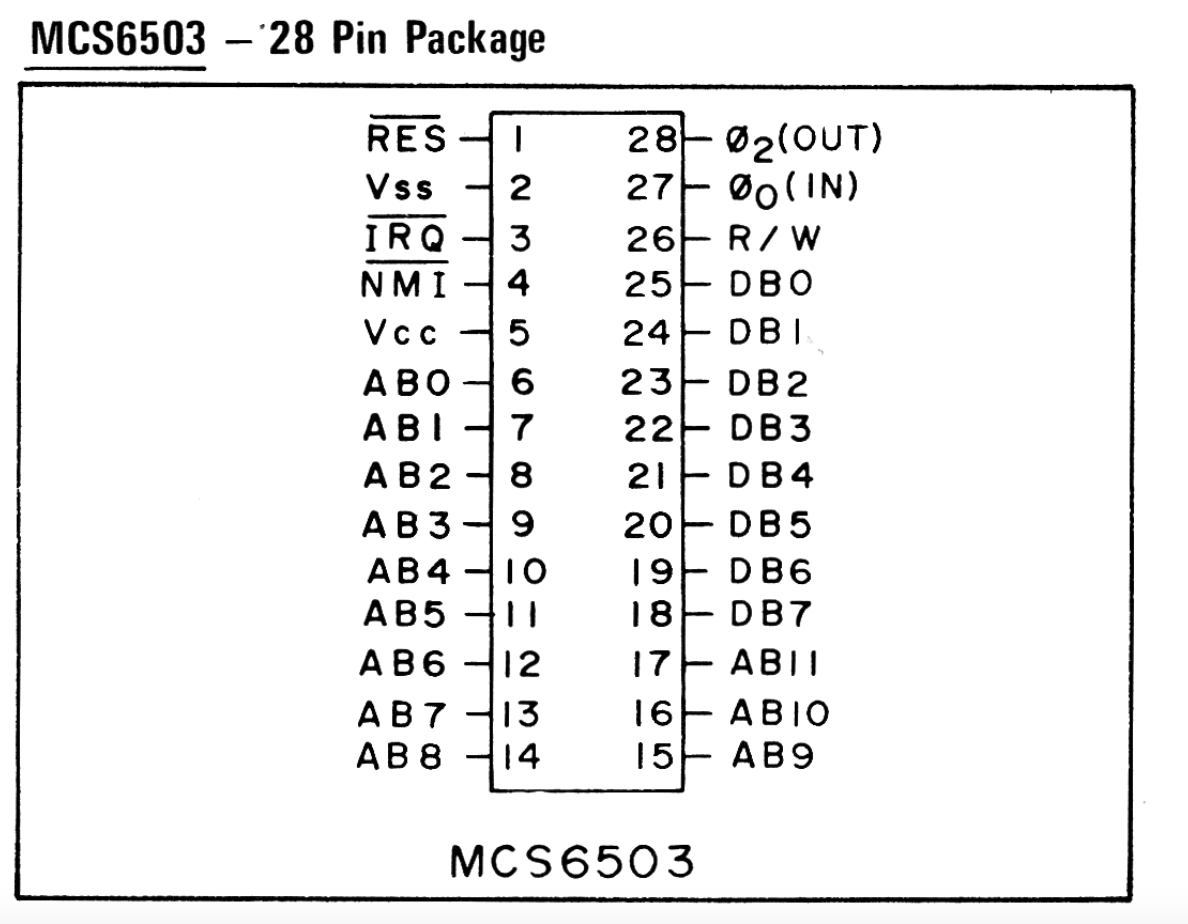

Este chip viene en formato DIP (Dual Inline Pins) de 28 pines y es muy parecido en su layout a la eeprom AT28C256 que vimos en un artículo anterior.

A14 – A0: Estos pines nos permiten seleccionar qué registro de ocho bits queremos acceder dentro de nuestra memoria, al ser 15 pines podemos direccionar 2ˆ15 = 32768 registros de 8 bits. Estos pines se conectan al bus de direccionamiento.

I/O 0 a I/O 7: Los pines de I/O es donde vamos a ver el contenido de cada registro previamente seleccionado para leer la memoria, o donde vamos a enviar los datos que tenemos para escribir la memoria. Estos pines se conectan al bus de datos.

VCC: En este pin es donde el chip espera una alimentación de +5Volts

GND: Este es el pin de referencia a tierra del chip

/WE: El pin de write enable al recibir una señal de low o 0 Volts permite grabar en los registros de la memoria. Como la estamos utilizando como una ROM conectamos este pin directamente a +5 Volts para que sea de sólo lectura. La barra / significa que este pin es active low con lo cual espera 0 Volts para activarse

/OE: El pin de output enable conecta o desconecta los pines de I/O del bus de datos. Si el pin está en +5 Volts la memoria se desconecta del bus de datos poniendo sus pines de datos en un estado de alta impedancia. La barra / significa que este pin es active low con lo cual espera 0 Volts para activarse

/CE: El pin de chip enable conecta o desconecta los pines del chip para una lectura o escritura trabajando en conjunto con /OE y /WE. Es active low con lo cual espera 0 Volts para activarse

Timing para una lectura

Cuando un procesador y una memoria necesitan comunicarse ya sea para lectura o escritura hay dos tiempos generales que tienen que ser compatibles: el tiempo en que la memoria responde y el tiempo que el procesador puede esperar. Para poder leer o escribir tenemos que realizar una combinación de 3 pines /WE /OE /CE. En el caso de una lectura WE debe estar en High y OE y CE en low, para una escritura los 3 pines deben estar en LOW.

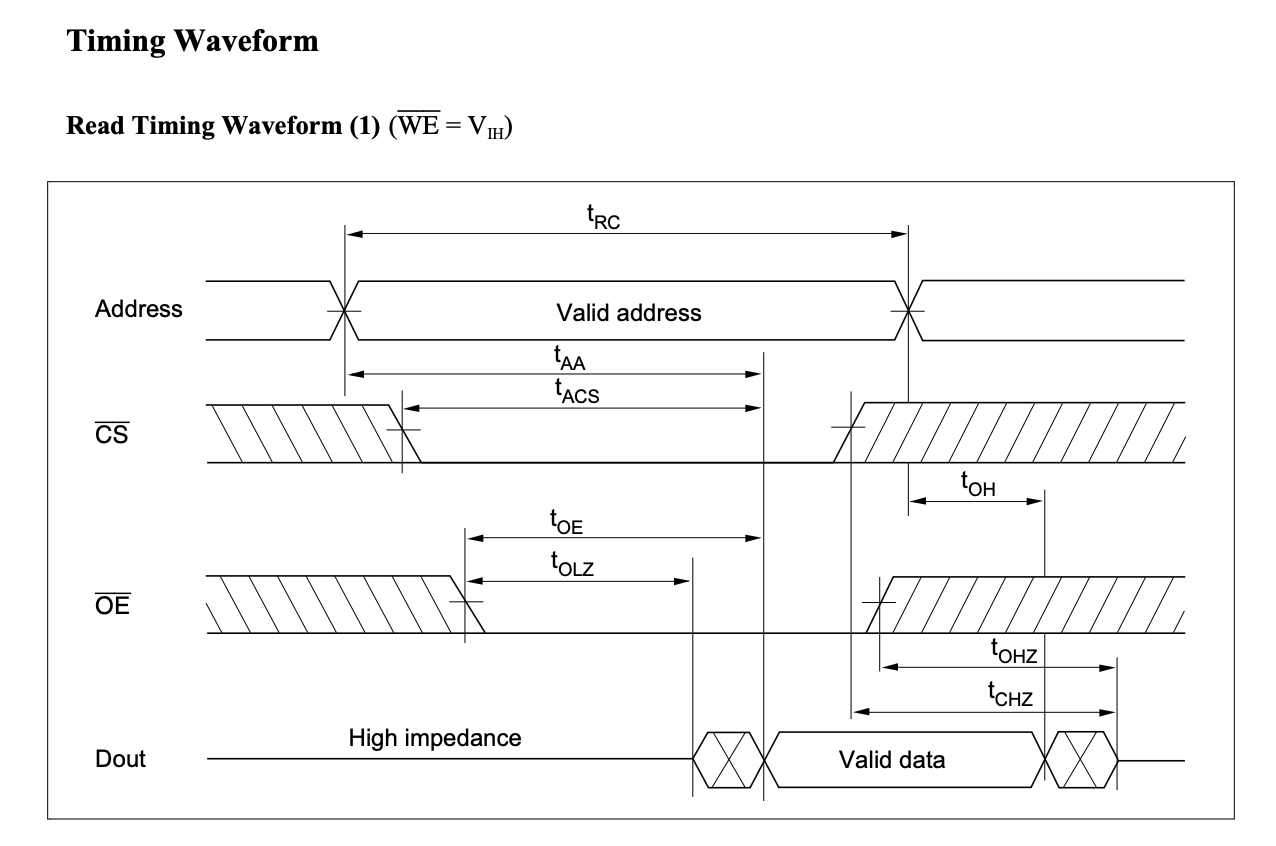

Timing de la Memoria en una lectura

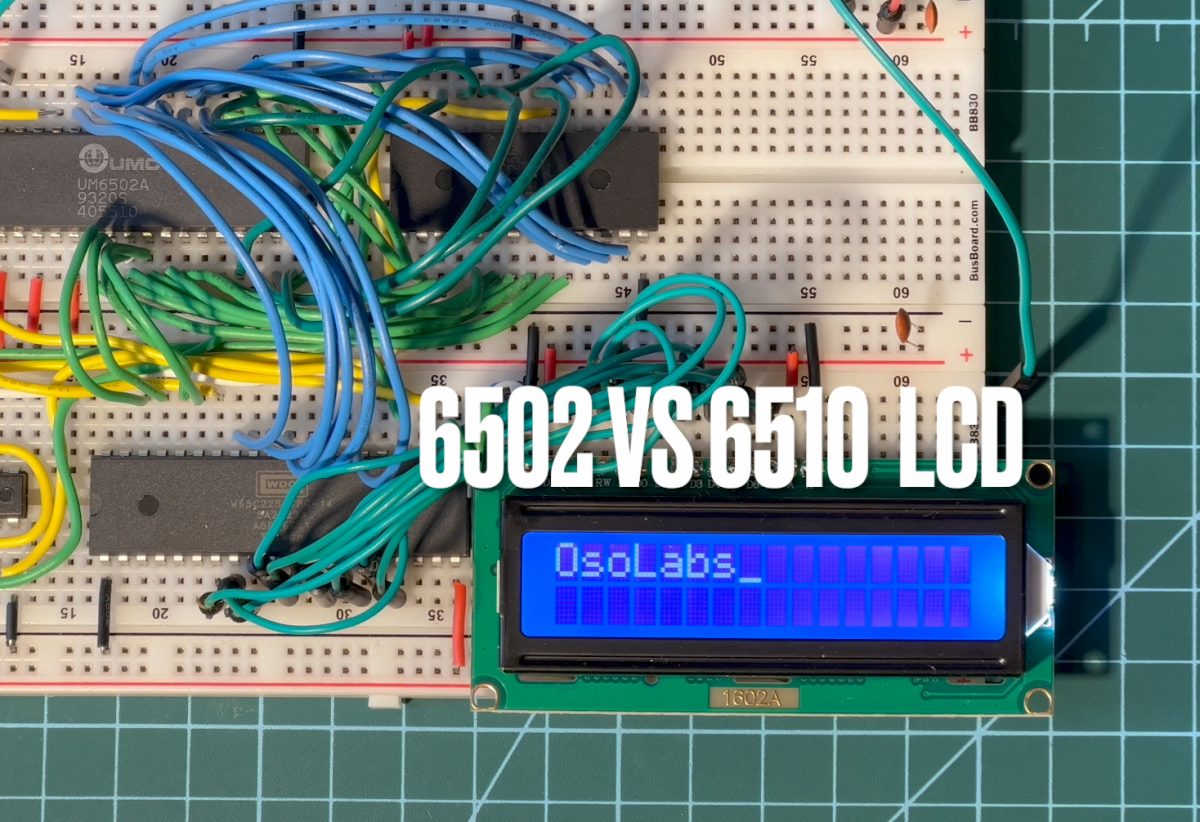

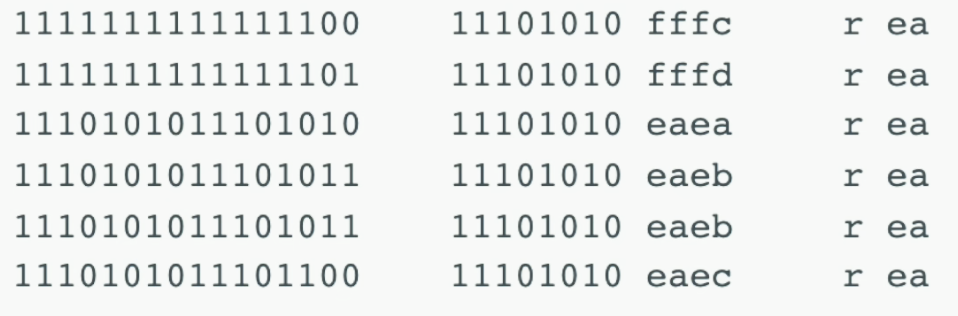

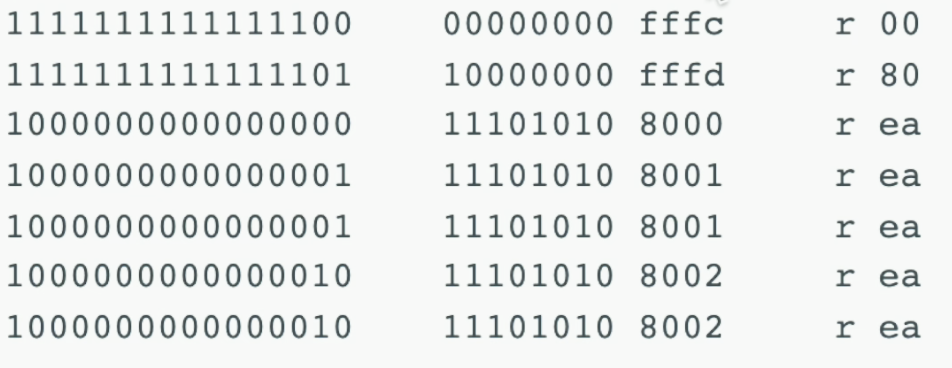

Para poder hacer una lectura de la memoria, primero el procesador debe poner en el address line o bus de direccionamiento la dirección donde está el dato que quiere leer, esta dirección consiste en los unos y ceros o los highs y lows de los pines A15 a A0.

La memoria no tiene inmediatamente disponibles los datos elegidos sino que tarda en buscar el dato y en poner el mismo en el bus de datos con sus 8 bits representados por los pines D7 a D0 y tarda en que estos estén estables, que sean válidos y que reflejen el valor interno en la memoria por lo que el procesador tiene que esperar un tiempo hasta que estos datos sean válidos y recién ahí leerlos, en el caso del datasheet del ejemplo 70ns como mínimo debe ser el tiempo de espera del procesador.

Hagamos el análisis paso por paso utilizando el siguiente diagrama.

Primero el procesador tiene que colocar los 16 bits del address line en forma correcta pero estos puede que no sean seteados al mismo tiempo o en algún orden específicos con lo que el bit 1 puede setearse luego el 15, luego el 12, etc. Tenemos que esperar hasta el punto donde comienza TRC o Read Cycle Time que es el momento donde el address bus tiene los 16 bits en forma correcta.

El procesador deberá esperar un tiempo tAA o Address Access Time, que es el tiempo para que los datos en el bus de datos sean válidos y con valores correctos. Cuando el tiempo tAA termina recién ahí los datos o bits o highs y lows que están en el bus son válidos y representan la dirección deseada.

Este tiempo posee dos subcomponentes tACS o chip Select to access time que es el tiempo que tarda el chip en activarse cuando recibe una señal low en el pin de Chip Select y también tOE o Output Enable to Output Valid, qué es el tiempo que tarda en activarse los pines de output luego de recibir un low en el pin de Output enable y que estos pines reflejen el valor correcto del contenido de la memoria en el bus de datos..

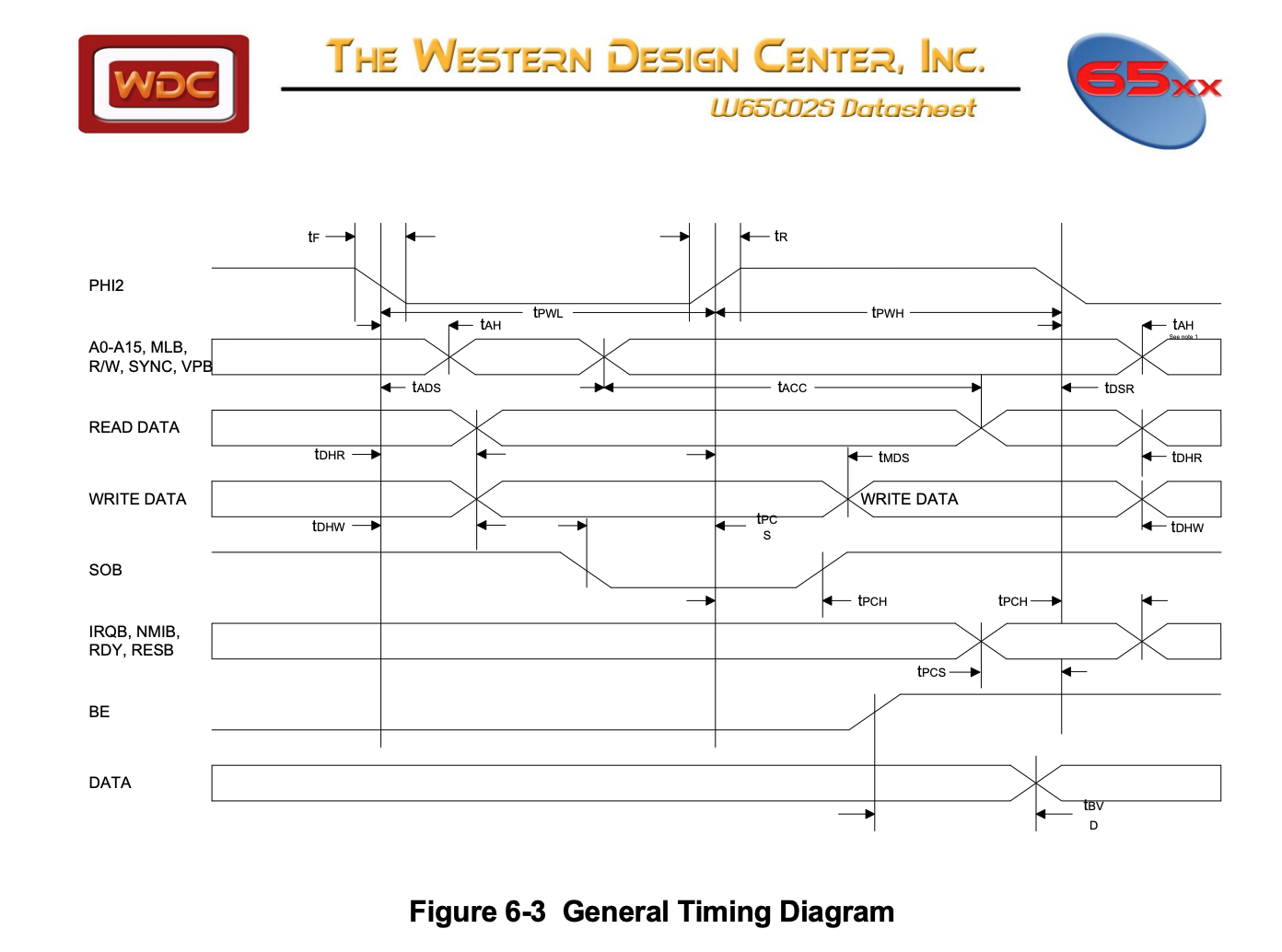

¿Cómo sabemos cuánto puede tardar como máximo el chip en darnos datos válidos una vez que tenemos un address válido en el bus de direccionamiento? Con una tablita de tiempos de acceso disponible en el datasheet de cada chip.

Si vemos para el chip de la familia HB62256B si termina el mismo en -7 el tiempo máximo de address access time o tAA es de 70 nanosegundos, podemos deducir que es tiempo máximo de tACS el chip select to access time o lo que tarda en activarse el chip ya que este timer tarda 70 ns y el de tOE de Output enable to output valid solo tarda 40ns como máximo.

tAA = 70 ns

tACS = 70ns

tOE = 40ns

Otro tiempo importante que vamos a utilizar en el futuro es el tOH o el Output hold time from address change, este tiempo es cuánto los datos vamos a mantenerse como válidos desde que cambió el address en el bus de direccionamiento, este es de 5ns

tOH = 5ns

Ahora cómo sabemos si el procesador que utilizamos puede esperar 70 nanosegundos? Estudiando el diagrama de timing del mismo,

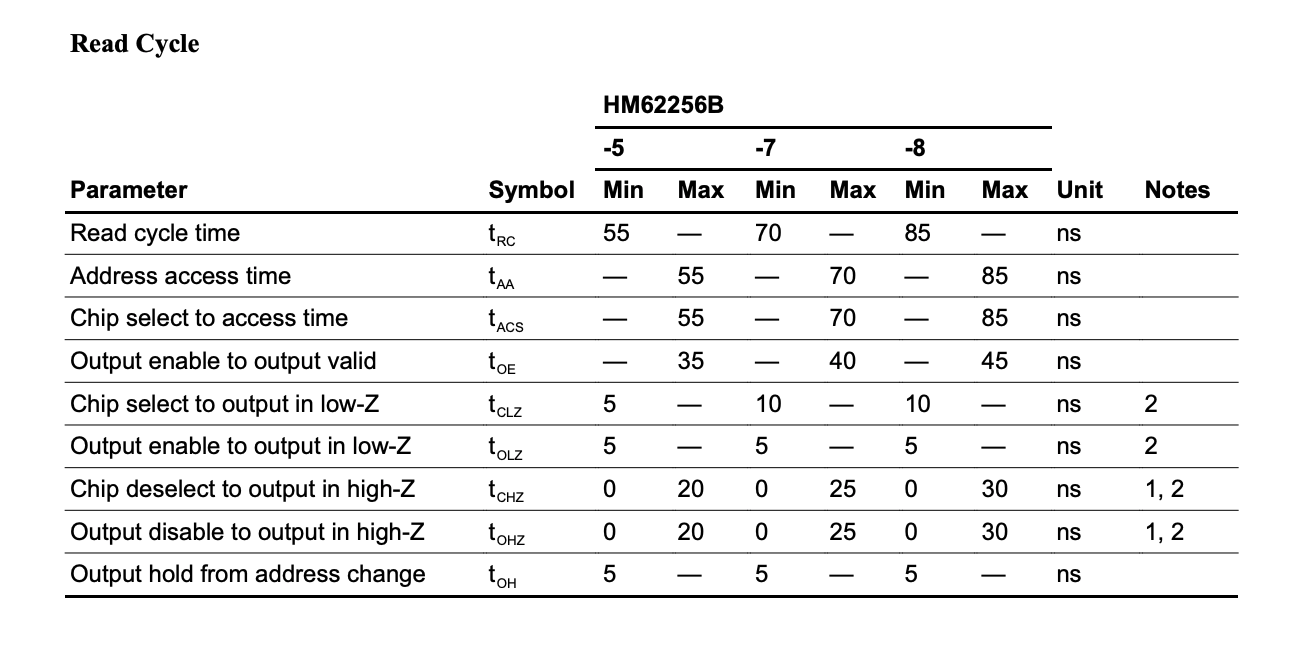

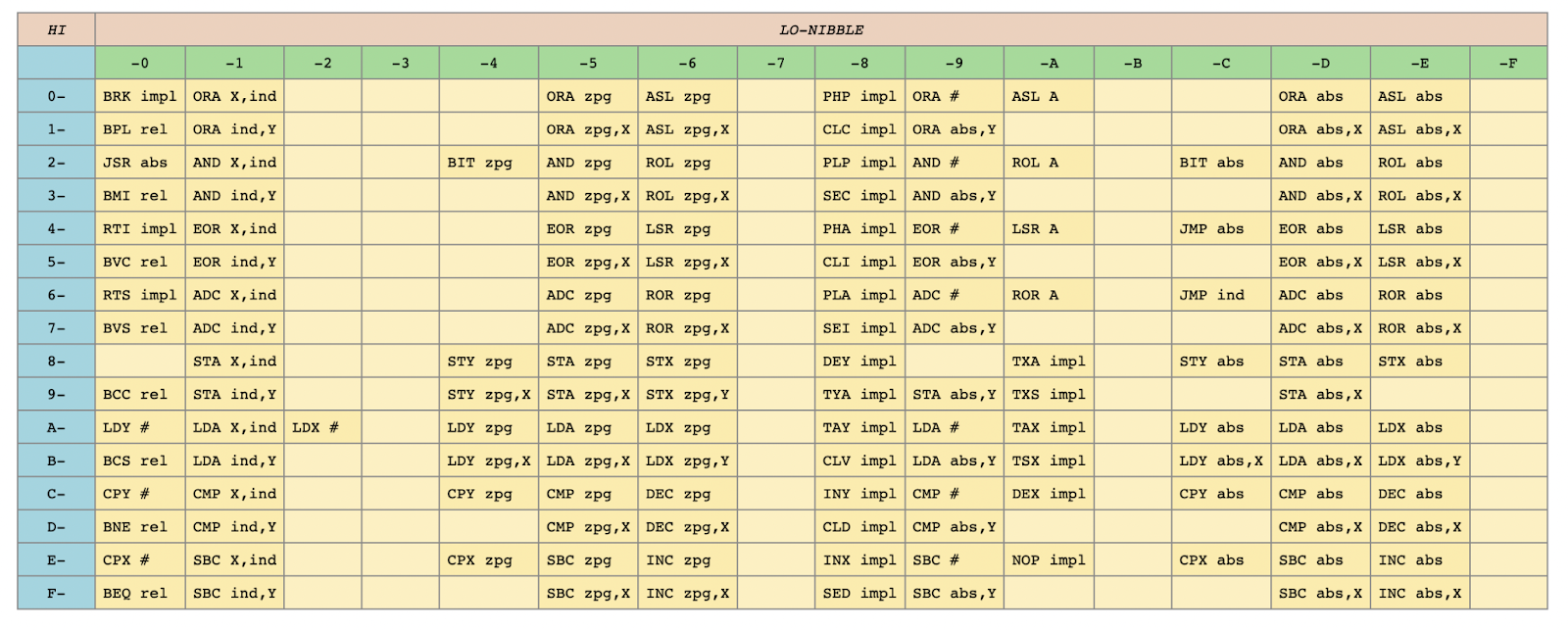

Timing del Procesador 6502 en una lectura

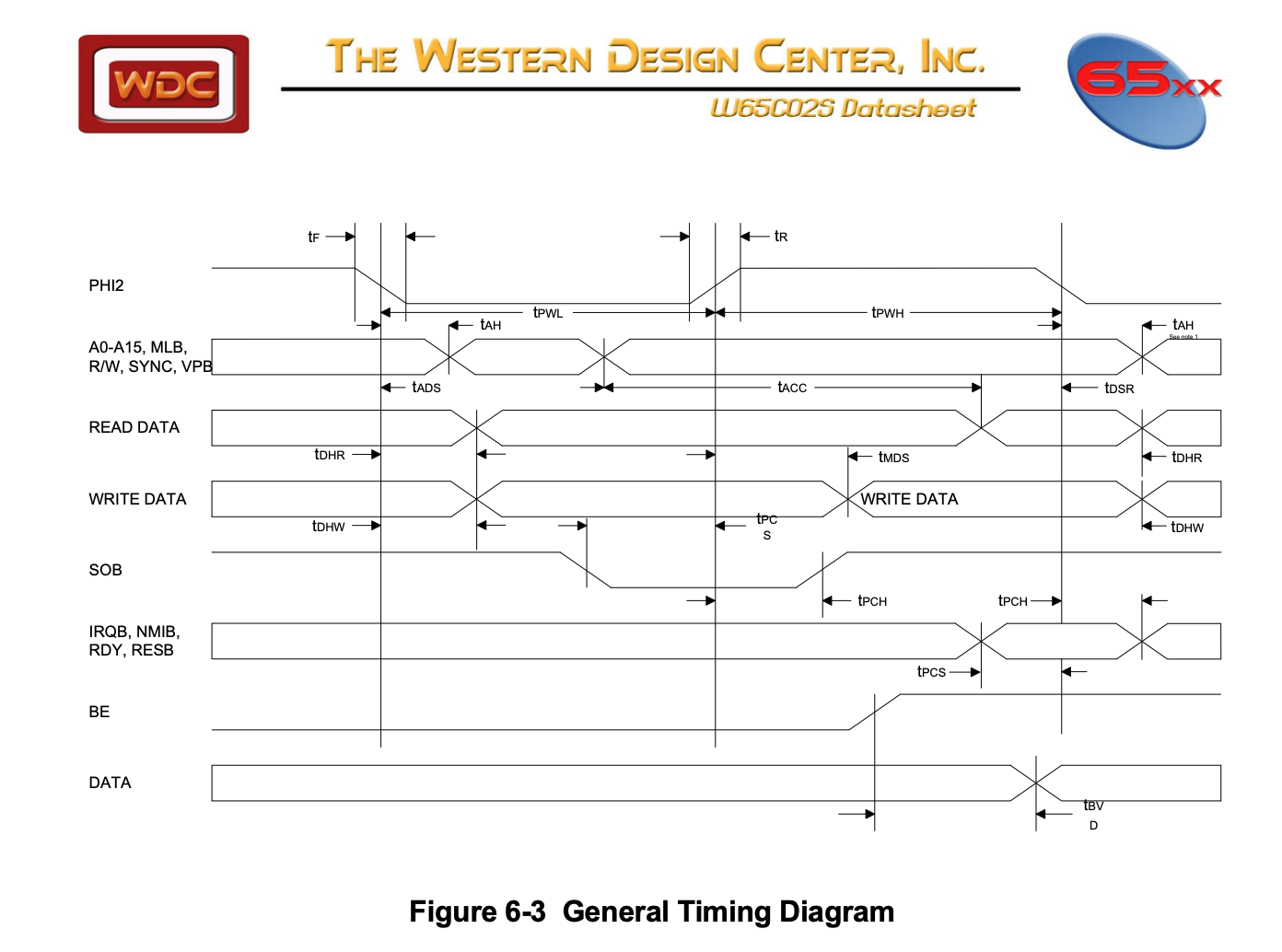

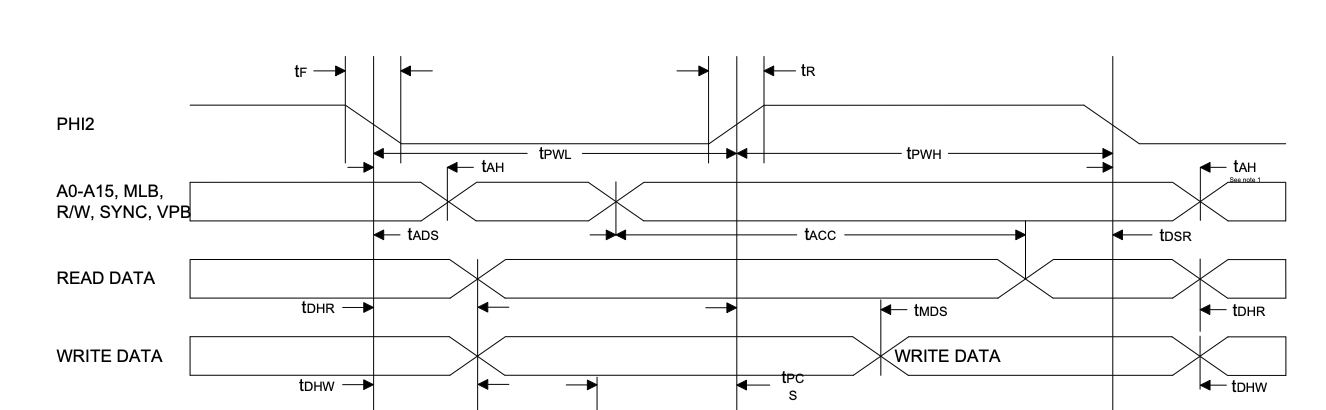

El siguiente es el diagrama de tiempos del procesador 6502 hecho por Western Design Center. El problema con este diagrama es que mezcla los tiempos de escritura y de lecturas al mismo gráfico por lo que construí un diagrama simplificado para poder entenderlos mejor.

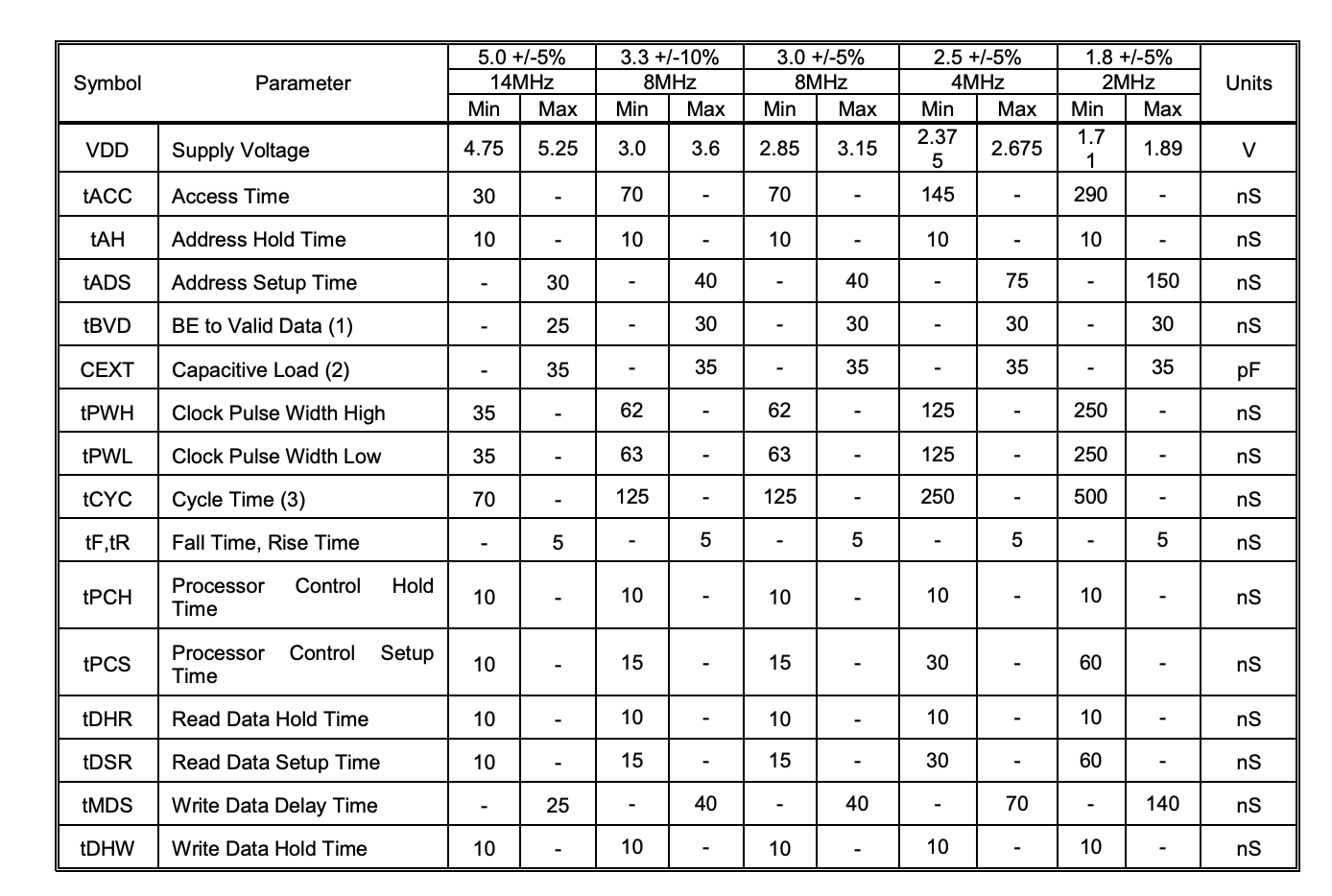

Por otro lado la velocidad de cada uno de estos intervalos va a depender de a que voltaje nosotros manejemos el cpu, como estamos usando +5 Volts esa es la columna que utilizaremos. Estos voltajes nos van a dar un máximo de 14Mhz para correr nuestro CPU pero lo vamos a estar corriendo a 1Mhz.

El ciclo del Reloj

El primer tiempo que nos interesa saber es el de un ciclo completo de reloj, este está representado en el diagrama como PHI2 y se divide en tPWL y tPWH (Clock Pulse Width Low y High respectivamente). Al usar un reloj de 1Mhz vamos a tener disponibles 1000 nanosegundos para todo el ciclo completo de reloj.

(1)

tPWL va de 0ns a 500ns

tPWH va de 500ns a 1000ns

El mínimo de tiempos de estos intervalos podría ser de 35ns cada uno o sea 70ns de ciclo de reloj si lo corriéramos a 14Mhz pero sabemos que por lo menos necesitamos 70ns para que nuestra memoria nos de los datos con lo cual esta velocidad no es adecuada.

Las preguntas que debemos responder primero para ver si podemos esperar esos 70ns que tarda en acceder a los datos la memoria que estamos utilizando es cuando el procesador configura el address en sus pines y cuando r ealiza la lectura.

Estableciendo el Address en el Bus de Direccionamiento

El segundo tiempo que vamos a tener que estudiar es el tADS o Address Setup Time , es el tiempo que le toma al cpu estabilizar los highs y lows en los pines del bus de direcciones. Y el tercer tiempo es el tAH o Address Hold Time, por cuánto tiempo esos highs y lows son válidos en el bus de direcciones.

(2) tADS = 30ns

(3) tAHT = 10ns

El tADS comienza en el falling edge del comienzo del ciclo del reloj.

El tAHT se mantiene desde el falling edge (transición de High a Low) del final ciclo del reloj.

Leyendo los datos

El cuarto tiempo a estudiar es el tDSR o Data Setup Time, que es cuánto tiempo tardan en estabilizarse los highs y lows en el bus de datos y el quinto tiempo es el tDHR o data Hold read time o cuánto tiempo esos datos són válidos.

(4) tDSR = 10ns

(5) tDHR = 10ns

El tDSR termina desde el falling edge (transición de High a Low) del ciclo del reloj en ese falling edge es cuando ocurre la lectura.

El tDHR son por lo menos 10ns desde el momento de la lectura.

Tenemos que asegurarnos que la RAM esté dando datos válidos durante tDSR + tDHR. Tenemos que asegurarnos que la RAM esté dando datos válidos durante tDSR + tDHR.

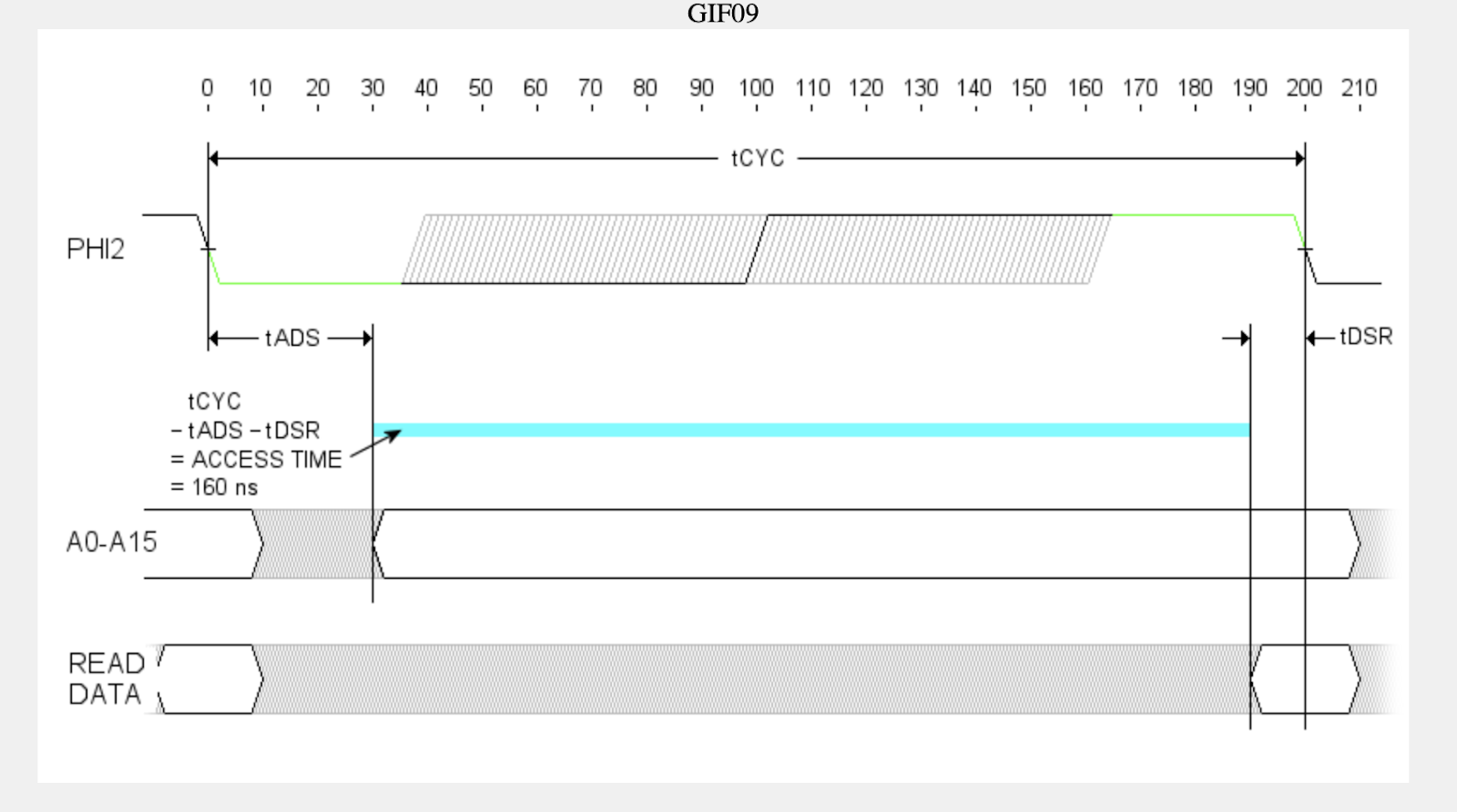

Si hacemos un esquema podemos ver:

0ns a 30ns necesitamos que el address sea estabilizado tADS

30ns a 1010 ns el address el válido tAHT

990ns a 1010ns los datos tiene que ser válidos tDSR + tDHR

Con lo cual la ram tiene 990 – 30 = 960ns para poder dar los datos en el bus, pero como vimos la RAM sólo tarda 70ns como máximo para darnos los datos por lo que tenemos mucho tiempo disponible.

Pero por cuánto tiempo la RAM mantiene los datos válidos en el bus? Para esto está el timer tOH de la RAM que es de 5ns a partir de que cambia la dirección de la ram, pero la dirección cambia recién en el ns 1010 que es cuando expira el timer de address hold time del procesador lo que nos da unos 5ns extras para la lectura.

990 ns a 1015ns la RAM da valores de highs y lows válidos en el bus de datos

Por esto podemos hacer la lectura por que el procesador requiere de 10ns después del momento de la lectura y la RAM mantiene los datos válidos por 15ns

De forma similar a como hicimos este análisis podemos realizar lo mismo para la escritura de la memoria variando solo algunos valores de los parámetros.

Un gran lugar para poder ver alternativamente como funcionan los diagramas de tiempo del 6502 es este sitio donde se ve muy bien visualmente Visual Guide to 65xx CPU Timing

Timing para una escritura

Con la información que ya tenemos de interpretar cómo se hace una lectura encaremos la escritura de datos en la memoria.

Timing de la Memoria en una escritura

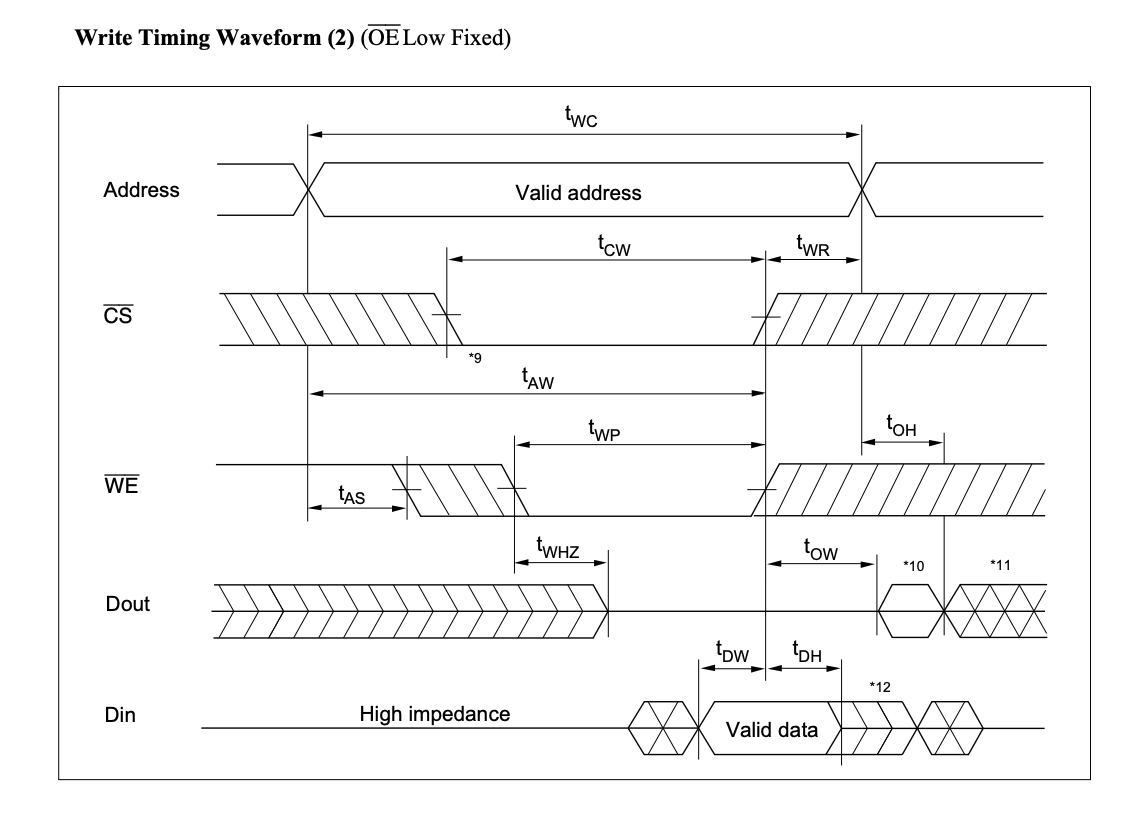

Veamos este nuevo diagrama de tiempos para la escritura.

Y también los nuevos valores mínimos y máximos para estos parámetros

Este diagrama asume que el pin de OE output enable está fijo en Low y según la nota 4 la escritura se va a realizar cuando CS y WE ambos estén el Low.

Comienza el tiempo tWP o Write Pulse Width cuando el último pin entre WE y CS entren en low y dura hasta que el primero de ellos pase a High.

tWP = minimo de 50ns

Los datos deben ser válidos en el bus por lo menos desde tDW o Data Write time overlap y mantenerse válidos por un período tDH o Data Hold form write time

tDW = 30ns

tDh = 0ns

Con lo cual por lo menos 30ns antes de que WE o CS pasen a ser High los datos deben mantenerse como válidos.

Si analizamos lo que puede pasar, el bus de datos puede tener cualquier información errónea sin problemas y esos datos se escriben en la ram, pero por lo menos 30ns antes de que se termine la escritura los datos deben ser válidos ya que estos quedarán en la RAM, estos datos válidos pueden ser mantenidos por 0ns enel bus si queremos ya que ya han sido escritos ya que el mínimo de tDH es cero.

Timing del Procesador 6502 en una escritura

Veamos este nuevo diagrama de tiempos para la escritura.

Sabemos que los siguiente tiempos se cumplen debido a nuestro análisis anterior:

0ns a 30ns necesitamos que el address sea estabilizado tADS

30ns a 1010ns el address el válido tAH

1000 ns a 1010ns tDHR

Los datos se vuelven inválidos al final de tDHR que coincide con tAH y con un nuevo timer tDHW o Write Data Hold Time

tDHW = 10ns desde el falling edge fin del clock cycle

1000 ns a 1010ns tDHW

El write ocurre en el falling edge del final de clock cycle. Pero para que la escritura sea correcta los pines de CS o WE tienen que ser high antes de que el address, los datos o el write hold time sean inválidos.

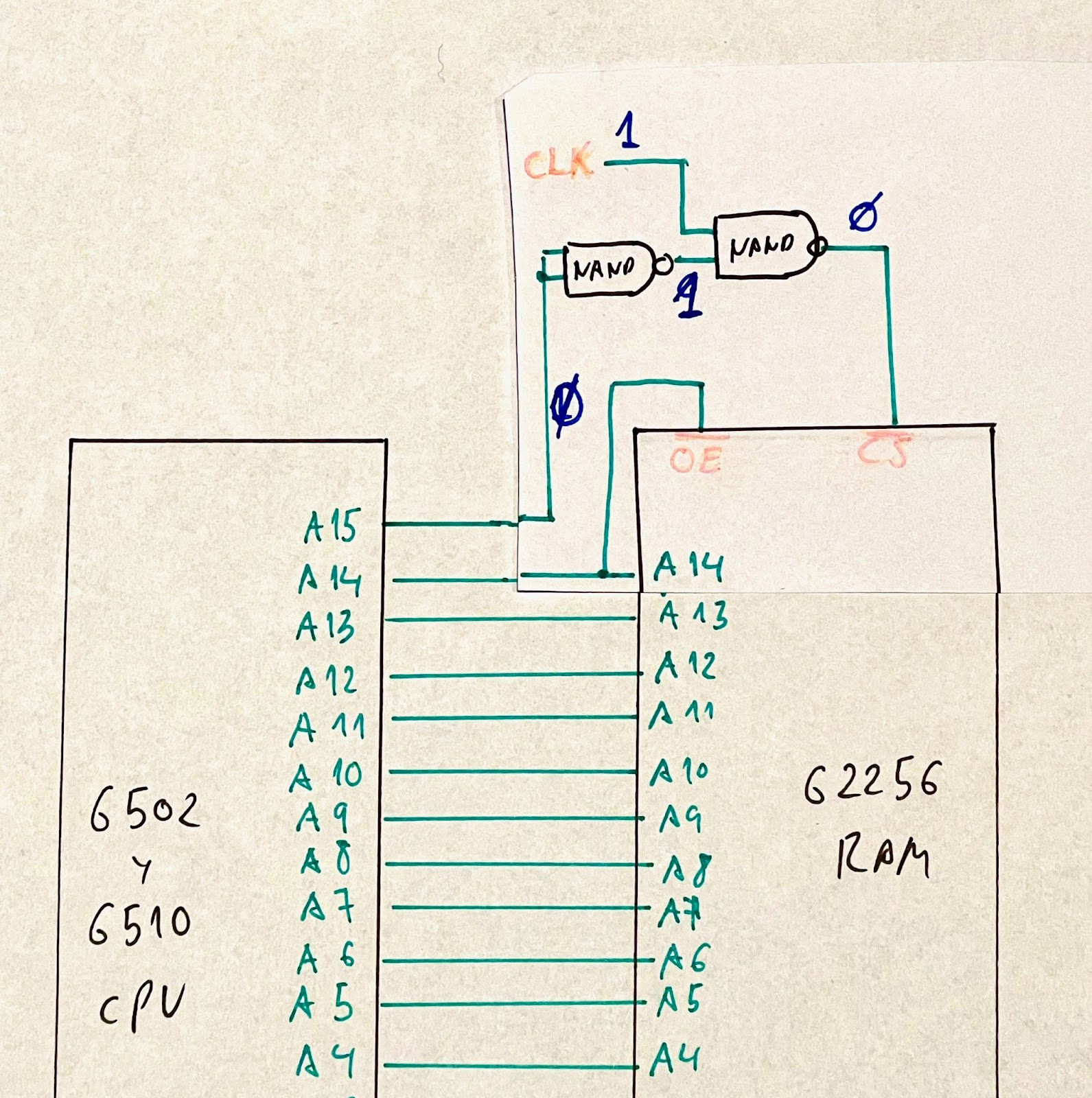

Si conectamos el pin de chip select CS a cualquier de las address lines estaríamos en problemas ya que debemos asegurar que el pin CS sea high mientras todavía todos los pines de address son válidos y todos los pines de datos son válidos, pero no tenemos forma de poder apagar un pin antes que los otros asegurándonos que sea siempre así.

Lo mismo nos sucede con el pin de R/W del procesador no hay forma de garantizar que vaya a cambiar antes que los pines de address.

Con lo que nada nos asegura que CS o WR pasen a ser High (terminando la escritura) antes de que el address y los datos seán inválidos.

Para solucionar esto podemos hacer que el CS chip select pin sólo sea LOW durante el ciclo de pulso alto del reloj o tPWH de 500 a 1000 ns, de esta forma nos aseguraremos que el address bus tenga direcciones válidas y que unos nanosegundos tDW antes de apagarse el CS tenemos todavía datos válidos, ya que los hold timers de tAH y tDW nos mantendrían valores válidos en address y data bus respectivamente aún después de poner el High el pin de CS. En nuestro ejemplo serían 10ns extras.

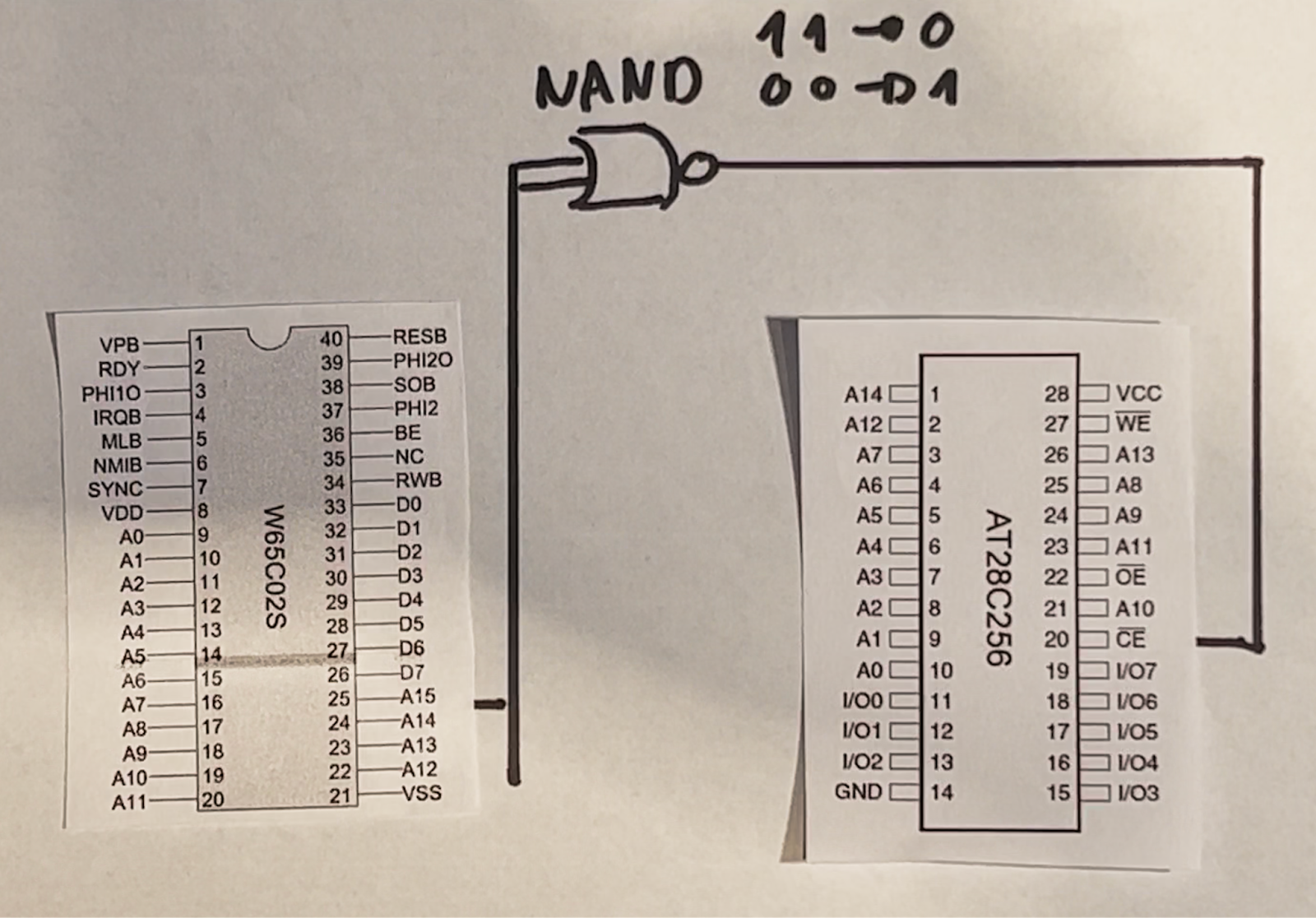

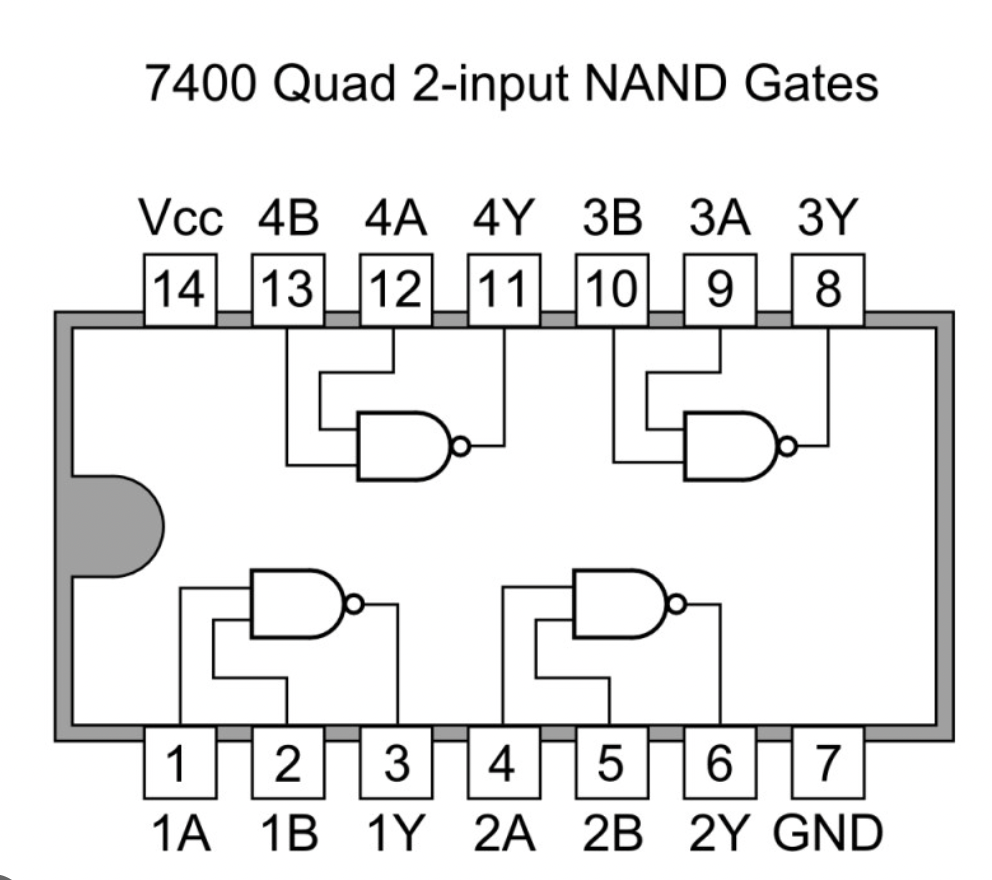

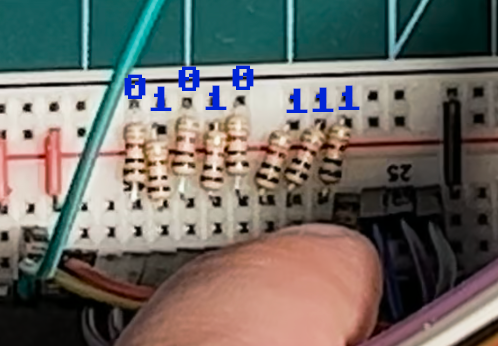

Para lograr esto podemos conectar el pin a15 si lo usáramos para seleccionar nuestro pin de chip select conectado a través de dos compuertas nand de forma tal que solo en el pulso high del reloj y cuando el pin a15 sea cero el pin de la memoria de chip select reciba un cero o low.

Al agregar dos compuertas nand debemos sumar un tiempo más que el que tarda la compuerta en evaluar sus inputs y darnos un output, este tiempo se llama maximum propagation delay (tPHL).

En el caso de las compuertas que utilizamos este es de 25ns al usar 2 vamos a tener como máximo 50ns de delay, lo que implica que la señal de chip select va a ir a low 50 ns después de que si no usáramos las compuertas, en este setup ese tiempo no influye ya que tenemos 960ns disponibles con el address valid antes de que los datos estén válidos (llendo de los 30ns a los 990ns) esto nos llevaría sólo al intervalo 80ns a 990ns no implica problema alguno.

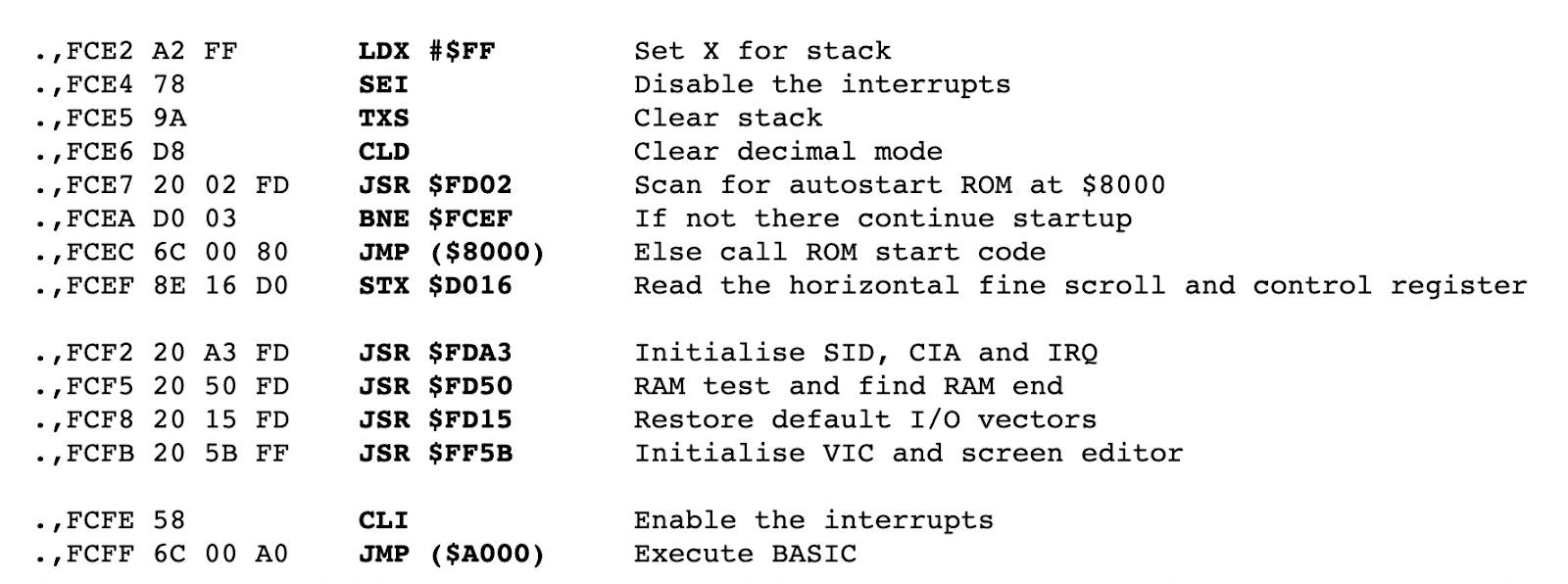

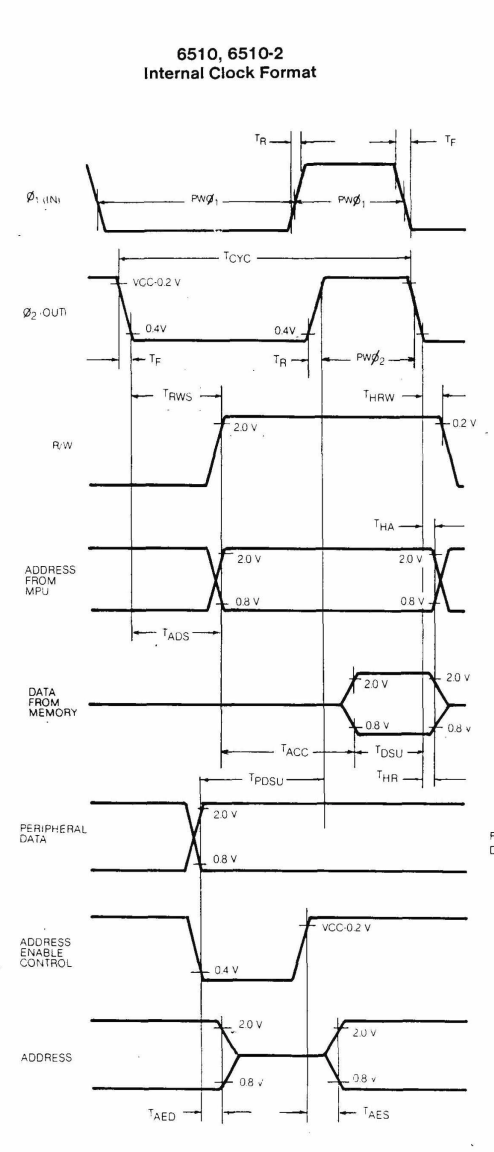

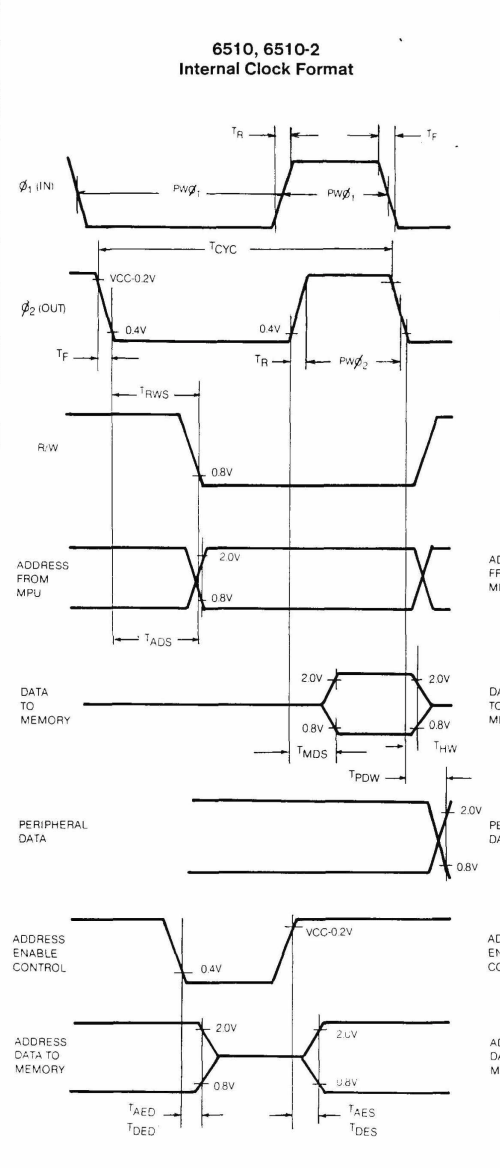

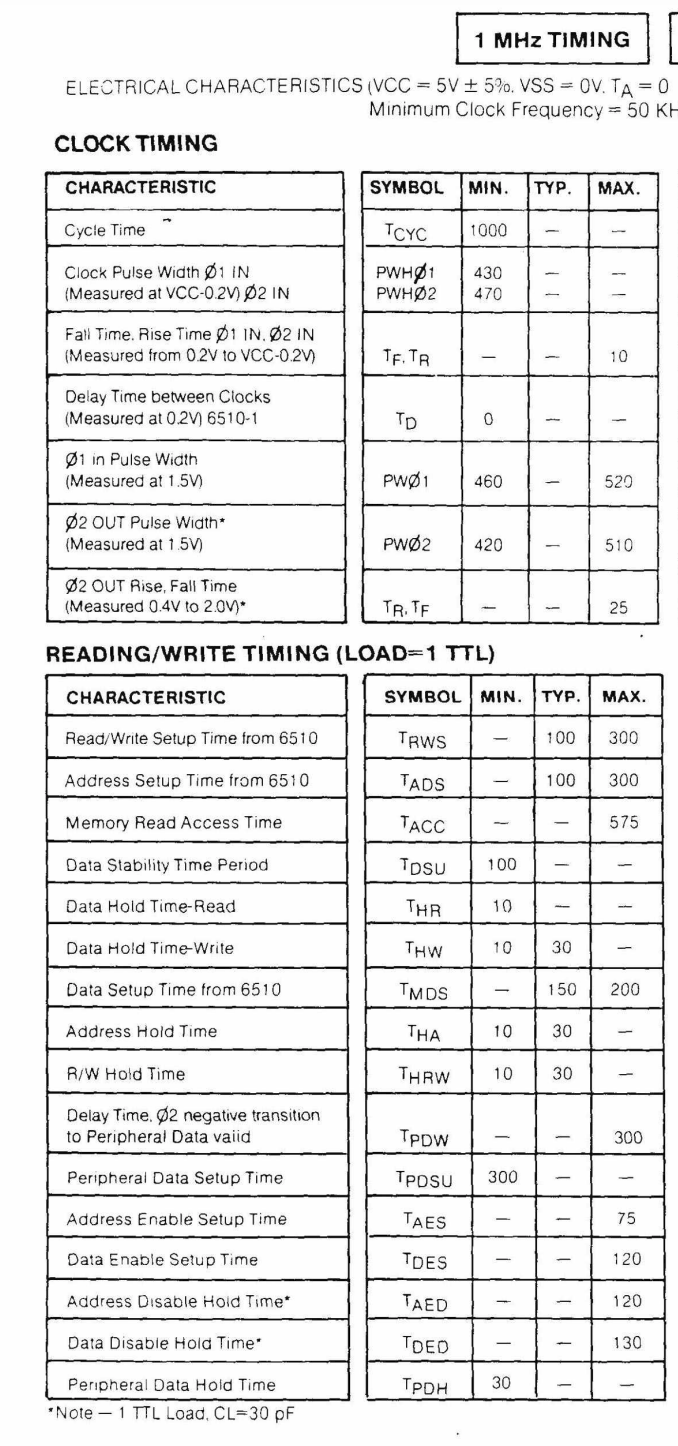

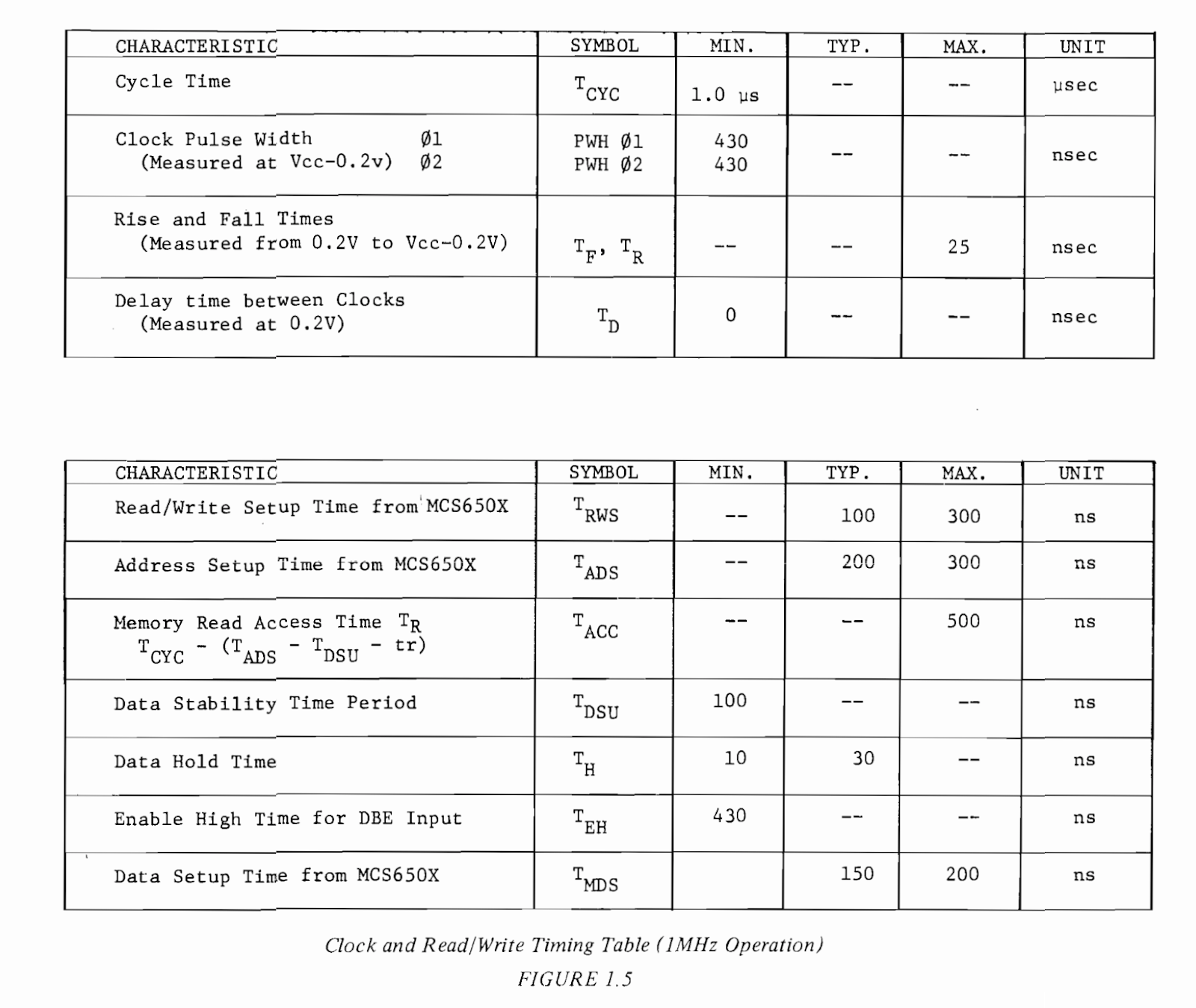

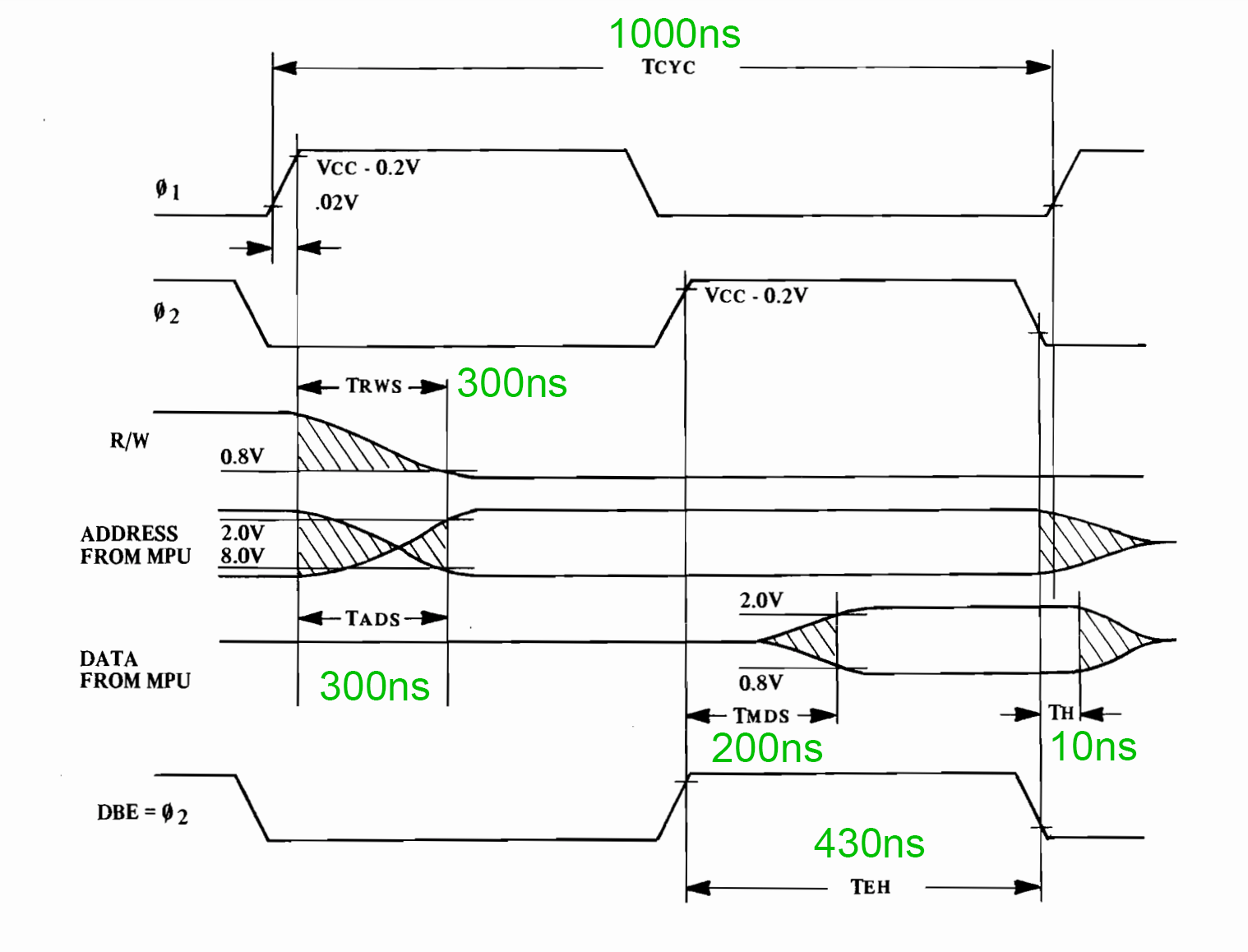

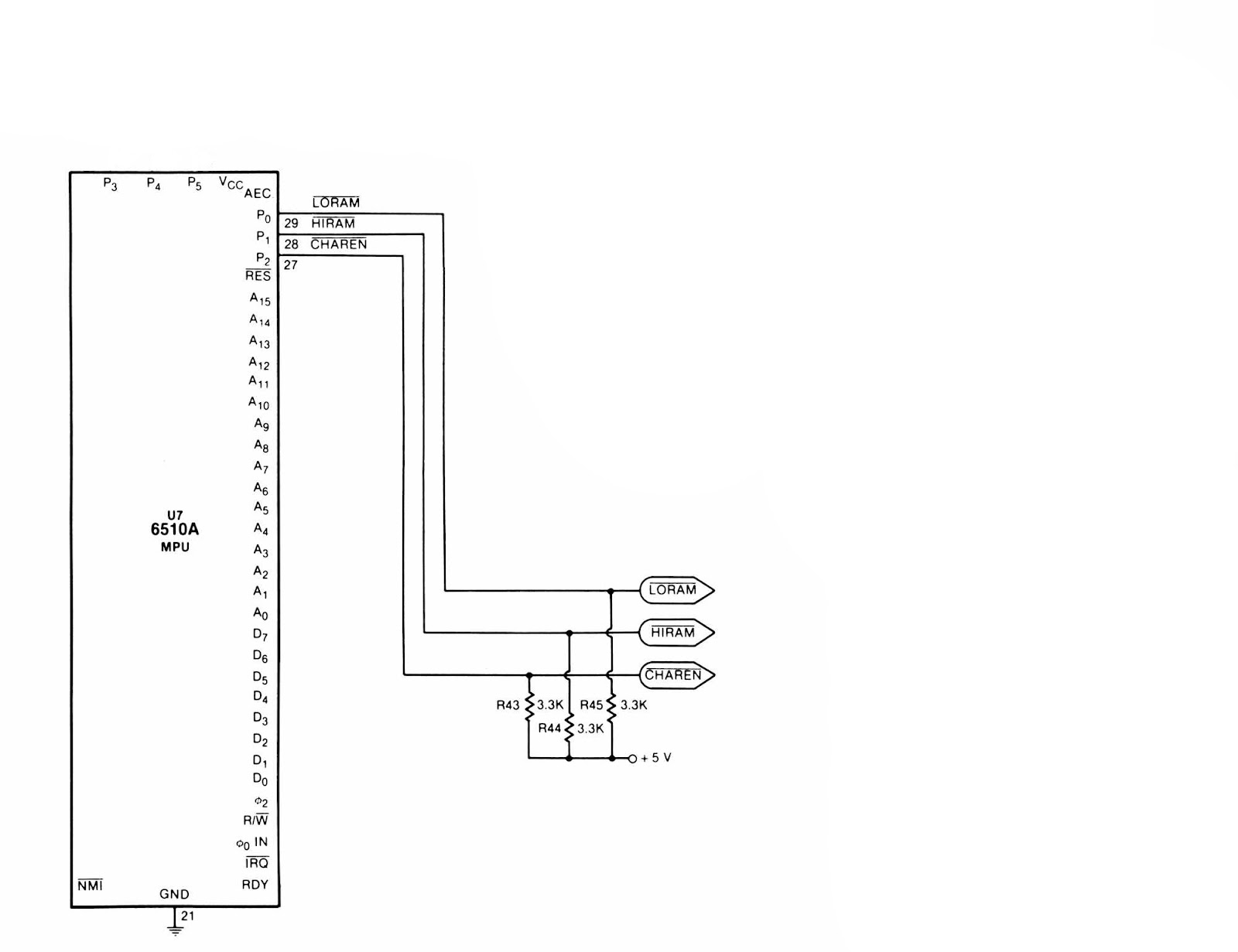

Timing en el procesador 6510

El timing en el 6510 es bastante más lento que en el 6502 y eso debemos tomarlo en cuenta, observemos estos valores y diagramas del datasheet original, el primer diagrama es de lectura y el segundo tiempos de escritura.

También tenemos algunos tiempos diferentes que los del 6502 más moderno

Así por ejemplo podemos observar el timer tADS o Address Setup Time el cual tarda 300ns en lugar de los 30ns del 6502 moderno. Si tuviéramos que hacer la cuenta con los tiempos para nuestra memoria ahora deberíamos comenzar así:

tADS = 300ms

tAH = 10ms

tDHR=tHR=10

0ns a 300ns necesitamos que el address sea estabilizado tADS

300ns a 1010ns el address el válido tAH

1000 ns a 1010ns tDHR

Y nuestra RAM muestra datos válidos desde

(tADS+tAA) a (tAH+tOE) = 300ns+70ns a 1010ns + 5ns

370ns a 1015ns la RAM da valores de highs y lows válidos en el bus de datos

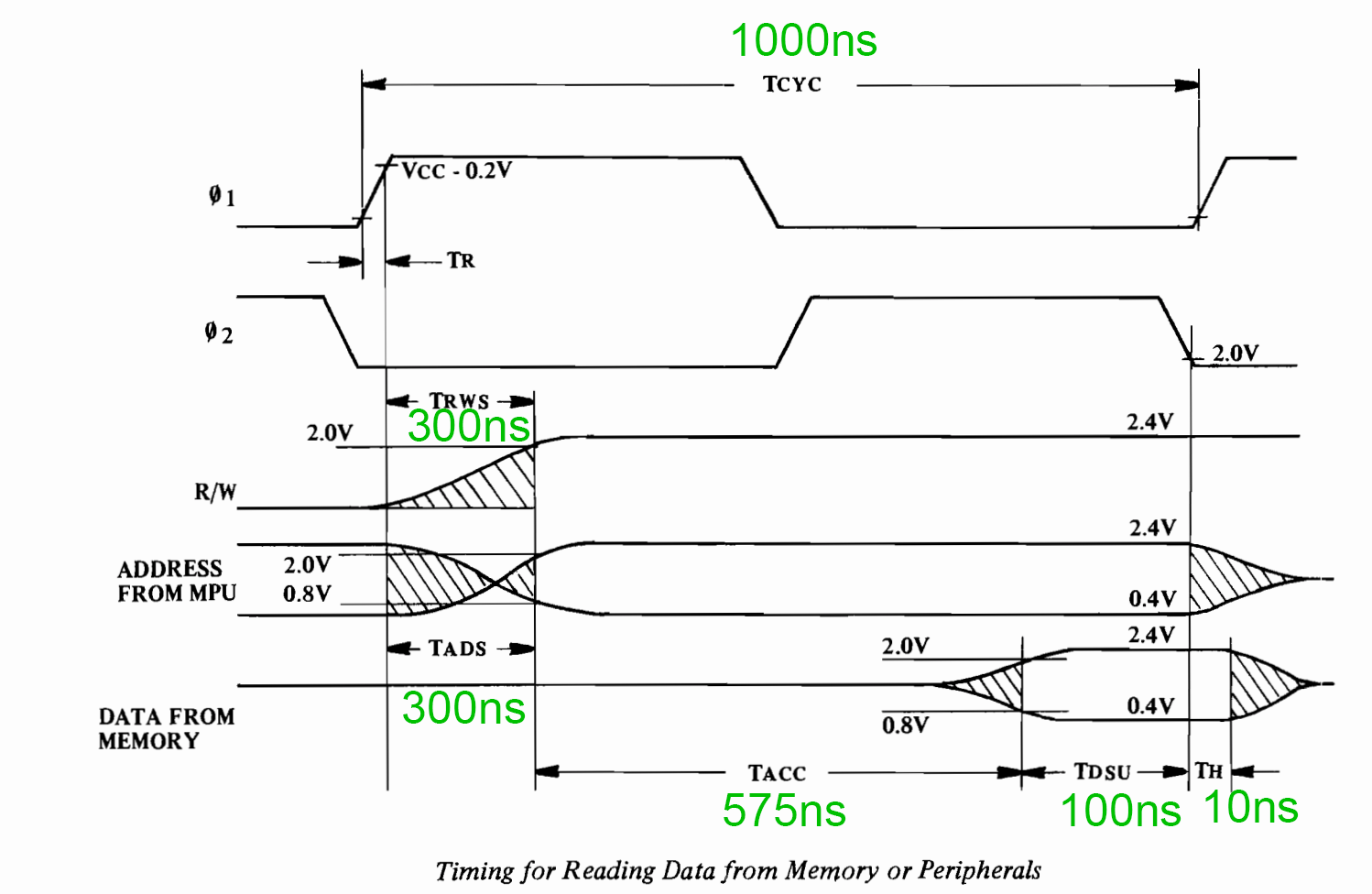

Si nos referimos al manual de Hardware de la línea de procesadores 6500 él mismo nos dice que a 1Mhz el address está estable. sí o sí, 300 nano segundos después de que comienza la fase uno y los datos deben estar estables al menos 100 nanosegundos antes de que termine la fase dos de nuestro ciclo de reloj. Esto nos da 575 ns para poner los datos en el bus de datos.

Y podemos observar los diagramas para timings de Read y Write respectivamente.

Read Timing Diagram

Write Timing Diagram

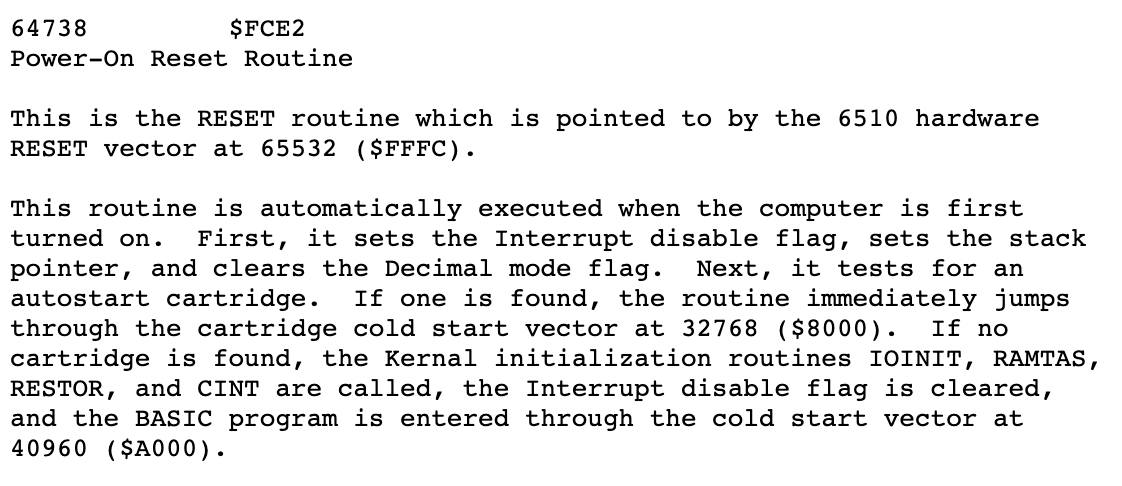

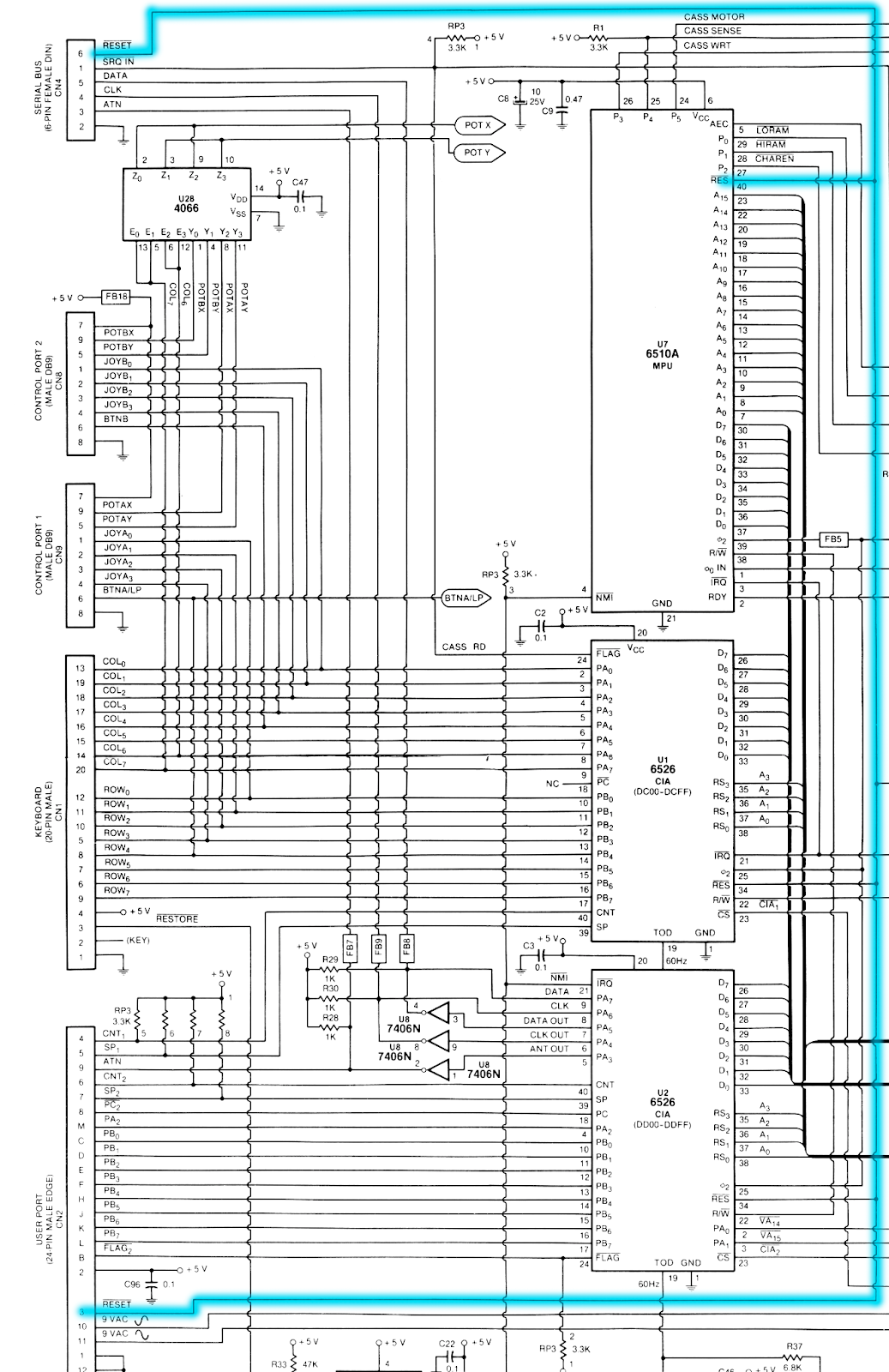

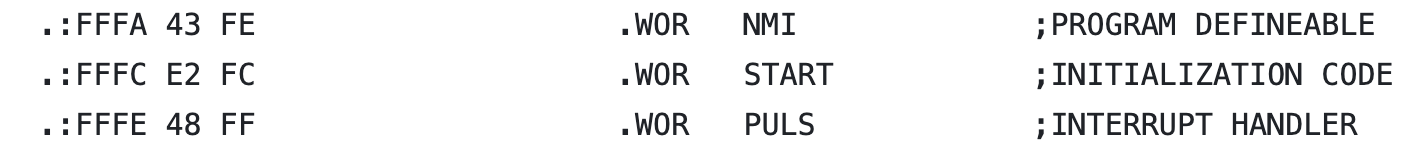

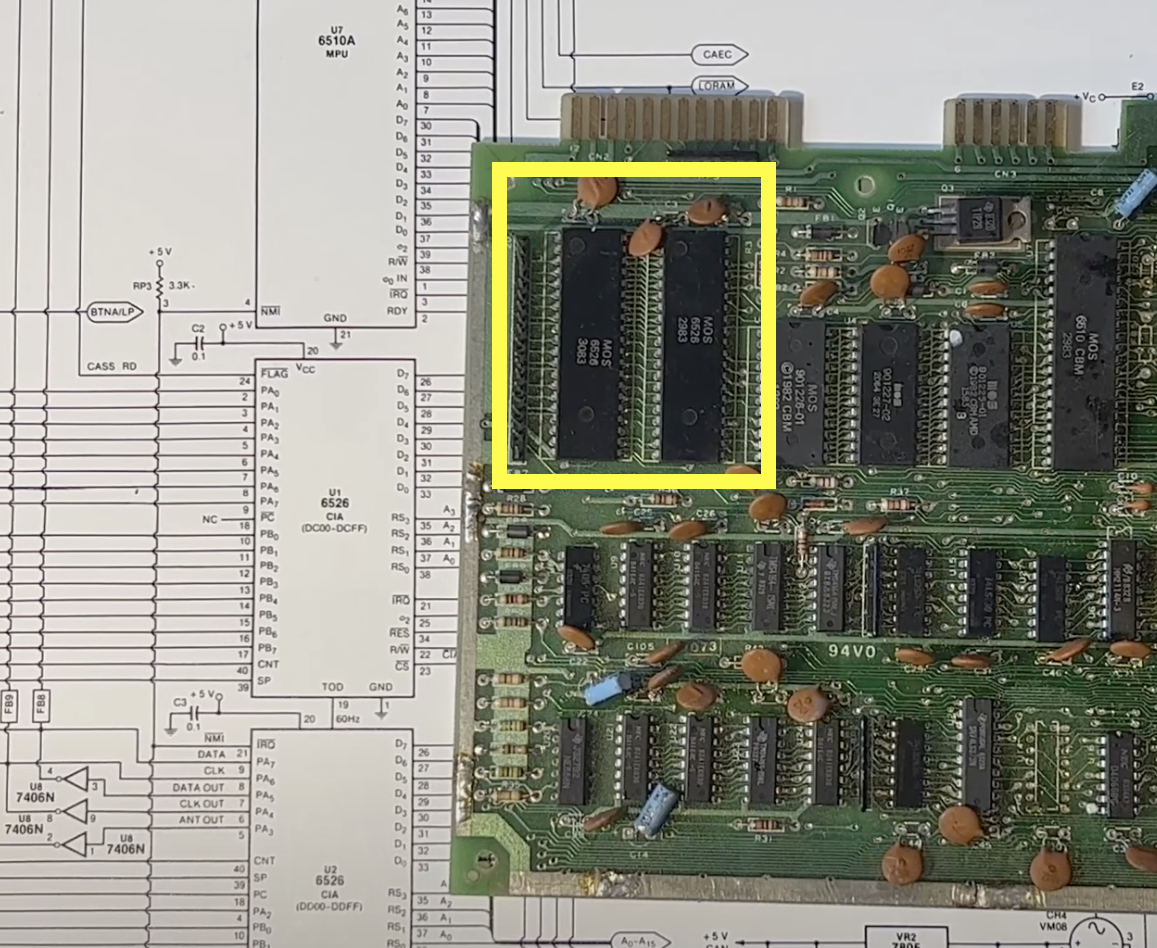

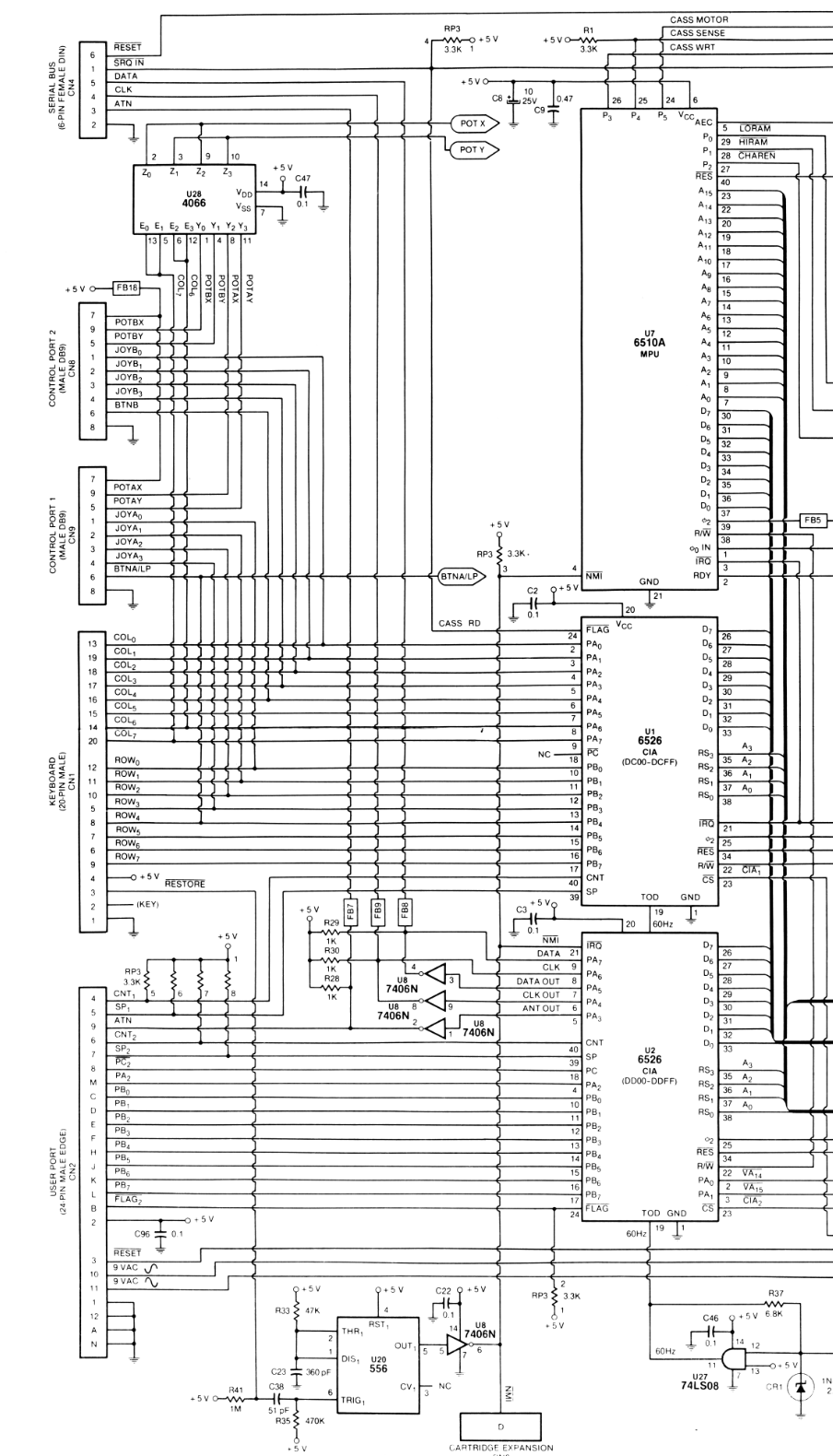

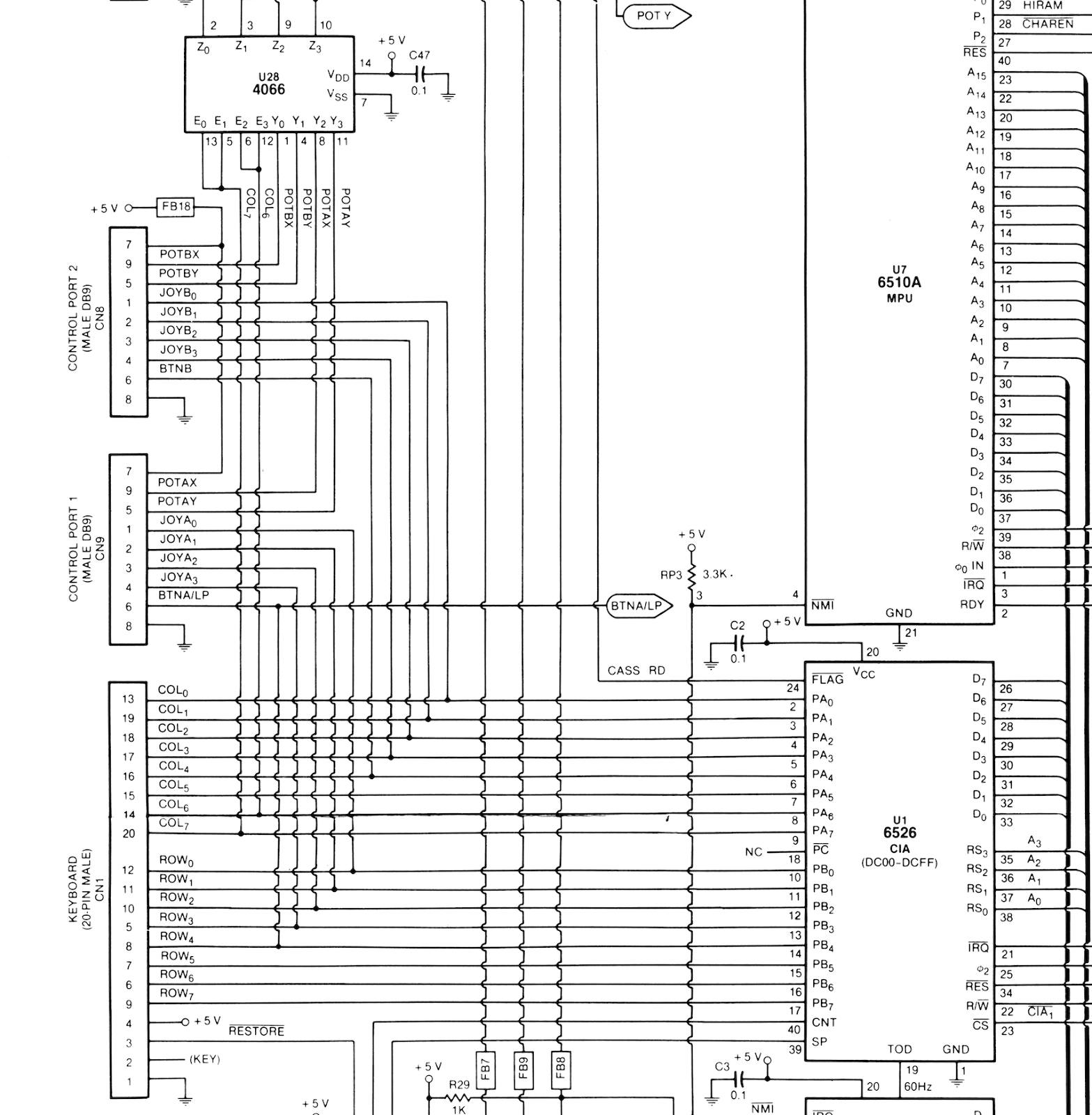

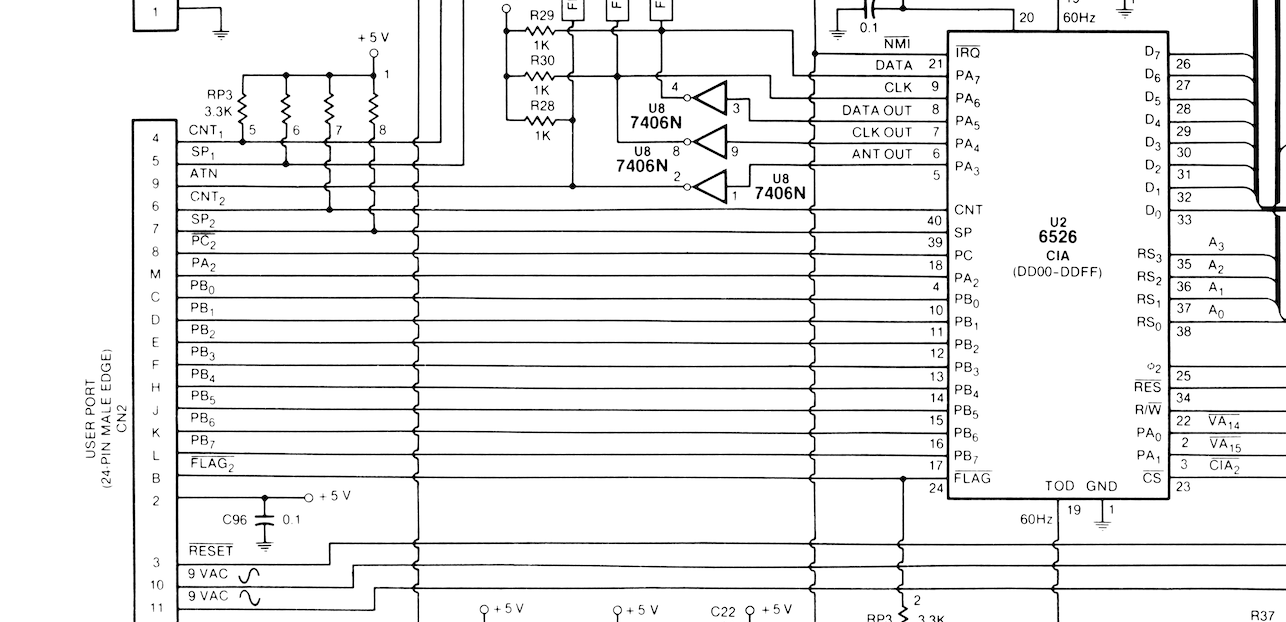

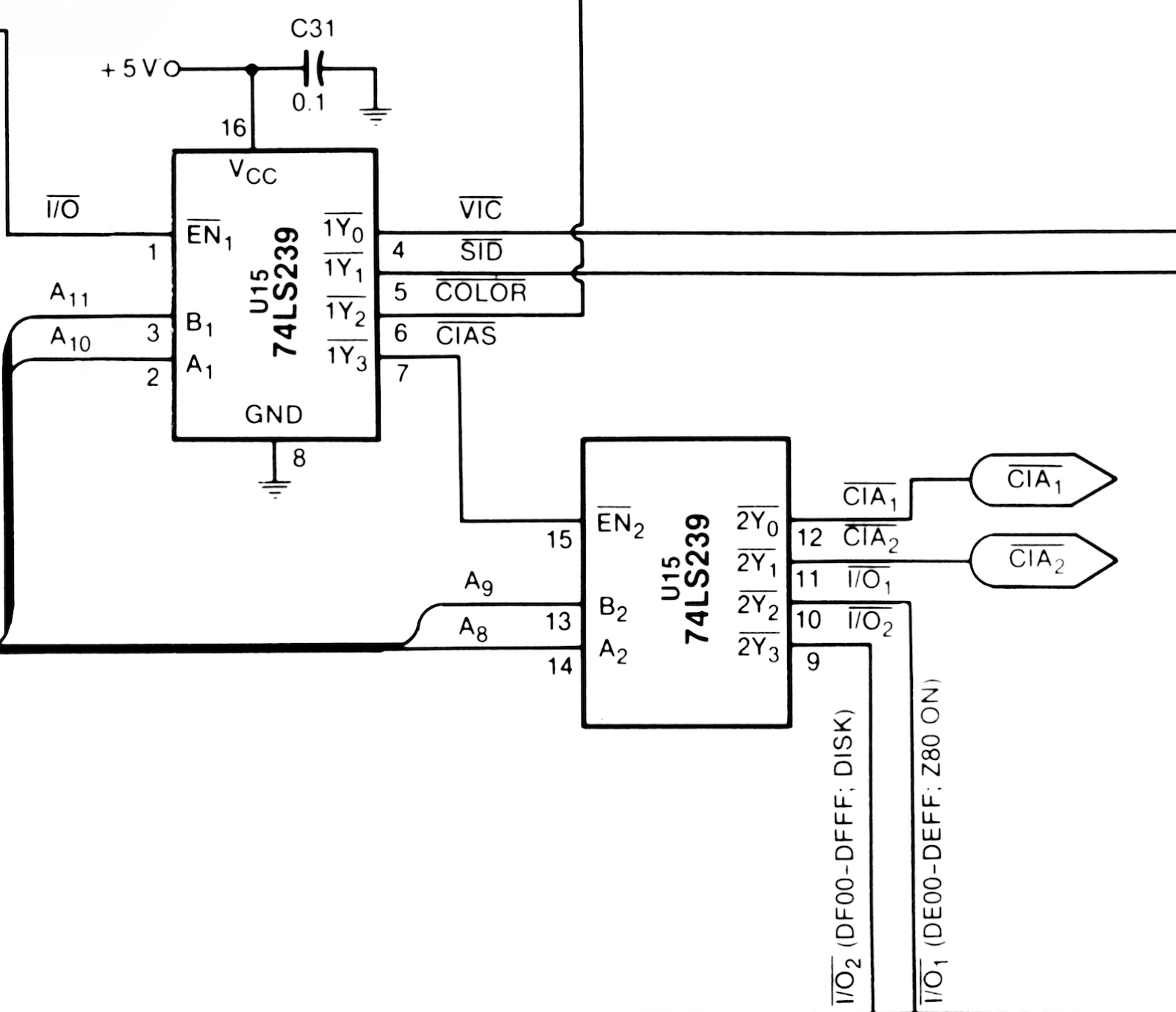

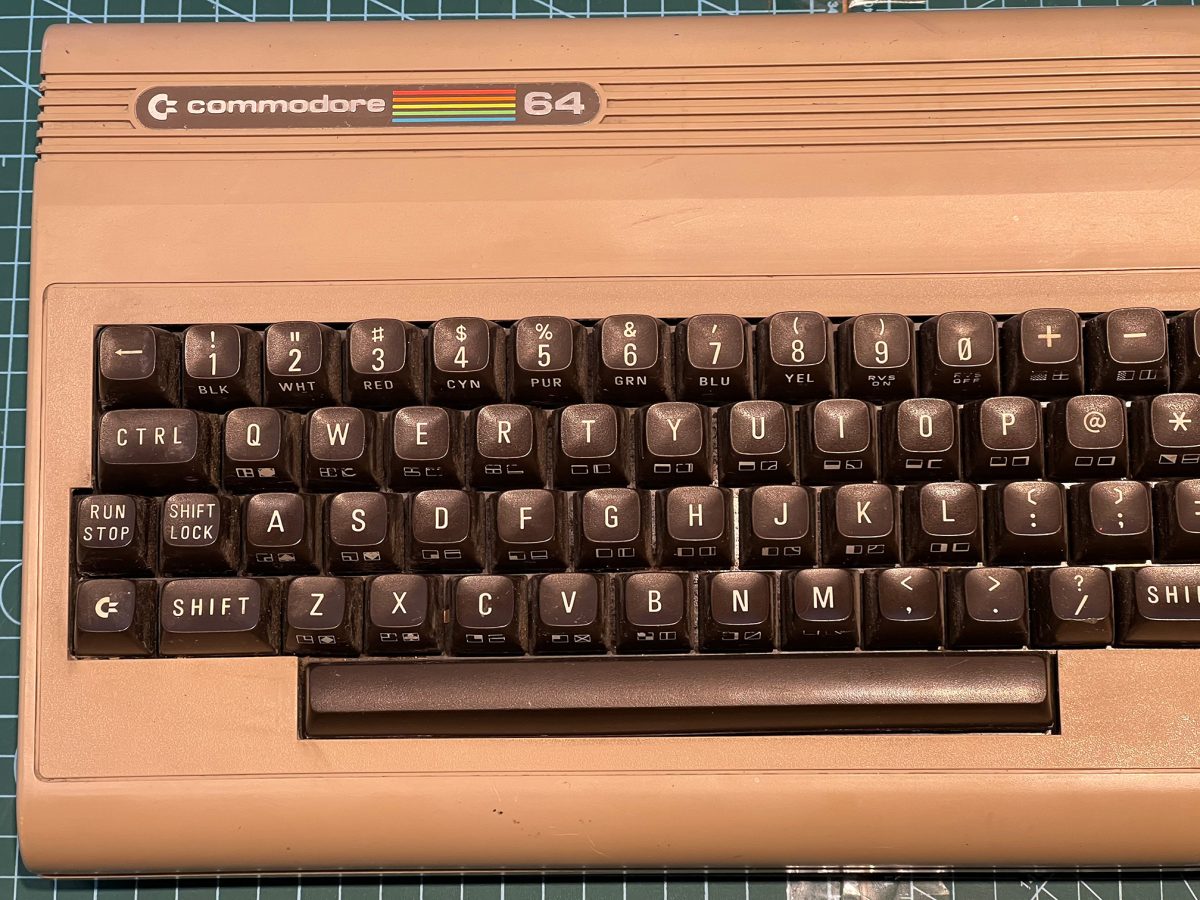

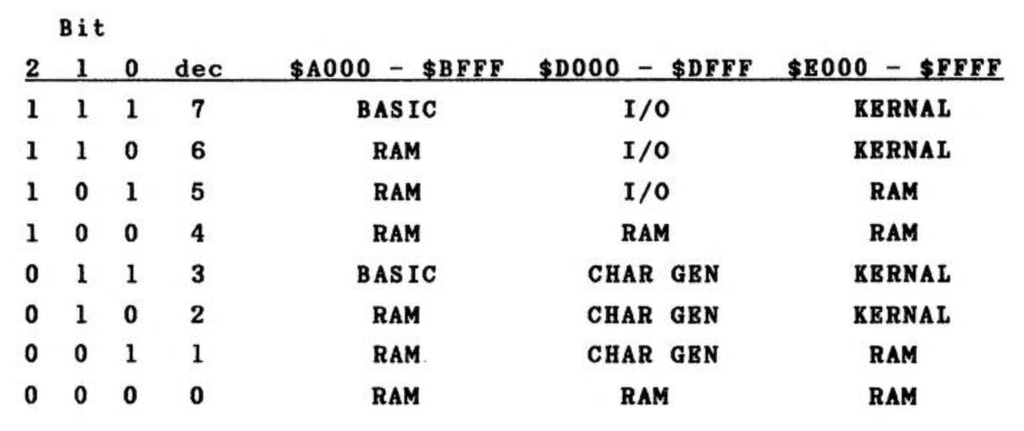

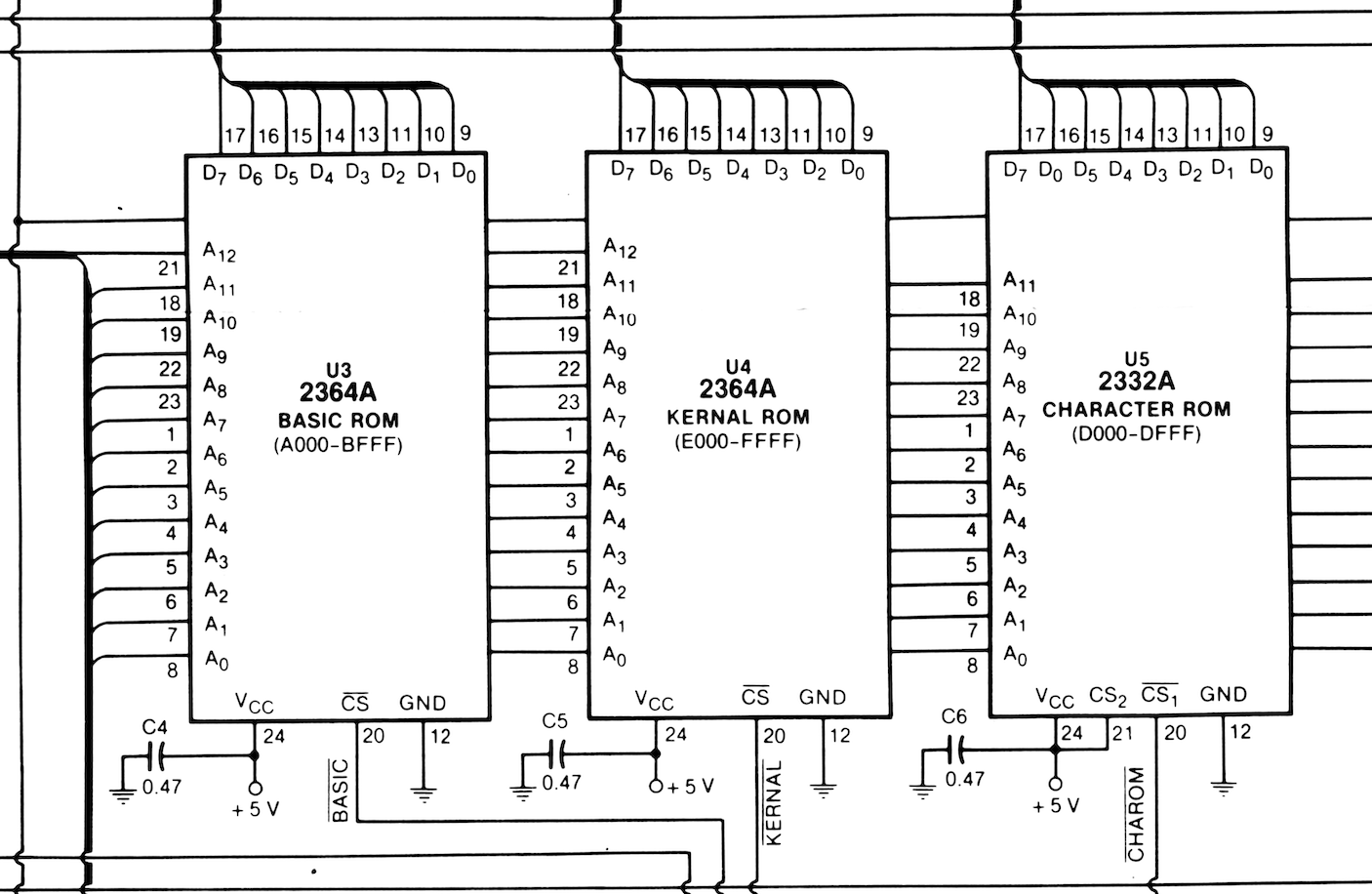

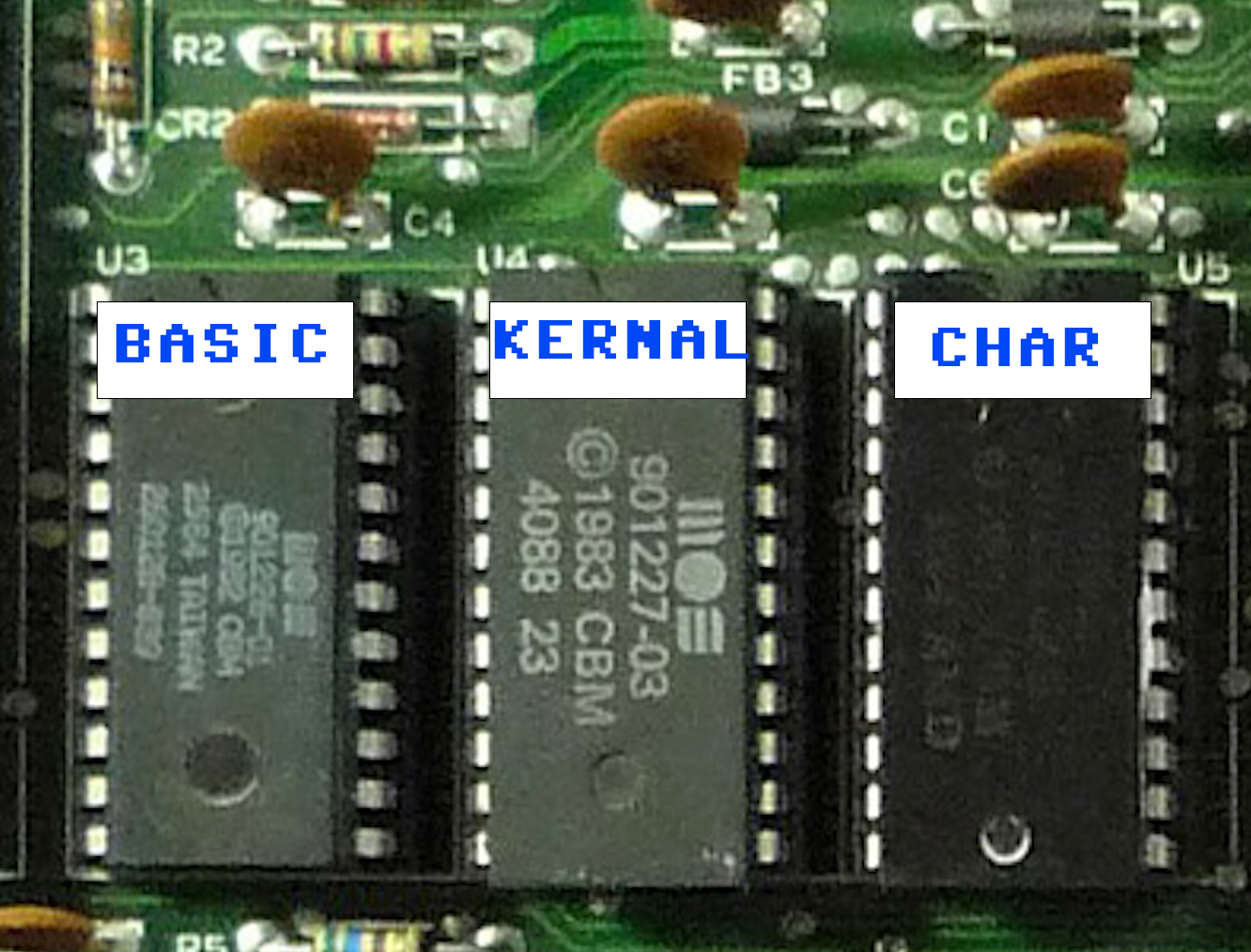

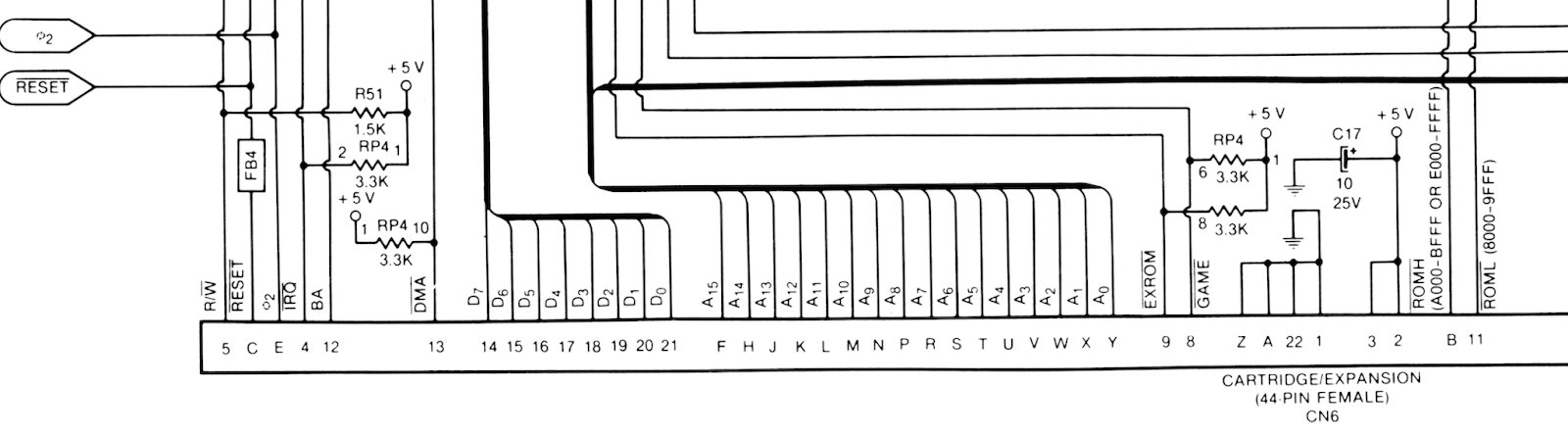

Cómo funciona en el Commodore 64

En nuestra querida Commodore 64 no estamos usando una memoria estática como la de este empleo si no que es dynamic ram, esta misma debe ser refrescada constantemente de lo que se encarga el chip de video VIC2. Esta memoria se selecciona por filas y columnas utilizando las señales de RAS y CAS.

Tampoco tenemos un sólo chip sino 8 chips cada uno de 64536 entradas y 1 bit de datos en cada entrada, con lo que si queremos representar un byte necesitamos los 8 chips y 1 bit de cada uno de ello, de ahí que cuando se rompe un chip de ram nada funciona ya que afecta al contenido de un bit en cada posición de la RAM.

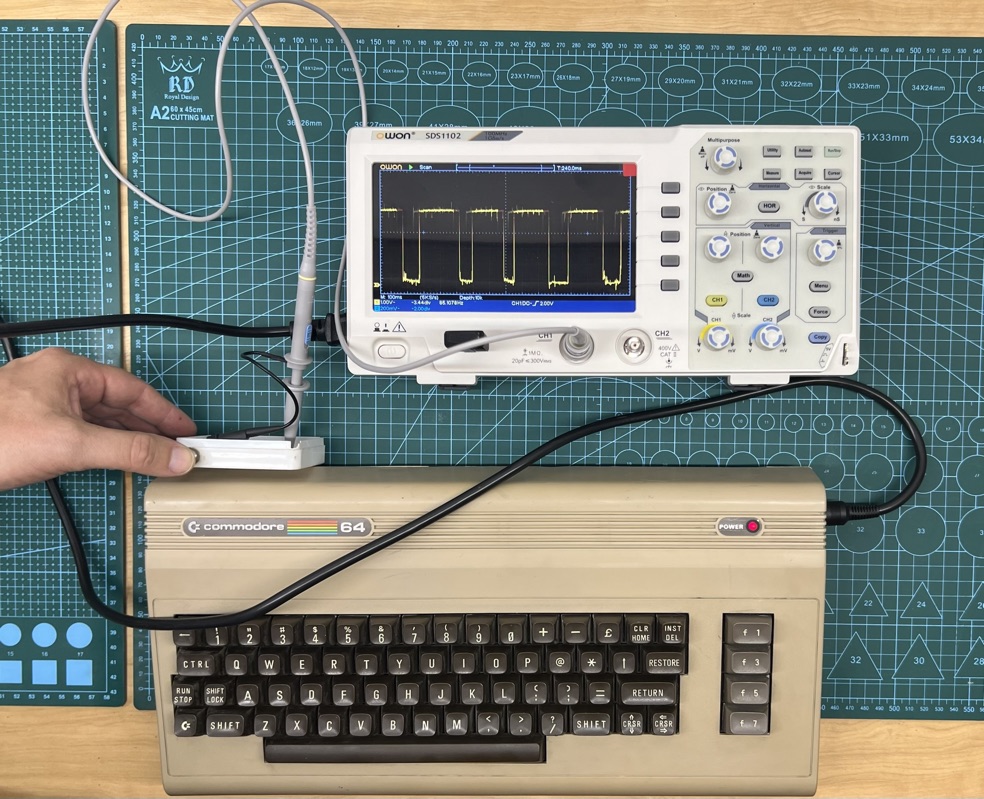

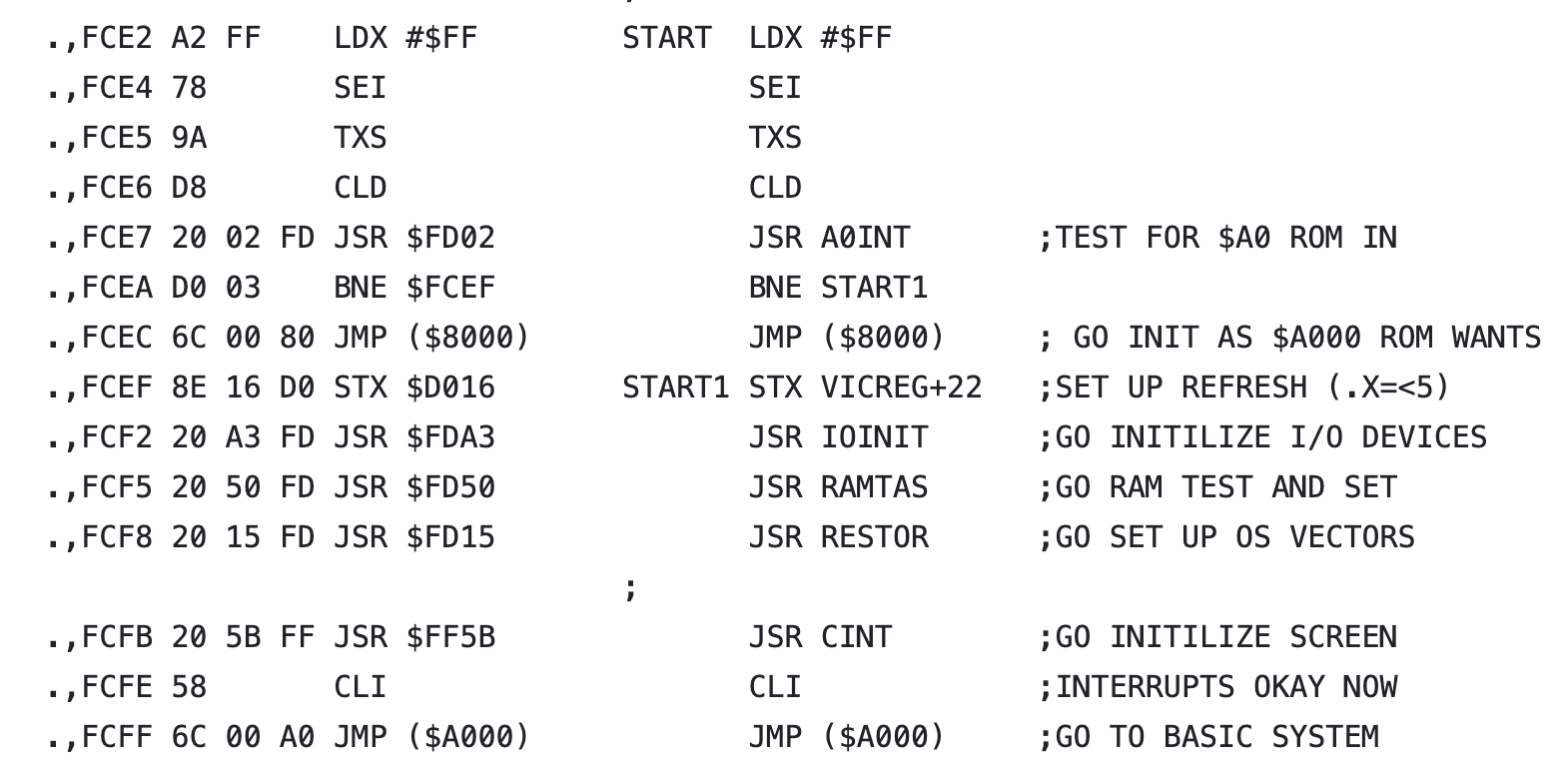

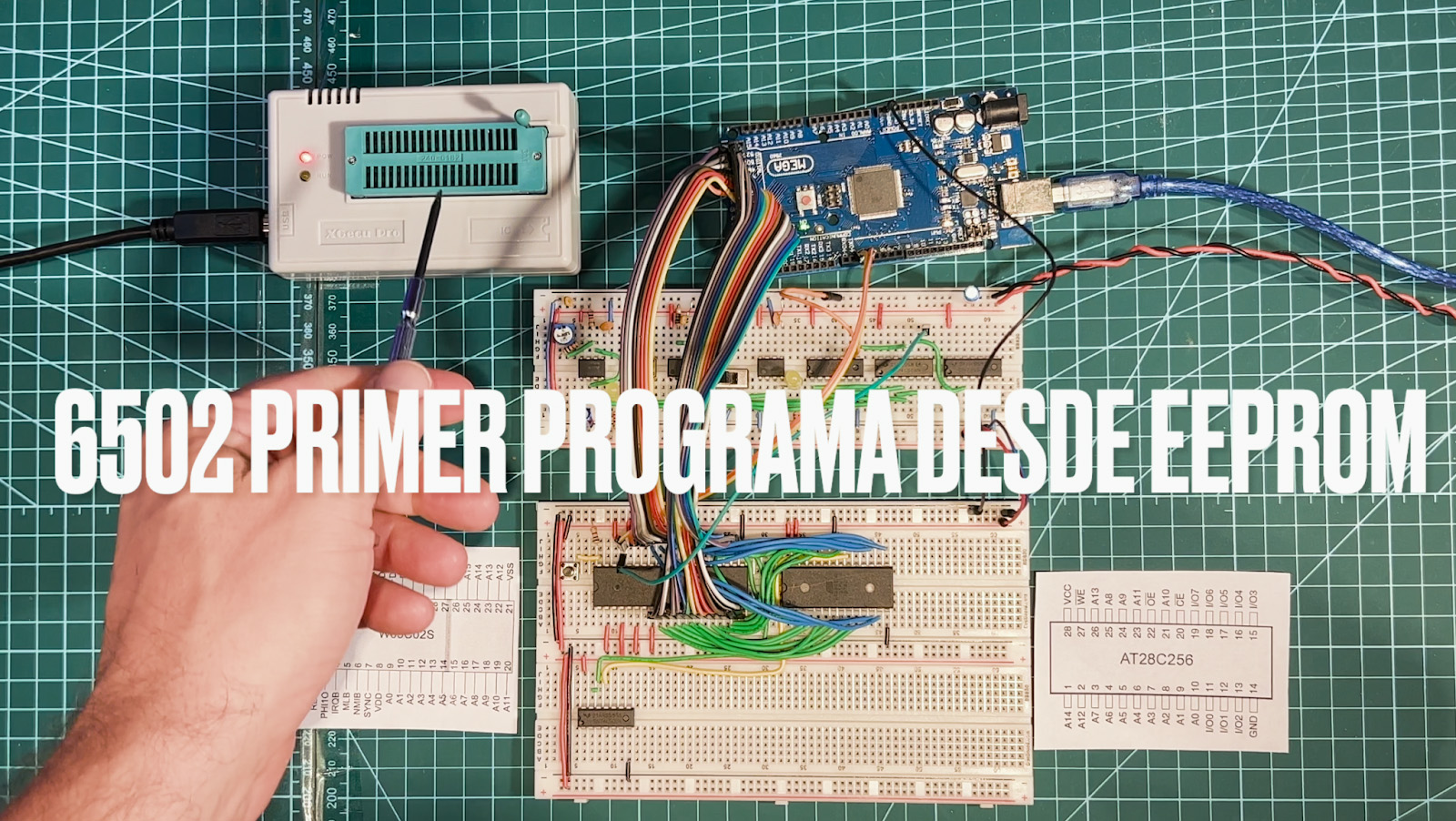

Estudio visual

Para poder estudiar visualmente cómo conectar una ram estática y programarla les dejo esta video que complementa al artículo.

RAM con 6510/CIA y 6502/VIA – 6502 vs 6510 Parte 10

Referencias

A continuación les dejo algunos links donde profundizar el tema:

VIDEOS

Video de la serie 6502 vs 6510 Parte 10 – RAM

RAM con 6510/CIA y 6502/VIA – 6502 vs 6510 Parte 10

Aquí tiene acceso a toda la serie:

6502 vs 6510 estudio detallado y comparación

PAPERS

Visual Guide to 65xx CPU Timing

MOS 6500 Family Hardware Manual

Y como siempre la serie de Ben Eater del 6502

Build a 6502 computer | Ben Eater

Todos los ejemplos de código de los videos los pueden encontrar en:

.

.

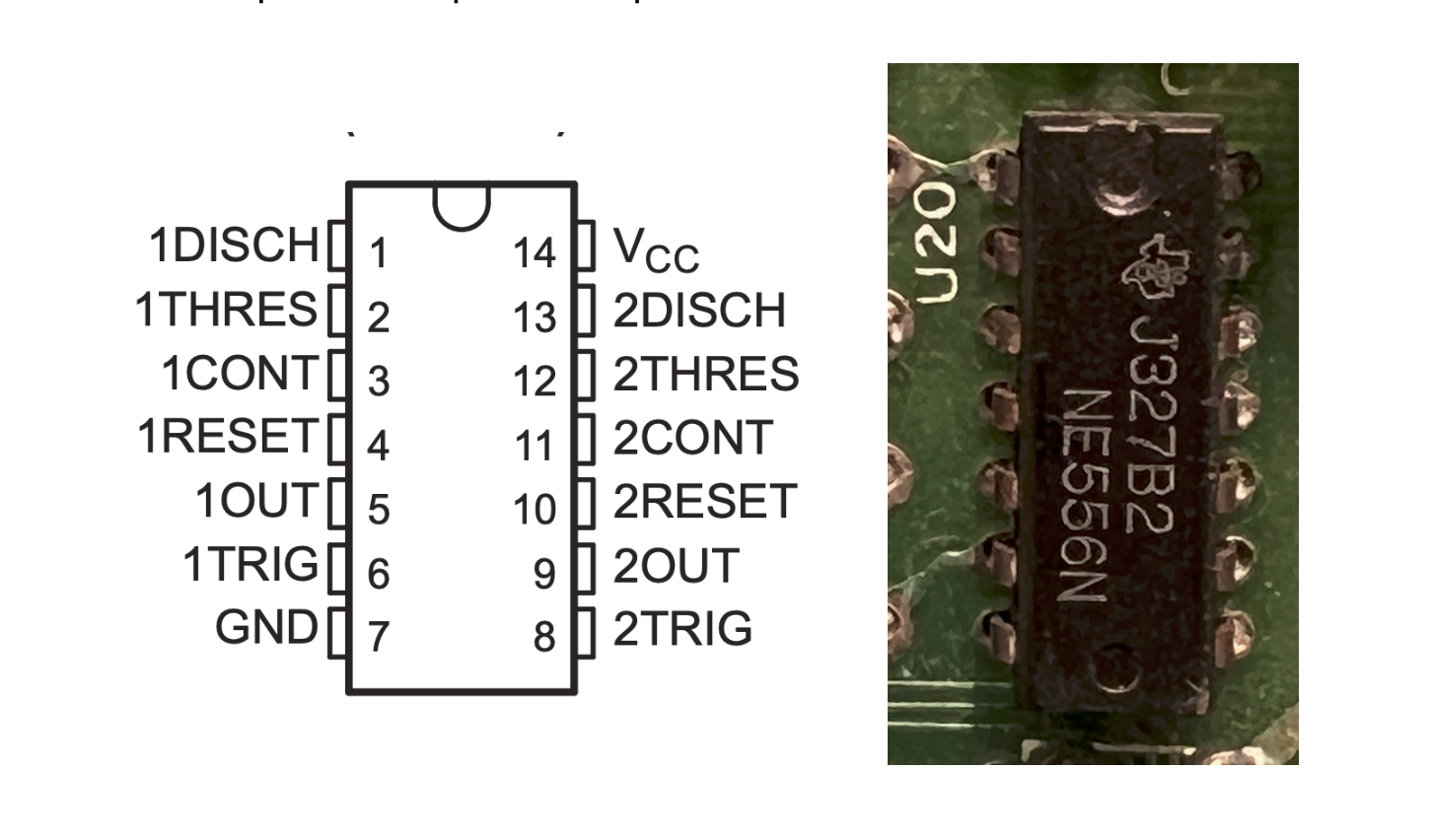

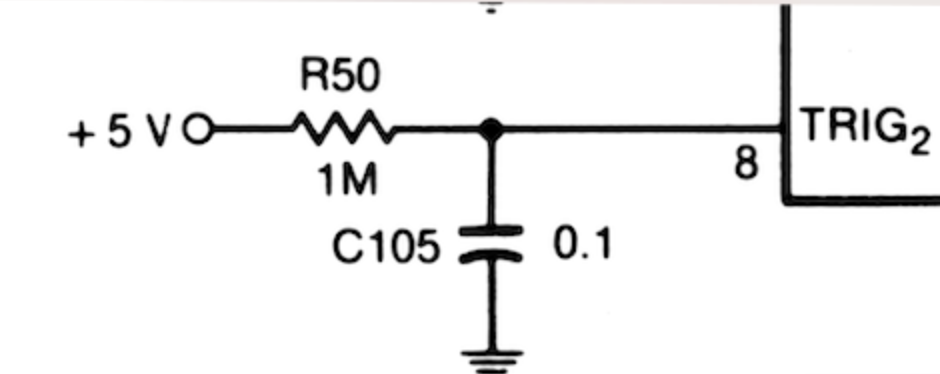

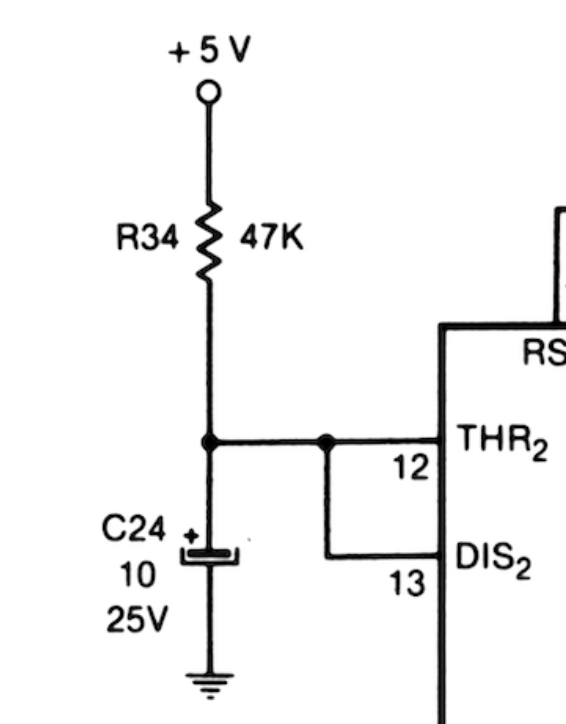

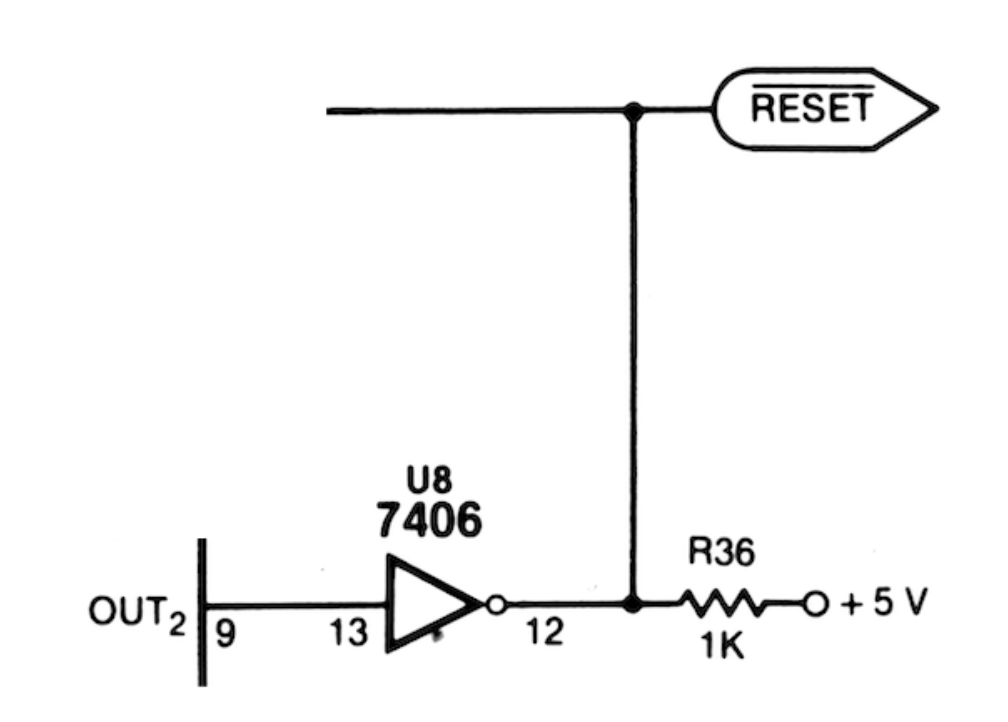

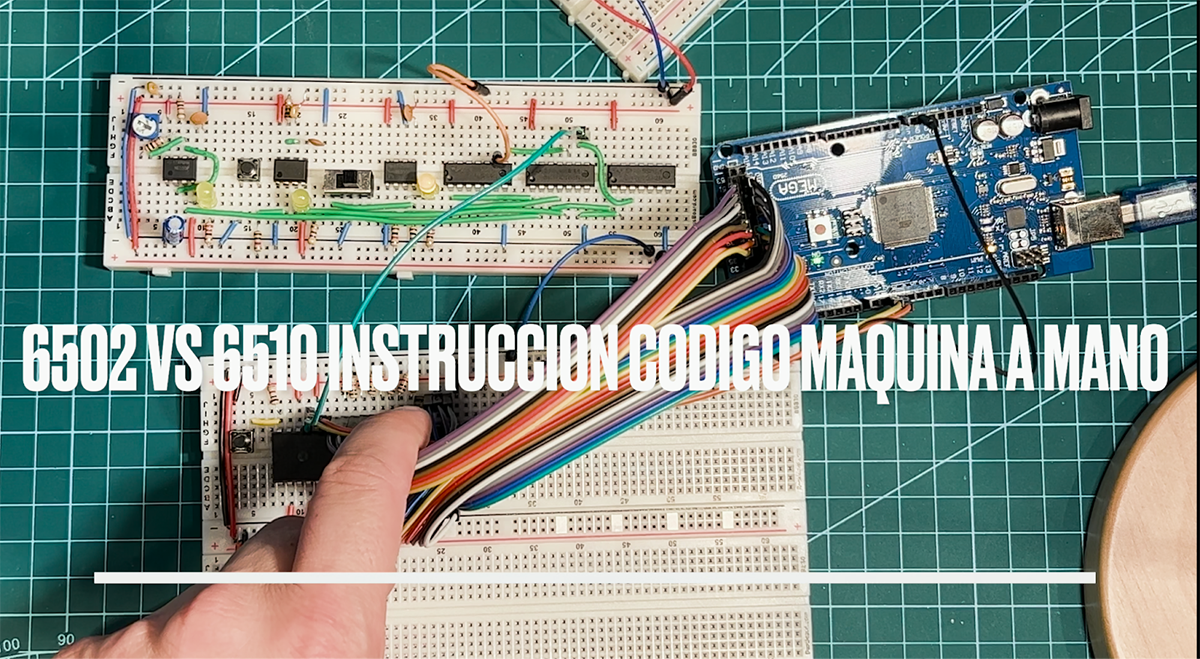

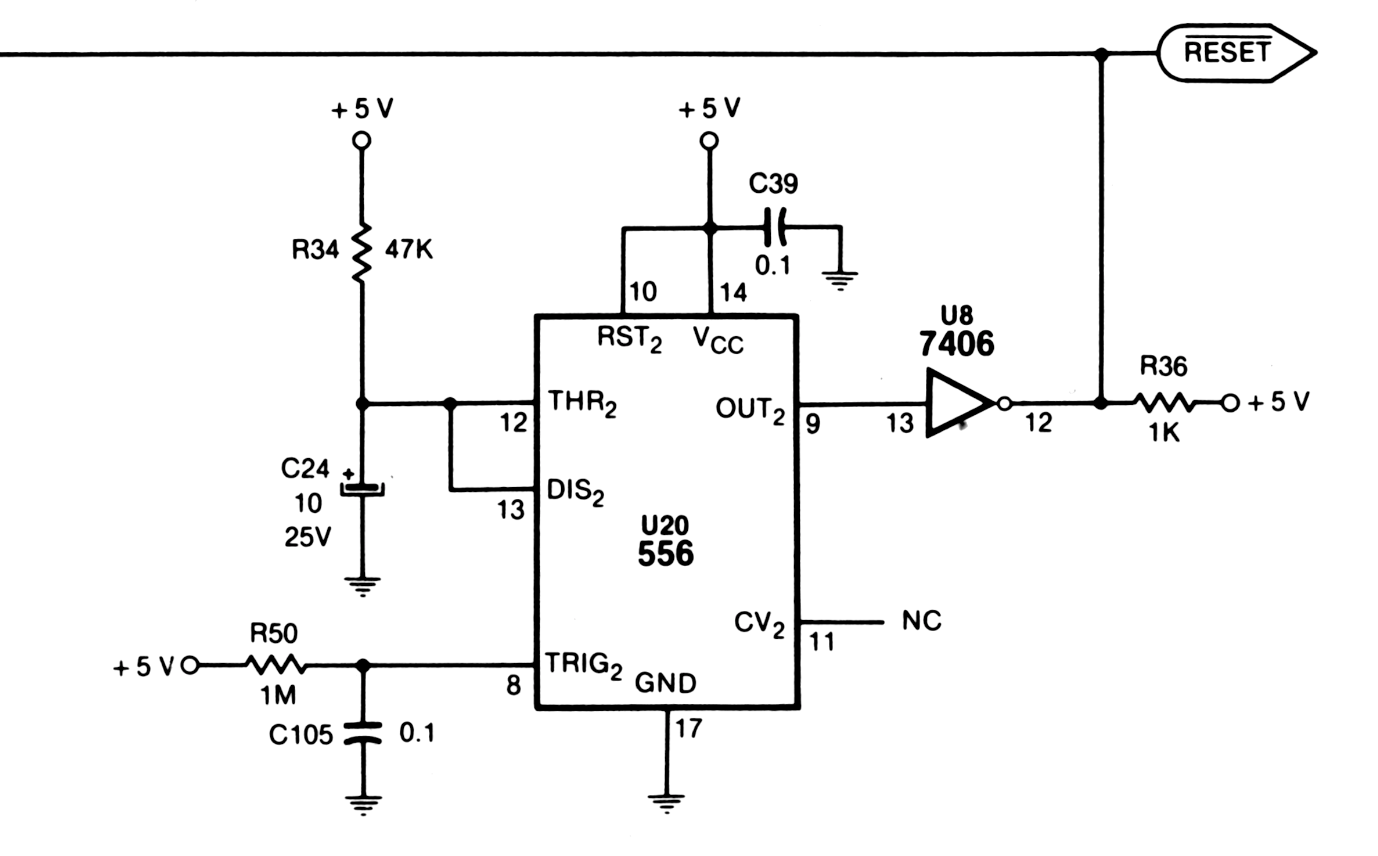

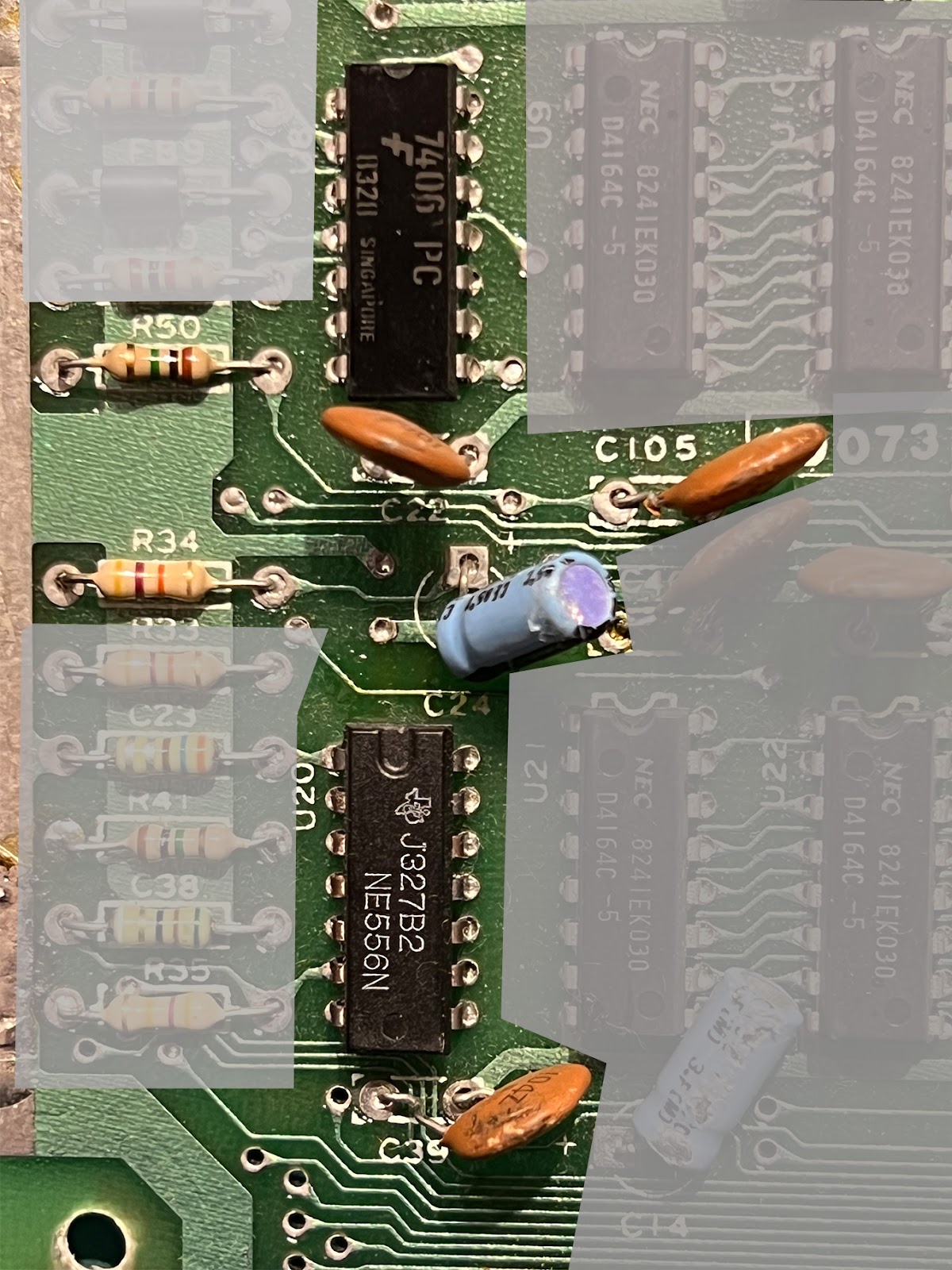

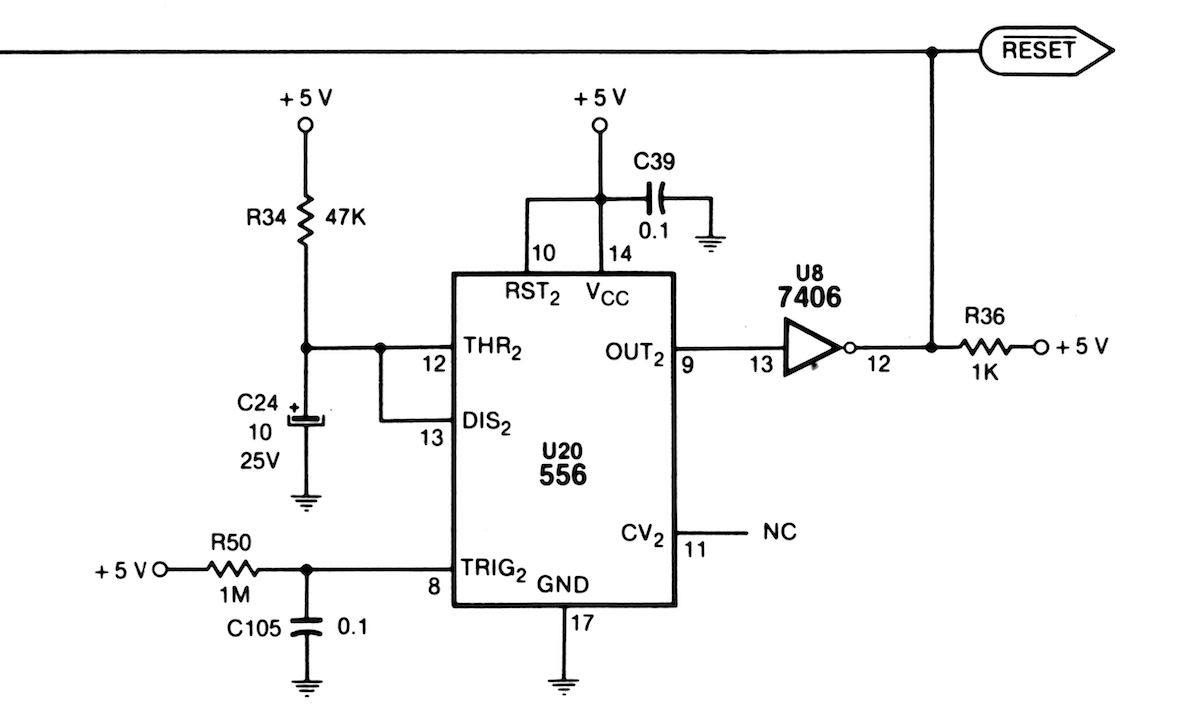

El 556 (componente U20) está cableado en forma monoestable lo que significa que por cada vez que es activado a través de su pin de trigger envía un pulso a través de su pin de output. Este circuito es activado solo al encender la computadora y después no vuelve a funcionar en la Commodore. Al ser dos timers 555 vamos a mirar la parte derecha del mismo, los pines con el número 2 que son los que forman parte del circuito de reset.

El 556 (componente U20) está cableado en forma monoestable lo que significa que por cada vez que es activado a través de su pin de trigger envía un pulso a través de su pin de output. Este circuito es activado solo al encender la computadora y después no vuelve a funcionar en la Commodore. Al ser dos timers 555 vamos a mirar la parte derecha del mismo, los pines con el número 2 que son los que forman parte del circuito de reset.